独立行政法人 産業技術総合研究所【理事長 中鉢 良治】(以下「産総研」という)ナノエレクトロニクス研究部門【研究部門長 金丸 正剛】青柳 昌宏 副研究部門長 兼 3D集積システムグループ 研究グループ長、同グループ 菊地 克弥 主任研究員は、株式会社 アリーナ【代表取締役社長 高山 慎也】(以下「アリーナ」という)と共同で、狭間隔部品実装技術を用いた高機能部品内蔵基板(部品内蔵インターポーザー)を開発した。

電子回路を低消費電力化するために電源電圧を低くすると、LSI上で発生する高周波電源ノイズにより誤動作が生じやすくなる。その対策として、電源回路にデカップリング・キャパシターを搭載して電源ネットワークのインピーダンスを広い周波数帯域で低い値に抑える方法により電子回路の安定動作が確保されている。しかし従来のインターポーザーでは、高い周波数帯域まで低インピーダンスにできず、他の方式であっても製造コストや製品信頼性の面で難があった。

今回、電源ネットワークの低インピーダンス化に向け、0.1 mmの狭い間隔で電子部品を実装する技術を用いて、キャパシターを従来よりも高密度で内部に実装した部品内蔵インターポーザーを開発した。このインターポーザーでは高周波数帯域まで電源ネットワークのインピーダンスを低減しているため、低消費電力で高機能な電子回路の実現への貢献が期待される。

この技術の概要は2013年10月31~11月1日に茨城県つくば市で開催される産総研オープンラボで、詳細は2013年12月12~14日に奈良県奈良市で開催される国際会議「2013 IEEE Electrical Design of Advanced Packaging & Systems Symposium」で発表される。

|

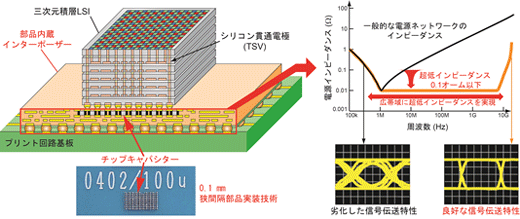

図 (左)今回開発した部品内蔵インターポーザー

(右)電源ネットワークのインピーダンスと信号伝送特性 |

情報ネットワーク社会の実現には携帯情報端末などの電子機器の高性能化が不可欠である。これまで、電子機器に使用されるLSIは、最小構成単位であるトランジスタを微細化することにより高性能化・高集積化してきた。しかし、次世代以降のトランジスタ技術では、寸法が小さいため素子間の特性ばらつきの問題が顕在化し、製品の歩留まりが著しく低下すると懸念されている。そのため、トランジスタの微細化によらないで、電子機器全体の処理性能を向上させることが必要であり、これに応える技術として三次元LSI積層集積化技術が注目を集めている。

また、医療機器、自動車、ロボット、産業機器、情報通信機器、情報家電などの幅広い産業で電子機器が使用され、総エネルギー消費量のうち電子機器が占める割合が年々増加している。そのため省エネルギーへの取り組みが優先度の高い課題となっている。電子回路の消費電力を削減するには電源電圧をより低くする必要があるが、電源ノイズの許容量も小さくなるため、電源ネットワークを高周波帯域まで超低インピーダンス化し、電源ノイズの発生を抑制することができる高性能インターポーザーが求められている。

産総研では、三次元LSI積層集積化技術の研究開発を進めており、超高速伝送・超高密度実装を実現するLSI接続インターポーザーの開発などに取り組んできた。さらに、2007年度から独立行政法人 新エネルギー・産業技術総合開発機構のITイノベーションプログラム「立体構造新機能集積回路(ドリームチップ)技術開発」において、電子実装分野の研究開発を進めている。また、電源ネットワークを高精度に測定・評価できる超広帯域・超低インピーダンス電子回路評価システムを開発している(2010年5月25日 産総研プレス発表)。

アリーナでは、0.1 ㎜という狭い間隔で電子部品を実装する技術を保有しているが、その技術を高度化し、部品内蔵基板技術に応用展開して、従来の部品内蔵基板より大幅に優れた、高密度で高性能な実装モジュールを製造する技術の開発に取り組んできた。

今回、両者の技術を融合させて高性能部品内蔵インターポーザーの開発に取り込んだ。

なお、この研究開発は、経済産業省 中小企業庁の平成23年度戦略的基盤技術高度化支援事業(平成23年度第3次補正予算事業)「部品内蔵基板内の狭間隔部品実装技術及びWLP-LSIチップ実装技術の確立」による支援を受けて行った。

低消費電力で高速動作するLSIを実装するインターポーザーでは、電源ネットワークを高周波帯域まで超低インピーダンス化し、電源ノイズの発生を抑制することができるデカップリング・キャパシターを内蔵するなどの高機能化が求められている。電源ネットワークのインピーダンスは供給電圧と供給電流、最大リップル電圧の許容値から想定される値以下にする必要があるが、三次元積層集積LSIでは、10 Gbps以上の高速信号伝送に対応するため、部品内蔵インターポーザーを含めた電源ネットワークのインピーダンスを、直流(0 Hz)から10 GHz以上の広い周波数帯域で、0.1 Ω以下にすることが求められている。この低いインピーダンスを実現するため、インターポーザーに従来以上の高密度でキャパシターを実装する必要がある。

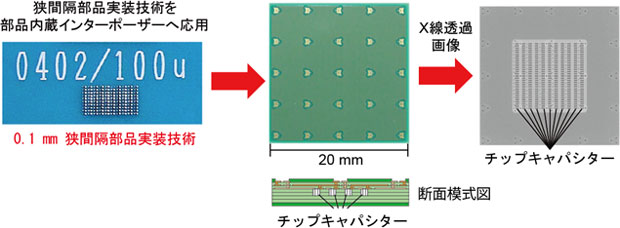

今回、アリーナの保有する0.1 ㎜間隔の狭間隔部品実装技術を、インターポーザー内層部に応用して0402サイズのキャパシターを高密度に実装し、超広周波数帯域で超低インピーダンスの電源ネットワークをもつ高機能な部品内蔵インターポーザーを開発した(図1)。

|

|

図1 狭間隔部品実装技術による部品内蔵インターポーザー |

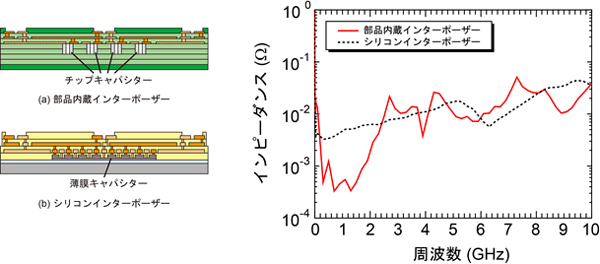

電源ネットワークを低インピーダンス化する技術として、部品内蔵インターポーザーのほかに、薄膜キャパシター内蔵方式によるシリコンインターポーザーがある。シリコンインターポーザーは、シリコンウエハーをベースとして、LSIの製造プロセスを適用して作製され、その内層に薄膜キャパシターが形成されている(図2左b)。通常のインターポーザーよりデバイスとキャパシターの距離が短くなるため、電源ネットワークのインピーダンスを低く抑制できる。しかし、シリコンインターポーザーはLSIの製造プロセスを用いるため非常に製造コストが高く、また、キャパシターの静電容量を大きくするには誘電体を超薄化する必要があり、絶縁不良の発生を抑えるのが困難である。

|

|

図2 (左)部品内蔵インターポーザーとシリコンインターポーザーの模式図と(右)電源ネットワークのインピーダンスの周波数依存性 |

産総研の保有する評価システムを用いて、今回開発した部品内蔵インターポーザーとシリコンインターポーザーについて、0 Hzから10 GHzの広い周波数帯域の電源ネットワークのインピーダンスを測定した。図2右のように、今回開発した部品内蔵インターポーザーは、シリコンインターポーザーと同様に電源ネットワークが大幅に低いインピーダンスになり、製造コストや製品信頼性の観点から、シリコンインターポーザーに対して十分な競争力を持つと考えられる。

以上より、狭間隔部品実装技術による部品内蔵インターポーザーを幅広く電子機器に用いることによって、実装配線の短縮、部品点数の削減、回路の簡略化などの改善効果により、機器自体の省電力化、省資源化が促進される。また、スマートフォンなどの登場で顕在化している、携帯電子機器の電池寿命不足に対して、省電力化による改善が期待できる。部品内蔵インターポーザーの普及により、電子機器の高機能化、小型化を推進できるため、高度ユビキタス情報化社会の実現に大きく寄与すると考えられる。

今後は、携帯端末機器メーカーや高性能半導体メーカーといった川下企業との連携を進め、高密度な部品内蔵インターポーザーを用いたプロトタイプ機の開発を行い、実用レベルの応用技術開発を推し進める予定である。