独立行政法人 産業技術総合研究所【理事長 野間口 有】(以下「産総研」という)、技術研究組合 超先端電子技術開発機構【理事長 秋草 直之】(以下「ASET」という)、学校法人 明星学苑 明星大学【学長 小川 哲生】、学校法人 芝浦工業大学【学長 柘植 綾夫】は共同で、将来の超低消費電力化された電子回路における電源ネットワークを高精度に測定・評価できる超広帯域・超低インピーダンス電子回路の評価技術の確立に成功した。

電子回路を低消費電力化するためには、電源電圧を低くすることが有効であるが、電源電圧を低くするとLSI上の多数のトランジスタが高速にスイッチングする際、急激な電流変化により電源電圧降下が起こり、これによって発生する高周波電源ノイズによる電子回路の誤動作が重大な問題になると予想されている。電源ネットワークを広い周波数範囲で低インピーダンスにすれば、電源ノイズ伝達を抑制できるので、高速な電子回路の安定動作が可能となる。しかし、従来の電源評価方法では、複数の計測機器を使用し煩雑な測定操作が必要なうえ、その方法でも超広帯域でかつ超低インピーダンスの評価には十分ではなかった。今回10 Hzから40 GHzまでの超広帯域な周波数領域にて、0.001 Ωの超低インピーダンス評価技術を確立し、薄膜キャパシターを付与したインターポーザーの電源ネットワークの超低インピーダンスの評価に成功したことにより、将来の低消費電力かつ高機能な電子回路の開発に貢献できると期待される。

本技術の詳細は、2010年6月1~4日に米国ラスベガス市で開催される国際会議「第60回電子部品技術会議」(60th Electronic Components and Technology Conference)で発表される。

|

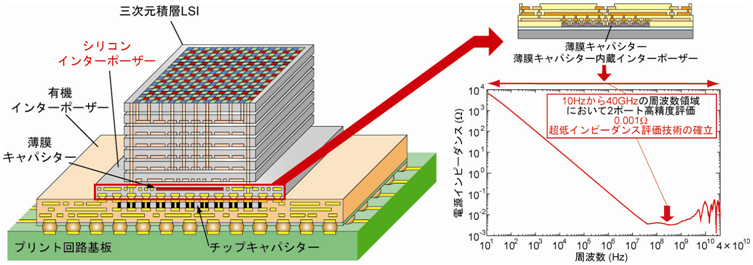

図1 高機能三次元LSI積層集積化技術と電源ネットワークインピーダンス |

情報ネットワーク社会の実現には携帯情報端末等の電子情報機器の高性能化が不可欠である。しかし、近年、機器に使用されるシリコン半導体LSIデバイスやその周辺回路の動作速度は、動画コンテンツのような情報処理量増大の要求に応えることが困難となってきている。これまでは、シリコン半導体LSIチップの最小構成単位であるトランジスタを微細化することによりLSIを高性能化・高集積化してきた。しかし、次世代の22 nm世代トランジスタ技術では、その寸法の小ささから、素子間の特性ばらつきの問題が大きく顕在化してくると考えられており、製品の著しい歩留まり低下が懸念されている。そのため、電子機器全体の処理性能を、トランジスタの微細化によらないで向上させることが必要であり、これに応える技術として三次元LSI積層集積化技術が注目を集めている。

また、近年、電子情報機器による消費電力量が増大し、座視できない状況となりつつある。このため、低消費電力で高性能な電子回路の実現が強く望まれるようになってきている。

世界中でさまざまな企業、大学、研究機関などが、これらの技術開発への取り組みを強化しており、日本でも、研究・技術開発が活発化してきている。

産総研では、三次元LSI積層集積化技術の研究開発において、超高速信号伝送による高機能化を目指しており、超高速伝送・超高密度実装を実現するLSIチップ接続インターポーザーの開発など、信号品質評価技術の開発に取り組んできた。さらに、2007年度から独立行政法人 新エネルギー・産業技術総合開発機構のITイノベーションプログラム「立体構造新機能集積回路(ドリームチップ)技術開発」において、ASETが、産総研、明星大学、芝浦工業大学と多機能高密度三次元集積化技術についての共同実施研究体制を組織して、電子実装分野の研究開発を進めてきている。特に、ASETと産総研の緊密な連携による実験設備、機材の共同利用、共同実験、情報交換などを通じて、成果を着実に上げてきている。

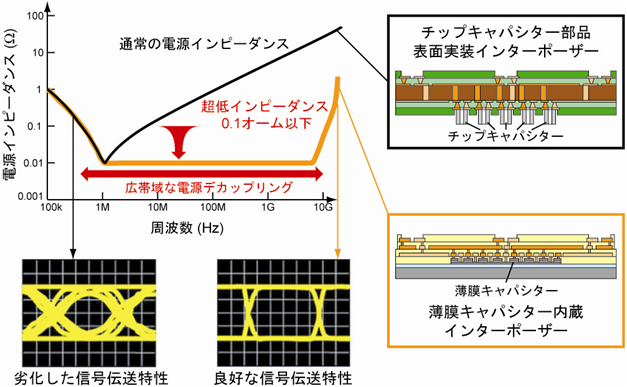

将来の低消費電力で高性能な電子回路を実現するためには、電源電圧をさらに低くすることで消費電力を削減する必要がある。このとき、三次元集積LSIシステムのように、膨大な数のトランジスタからなるデバイスでは、これらのトランジスタが高速かつ同時にスイッチングする際に発生する急激な電流変化が、瞬間的に電源電圧の低下を引き起こし、電源ネットワークに高周波電源ノイズを発生させるため、高速なトランジスタの動作が阻害され、信号伝送の劣化が生じる。特に、これからの低消費電力デバイスの電源電圧はさらに小さくなり、電圧の揺らぎの許容量もさらに小さくなることが予想される。このため、低消費電力かつ高速信号処理に対応する高性能な回路システムを実装するインターポーザーでは、電源ネットワークを高周波領域まで超低インピーダンス化し、電源ノイズの伝達を抑制することができるデカップリング・キャパシター(図1の薄膜キャパシターやチップキャパシター)を内蔵するなどの高機能化が求められている(図1)。電源ネットワークのインピーダンスは供給電圧と供給電流および最大リップル電圧の許容値から想定される値以下にする必要があり、特に三次元集積LSIシステムでは、10 Gbps以上の高速信号伝送に対応するため、キャパシター内蔵インターポーザーを含めた電源ネットワークについて、直流(0 Hz)から10 GHz以上の周波数領域に至る広帯域で、0.1 Ω以下の低インピーダンスとする必要があると予測される(図2)。

|

図2 デカップリング・キャパシター搭載インターポーザーによる電源インピーダンスとその信号特性

|

従来、キャパシターの容量や設置場所が電源ネットワークのインピーダンスに与える影響について、経験的な知見および電磁界シミュレーションによる解析・設計を行い、電圧の揺らぎや信号伝送の劣化を予測して、デカップリング・キャパシターの効果を評価していた。近年、電源ネットワークのインピーダンスを直接評価する方法として、インピーダンスアナライザーを利用する方法の研究が行われてきた。しかし、このような広帯域において、低インピーダンス値を評価するには、従来のインピーダンスアナライザーでは、周波数範囲やインピーダンス値の範囲により複数の測定装置を使い分け、その測定評価ごとにシステムの校正が必要なため、測定が非常に煩雑で時間のかかる工程となっていた。また、通常、周波数領域によって測定手法が異なるので、得られたデータの連続性にも課題があった。

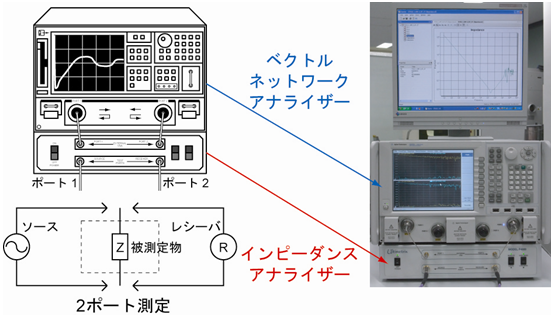

そのため本研究開発では、同一の2ポート測定法で測定が可能な、低周波領域と高周波領域に対応した2種類のインピーダンスアナライザーを用いたシステムを開発した。低周波領域の測定用にインピーダンスアナライザーを、高周波領域の測定にはベクトルネットワークアナライザーを用い、高周波同軸切り替えスイッチを用いて、2台の測定装置を統合して1つのシステムとして機能させた。このシステムは、従来の測定装置の組み合わせでは実現できないような、1回の測定で10 Hzから40 GHzに至る超広周波数帯域をシームレスに測定できる。さらに、2台の装置の動作ノイズを極力抑制することで、測定可能な下限のインピーダンス値としても現在の最高性能を達成している(図3)。また、本評価システムでは、システムの測定端子に高周波プローブを用いることで、LSIチップを接続する端子で直接電源ネットワークインピーダンスの測定を行うことができ、LSIチップへ影響する電源インピーダンスの精密な評価を可能としている。

|

図3 超広帯域・超低インピーダンス評価システム |

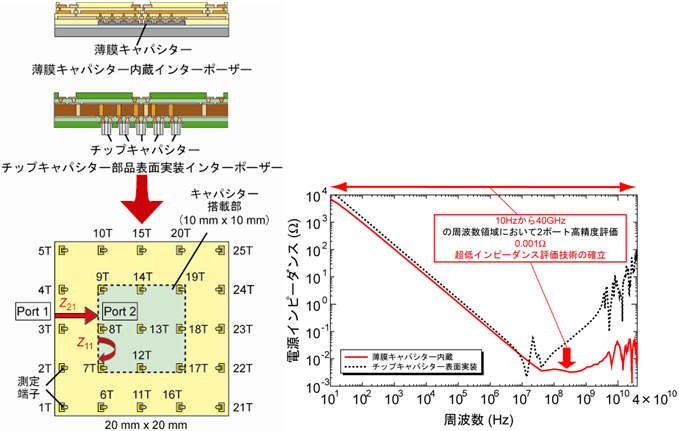

今回開発した評価システムの適用例として、薄膜キャパシター内蔵インターポーザー、比較のためにチップキャパシターが表面実装されたインターポーザーの2種類について、電源ネットワーク中におけるキャパシターの挿入位置による、低インピーダンス特性の違いを比較評価した。図4左に、デカップリング・キャパシターとして薄膜キャパシターを内蔵したインターポーザーとチップキャパシター部品表面実装インターポーザーを示す。中央の10 mm角の領域にLSIチップを接続することを想定したインターポーザーとなっている。図3に示す2ポート測定法により、インターポーザー(図4左)の端子3Tから端子8Tへの透過インピーダンスを評価した。図4右に示すように、今回開発した超低インピーダンス測定システムによって、10 Hzから 40 GHzまでの広帯域において、シームレスな透過インピーダンスの測定が可能となった。従来のインピーダンスアナライザーでは1ポート測定法(端子8Tによる測定)であるため、LSIチップの電源端子からみえる電源ネットワークの反射インピーダンスだけしか評価できず、電源供給部分からLSIチップの電源端子までの、透過インピーダンスを測定することは不可能である。また、従来はインピーダンスの最低測定範囲が0.01~0.1 Ω程度であったが、図4右に示すように本システムでは0.001 Ω程度にまで拡大している。この比較評価により、LSIチップの接続端子からデカップリング・キャパシター搭載位置までの距離が短い薄膜キャパシター内蔵インターポーザーの方が、電源インピーダンスが小さくなることがわかった。

|

図4 デカップリング・キャパシター搭載インターポーザーの模式図(左)と

評価システムによる電源インピーダンスの周波数依存性測定結果(右)

|

今回開発した評価システムにより、実用的な電源ネットワークをもつ薄膜キャパシター内蔵インターポーザーのような、高性能インターポーザーの高精度な電源インピーダンス評価が可能となった。特に従来、電源ネットワークの広帯域インピーダンスについては、電磁界シミュレーション解析で予測することが行われていたが、本評価システムによる高精度な実測から、シミュレーション解析と実測値を高い精度で比較検証できると考えられる。

今回開発した超広帯域・超低インピーダンス評価システムは、電子回路の電源ネットワークのインピーダンス評価技術として幅広く適用できるので、三次元LSI積層集積技術による電子回路だけでなく、さまざまな高性能電子回路についての電源ネットワーク評価ができる。本システムを活用し、民間企業、大学などと連携することで、高性能コンピューター、携帯電子機器、情報家電など、低消費電力かつ高性能な電子回路を実現するため、実用レベルの応用技術開発を推し進める。