独立行政法人 産業技術総合研究所【理事長 吉川 弘之】(以下「産総研」という)エレクトロニクス研究部門【部門長 伊藤 順司】は、独立した二つのゲートで4端子駆動動作をするデバイス技術を、次世代トランジスタとして期待されるダブルゲートMOSFETで実現することに成功した。自在なしきい値電圧制御性などの独自の4端子駆動機能をゲート長80nm(1ナノメートル:10億分の1メートル)のサブ0.1ミクロンデバイスで系統的に実証した。この成果は、最適なパワー制御・動作速度制御などをフレキシブル且つ、ダイナミックに行う革新的LSI実現に先鞭をつけるものである。

○究極のMOSFETに新たな機能をインストール

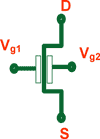

ダブルゲートMOSFET(1984年に旧工業技術院電子技術総合研究所(現産総研)が提案、当初XMOSと命名)は、通常のシングルゲートMOSFETの、リーク電流や短チャネル効果の増大による微細化限界を打破できる次世代トランジスタとして期待されている。しかし、従来のダブルゲートMOSFETでは二つのゲートは一体で同一電圧にしかできず、3端子型動作しかできなかった。これに対して今回、二つのゲートを分離独立して4端子駆動できるダブルゲートMOSFETの開発に成功した。4端子化によって新たに獲得できた最も顕著な機能は、二つのゲートのうち、一方のゲートで行うスイッチング動作に加えて、他方のゲートでそのしきい値電圧を自在に制御できることである。これは、トランジスタ動作速度を最適に制御したり、待機時のリーク電流によるパワーロスを実質的にゼロにできることを意味する。すなわち、この技術開発は、動作速度を犠牲にせずに最適にパワー制御された超低消費電力VLSIの実用化への道を拓く成果と言える。さらに4端子駆動型ダブルゲートMOSFETは、独立に二つの入力が行える演算機能を持つMOSFETと見立てることができ、一つの素子で回路機能があるゆえに、集積回路素子数を大幅に削減できる可能性もある。これらの4端子駆動機能は従来のMOSFETにはないもので、トランジスタの大革新が期待される。

○汎用性の高い4端子駆動型ダブルゲート技術を開発

技術的ブレイクスルーは、現状の半導体技術とのコンパティビリティが高い微細加工技術を用いて、4端子駆動可能な分離ダブルゲート作製技術を開発したことである。起立したフィン型のごく薄いシリコン(Si)チャネルの作製には、産総研が開発した、Siの結晶面に依存する結晶面異方性ウエットエッチングを用い、理想的な矩形断面を持たせることに成功した。この極薄フィン型チャネルを両側からはさむ、分離した2つの多結晶Siゲートを、微細化学的機械的研磨(CMP)技術によって形成した。今回開発したこれらの微細加工技術は、結晶面異方性ウエットエッチング、微細CMP技術とも、現状の半導体技術とコンパチブルな技術であり、実用化が容易である。従来のダブルゲートMOSFETに新たな機能をインストールできたため、Si集積回路に大革新をもたらすことが期待できる。

○4端子駆動型ダブルゲートMOSFET独自の自在なしきい値電圧制御性を系統的に実証

試作したゲート長80nmの4端子駆動型ダブルゲートMOSFETにおいて、一方のゲート電圧によって、トランジスタのしきい値電圧Vthを自由に変えることが出来ることを実証した。この機能は、高いしきい値での低消費電力化と低いしきい値での高速化を両立することができる画期的成果である。また、フィン型Siチャネル厚が薄いほど、しきい値電圧制御性にも短チャネル効果抑止特性にも優れることをSi-フィン厚13nmの試作デバイスで実証した。さらに、二つのゲート電圧にオフセットをかけて連動する4端子駆動モードで、Vthを自由に制御しつつ最大の短チャネル効果抑止特性が得られることも実験的に実証した。

本成果によって、次世代のトランジスタとして期待されているダブルゲートMOSFETの4端子化を実現し、革新的な機能の拡大が可能になった。今後は、今回開発した4端子駆動型ダブルゲートMOSFETを最適に用いた、新たな集積回路技術の創出に取り組む予定である。

本成果は、2003年12月8~10日に米国ワシントンDCで開催される、国際電子デバイス会議(IEDM2003:2003 IEEE International Electron Devices Meeting)で発表する。ちなみに、産総研エレクトロニクス研究部門では、昨年に続いてのIEDMでの新デバイスの発表である。また、本研究に関連した特許を3件出願中である。

IT世界を支えるSi VLSIの驚異的な発展は、そこに用いられるSi MOSFETの微細化によって支えられてきた。しかしながら、きわめて近い将来に我々は、極微細化によって、素子がオフ時でも流れてしまうリーク電流の増加と、ドレイン - ソース間の干渉によるトランジスタ特性の劣化により、重大な障害(赤煉瓦障壁(Red Brick Wall)と呼ばれている)に直面する。ソース - ドレインの接近による干渉のため、素子特性が急激に劣化するという後者の短チャネル効果を打破するには、薄いチャネル層を二つのゲートで挟み込んでシールドするダブルゲートMOSFETが最も有効なデバイス構造であり、ITRS半導体ロードマップでも認知されている。一方、前者のリーク電流による消費電力の問題は、深刻な状況になってきている。CPUチップの消費電力はすでに100Wを越えるレベルにまで達しており、何らかの解決策が見いだされない限り、デバイス作製技術の進展があったとしても、実際にはこれ以上発熱の問題から集積化できないという状況になってしまう。

今回、産総研で開発した4端子駆動型ダブルゲートMOSFET技術は、上記のSi半導体技術が直面する障害を何れもブレイクスルーする画期的な成果であり、最適なパワー・動作速度制御や新機能などをフレキシブルに持たせる未来型集積回路実現に先鞭をつけたと言える。

(1) 理想的な矩形断面を持つ4端子駆動型ダブルゲートMOSFET技術を開発

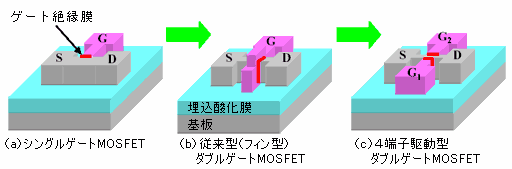

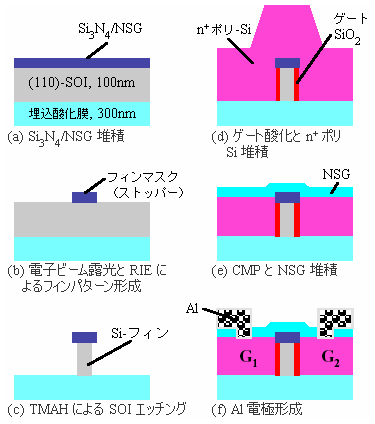

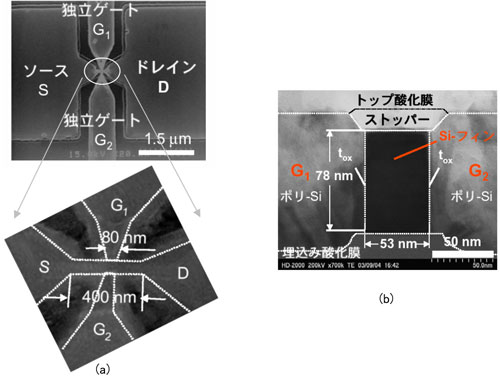

【図1】は、シングルゲートMOSFET(比較のためにサイドゲートで表示)とその微細化限界を打破する従来型(フィン型)のダブルゲートMOSFET、および、今回試作に成功した4端子駆動型ダブルゲートMOSFETを示している。シングルゲートMOSFETでは、基板側にドレイン - ソースを分離するものが特にないために、微細化を進めるに従って干渉がおこり、ゲートの効きが悪くなってトランジスタ特性が劣化してしまう。これに対して、ダブルゲートMOSFETでは、ドレインからソースへの干渉を、二重ゲートで遮蔽できるので、短チャネル効果を抑止できる、最も微細化に適したMOSFETであると考えられている。しかしながら、従来型ダブルゲートMOSFETでは二つのゲートが一体化されており、3端子動作しかできなかった。これに対して、今回試作に成功した4端子駆動型ダブルゲートMOSFETは、独立した二つのゲートを持ち4端子動作が可能となる。フィン型チャネルの作製には、産総研が開発した結晶面異方性ウエットエッチングを用いた。Si結晶のアルカリ系エッチング溶液(2.38% TMAH (tetramethylammonium hydroxide))に対するエッチング速度は強い異方性を持ち、(100)面、(110)面、(111)面の順に遅くなる。この異方性を利用して、(110)SOIウエハに、<112>方向にアライメントされた窒化膜/酸化膜(Si3N4/NSG)マスクによって、【図2】(c)に示すようにSi-フィンを作製した。Si-フィンの側壁は、エッチング速度の極端に遅い(111)面となるので、精度よくアスペクト比の高い微細フィン型チャネルを作ることができる。Si-フィンの作製に通常用いられるドライエッチングではどうしても断面がだれてしまったベル型になり、しきい値電圧のばらつきの原因となるが、産総研が開発したこの技術は、理想的な矩形断面チャネルを作製する方法として、世界的に注目されている(2003 デバイスリサーチコンファレンス(DRC)など多数の国際会議で発表)。その後、窒化膜/酸化膜(Si3N4/NSG)マスクをストッパーとして用い、微細CMP(化学的機械的研磨)技術によって【図2】(e)に示すように分離ゲートを作製した。【図3】は、試作した4端子駆動型ダブルゲートMOSFET平面の走査型電子顕微鏡(SEM)写真と断面の透過型電子顕微鏡(TEM)写真を示す。ナノメートルサイズで、完璧な分離ダブルゲート作製に成功したのは世界で初めてである。すなわち、最も研究開発が進んでいるフィン型ダブルゲートMOSFETで、世界に先んじて4端子化技術を示したことになる。

|

|

|

図1 MOSFETの進化。(a)シングルゲートMOSFET、(b)従来型(フィン型)ダブルゲートMOSFET、(c)今回試作に成功した4端子駆動型ダブルゲートMOSFET

|

|

|

図2 4端子駆動型ダブルゲートMOSFETのプロセスフロー。独自の結晶面異方性ウエットエッチングと微細CMP技術を用いている。

Si3N4/NSG:シリコン窒化膜/酸化膜、SOI:埋込酸化膜上のシリコン層、RIE:反応性イオンエッチング、TMAH:アルカリ系の選択エッチング溶液、CMP:化学的機械的研磨

|

|

|

図3 試作した4端子駆動型ダブルゲートMOSFETの、(a)平面SEM写真、(b)Siフィン型チャネルの断面TEM写真。理想的な矩形フィンチャネル断面と完璧な分離ダブルゲートを示している。

|

(2)4端子駆動型ダブルゲートMOSFETの独自の機能を実証

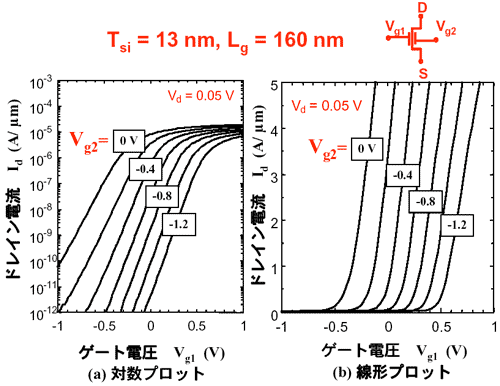

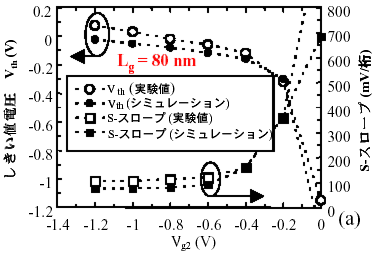

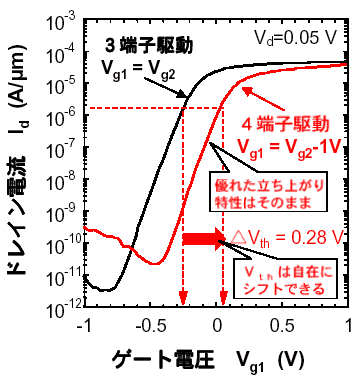

【図4】は、極薄Si-フィン厚13nm、ゲート長160nmのnチャネル4端子駆動型ダブルゲートMOSFETのしきい値電圧Vth制御特性を示している。Vth制御ゲート電圧Vg2に負の電圧を増やして行くと、Vg1に対するVthは正方向に制御され、元々Vthが負の値*であったこのデバイスが、Vg2=-0.6Vですでに正の値となって動作していることがわかる。この実験結果が明瞭に示しているように、Vth制御性は、短チャネル効果抑止機能と同様にSi-フィン厚が薄いほど優れていることも系統的に明らかにした。【図5】は、4端子駆動型ダブルゲートMOSFETの、Vg2に対するVthと電流立ち上がりを表すサブスレッショールドスロープ(Sスロープ)の実験値およびシミュレーション値(Si-フィン厚43nm、ゲート長80nmの場合)を示しており、実験値と計算値はよく一致している。4端子駆動型ダブルゲートMOSFETではVthを自由に制御できることが証明されたが、Sスロープは3端子型ダブルゲートMOSFETよりも若干犠牲になる。しかし、【図6】に示すように、4端子駆動型ダブルゲートMOSFETにおいても、Vg2にオフセットをかけて、Vg1, Vg2を追従モードで動作させる4端子駆動モードでは、Vthを自由に制御(この場合は、-0.25Vから+0.03Vへと0.28Vの正シフト)しつつ、Sスロープも、最小値を示す3端子駆動モード(Vg1=Vg2)と変わらない優れた値を持たせることができる。【図4】に示したSi-フィン厚13nmの試作デバイスでは、同じ-1VのVg2オフセットで、0.43VのVth正シフトと理論限界値である60mV/桁のSスロープというさらに優れた特性を示した。

【図6】の例で示すように、4端子駆動型ダブルゲートMOSFETでは、独立した2つのゲートを有するが故に、従来型ダブルゲートMOSFETを含めた3端子駆動MOSFETでは不可能な、新たな機能を実現できる。すなわち、しきい値制御によるパワーと速度の最適制御のみならず、素子自身がスイッチ機能以上の多機能を発揮できる、より進化したMOSデバイスが実現されたことになる。

*試作デバイスはn+ポリSiゲートであるため、元のしきい値電圧(Vg1=Vg2の場合)は負の値になっている。ゲート電極材料の選択で正の値にすることは可能である。

|

|

|

図4 試作したSi-フィン厚13nm, ゲート長160nmの4端子駆動型ダブルゲートMOSFETのしきい値電圧制御特性。

(a) ドレイン電流を対数プロット、(b) ドレイン電流を線形プロット。Vth制御電圧Vg2により、しきい値電圧(ドレイン電流が立ち上がるところのゲート電圧)を自在に制御できることを示している。

|

|

|

図5 4端子駆動型ダブルゲートMOSFETのVth制御電圧Vg2の関数としての、しきい値電圧Vthおよびサブスレッショールドスロープ(Sスロープ)。Si-フィン厚=43nm、 ゲート長=80nmである。試作デバイスの実験値とシミュレーション結果はよい一致を示している。

|

|

|

|

図6 試作した80nmゲート長4端子駆動型ダブルゲートMOSFETの、3端子駆動モード(Vg2=Vg1)と4端子駆動モード(Vg2=Vg1-1V)での電流-電圧特性。4端子駆動モードでは、しきい値電圧制御(正シフト)と短チャネル効果抑止(立ち上がり特性(Sスロープ)が3端子駆動モードと同等)を同時に実現している。

|

本成果によって、次世代のトランジスタとして期待されているダブルゲートMOSFETの4端子化を実現し、更なる機能の拡大が可能になった。最適しきい値制御などによって、省エネ化、高速化を両立させ、かつ、ダイナミックに制御できる革新的LSIのキーデバイスとして期待される。今後は、この進化したMOSデバイスを最適に用いた、革新的な4端子駆動型ダブルゲートMOS集積回路技術の創出を目指している。