独立行政法人 産業技術総合研究所【理事長 野間口 有】(以下「産総研」という)ナノエレクトロニクス研究部門【研究部門長 金丸 正剛】連携研究体グリーン・ナノエレクトロニクスセンター【連携研究体長 横山 直樹】右田 真司 主任研究員らは、チャネル長が3 nmという非常に小さいトランジスタの動作実証に成功した。

開発したトランジスタは、シリコン結晶をアルカリ溶液で溶解したときにできるV型の溝を利用して作製した。溶解条件を調整することで溝の先端部分を3 nmの鋭さに仕上げ、この部分をチャネルとした。接合は、シリコン結晶全体に不純物を均一に分布させる新しい技術で形成した。電気特性では、長さ3 nmのチャネルに対してチャネル厚さを1 nm相当に薄くしたときに、電流調整能力が最大化した。さらにトランジスタを流れる電子の速度を調べたところ、長さ3 nmのチャネル内部では散乱の影響が抑制され、準弾道的に流れていることが確認できた。これはエネルギーを損失せずに電気が流せることを意味しており、集積回路の消費電力低減が期待できる。

この技術の詳細は、2012年12月10~12日に米国サンフランシスコ市で開催される国際会議2012 International Electron Devices Meeting (IEDM 2012)で発表される。

|

|

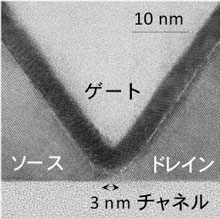

試作したチャネル長3 nmのトランジスタの電子顕微鏡像 |

近年、携帯情報端末の普及やIT機器の高機能化に伴う消費電力の増大が懸念され、電子情報機器の消費電力低減に関する社会的要求が高まっている。電子情報機器の中核部品である大規模集積回路(LSI)には1億個以上のトランジスタが組み込まれており、内部で高速の演算処理を行っている。情報機器の消費電力を低減するためには、この膨大な数のトランジスタが消費するエネルギーを少なくする技術開発が必要とされている。

トランジスタの消費エネルギーを減らすために材料、構造、そして動作原理といったさまざまな観点からの研究開発が世界各国で行われている。構造に関しては微細化が重要な設計指針となっており、今日では20 nm相当の寸法で作製した立体構造トランジスタで構成されるLSIが市販されている。また、研究開発では10 nm以下に微細化したトランジスタの性能検証に関心が集まっている。

連携研究体グリーン・ナノエレクトロニクスセンター(GNC)は、内閣府と独立行政法人 日本学術振興会によって運営される最先端研究開発支援プログラム(FIRST)に採択されたプロジェクトを実施するために2010年4月に設立された。企業5社(富士通株式会社、株式会社 東芝、株式会社 日立製作所、ルネサスエレクトロニクス株式会社、株式会社アルバック)からの出向研究者と産総研研究者によって構成されている。GNCでは、2011年度より、従来のLSIの消費電力を10分の1~100分の1に低減することを目標に、トランジスタの研究開発を進めている。

なお、この研究開発は、最先端研究開発支援プログラム(FIRST)のプロジェクト「グリーン・ナノエレクトロニクスのコア技術開発」(中心研究者 横山直樹)の助成により行われた。

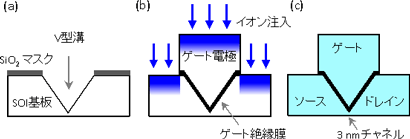

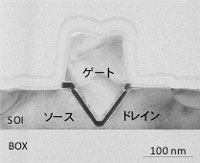

今回の技術は、既存の半導体製造方法を用いながら、ナノメートルスケールの構造制御技術および新しい接合技術を取り入れることによって開発した。試作の手順を図1に示す。絶縁膜の上にシリコン単結晶が貼り合わせてあるSOI基板を用いてトランジスタを作製した。最初にアルカリ溶液でシリコン単結晶の限定された領域を溶解してV型の溝を形成した。シリコンの結晶面によって溶解速度が大きく異なる性質を利用することで、特定の結晶面が残り、V型の溝が形成される。溶解の温度や時間を調整することで、V溝の先端は曲率半径が3 nmという鋭さになる。この部分がトランジスタのチャネルになる。一方でSOI基板の厚さについてはV溝の深さを精密に調整することで、チャネルの厚さが自在に設計できる。V溝構造を形成した後にゲート絶縁膜とゲート電極膜を堆積、パターン加工を行ってゲート電極を作製する。ソースとドレインに相当する部分にイオン注入を行う。最後に高温の熱処理で不純物の拡散を促進し、シリコン結晶全体にわたって不純物を均一に高濃度に行き渡らせた。これまでのトランジスタの作製方法では、不純物の拡散を抑制して濃度勾配を作り出し、PN接合を形成する。ところが微細化が10 nm以下のトランジスタにおいてはPN接合の形成は困難である。そこで今回の開発ではこの課題を克服するために、PN接合を用いずにゲート電極の電界によって作り出されるエネルギー障壁だけでトランジスタを動作させる、新しい接合技術を取り入れた。試作したトランジスタの断面構造を電子顕微鏡で観察した像を図2に示す。

|

|

図1 開発したトランジスタの試作手順

(a) アルカリ溶液でSOI基板を溶解し、V型溝を作る。(b) ゲート絶縁膜、電極膜を堆積。ゲートパターンを加工した後にイオン注入。(c) 熱処理によって不純物を高濃度に均一に分布させて完成。V型溝の先端部分が曲率半径3 nmの鋭さを有しており、トランジスタのチャネルとなる。 |

|

|

図2 試作したトランジスタの断面構造の電子顕微鏡像 |

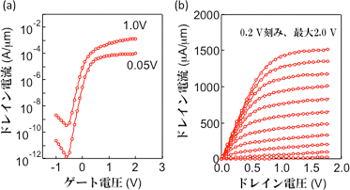

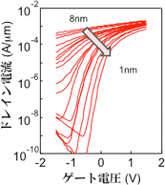

チャネル長3 nmのトランジスタの電気特性を図3に示す。ゲート電圧を変化させることで、ドレイン電流を6桁以上にわたって変調することができた。ドレイン電圧の変化に対してもトランジスタとして正常な電流応答が確認できた。

|

|

図3 試作したトランジスタの電気特性

(a) ゲート電圧とドレイン電流の関係。図中の数字はドレイン電圧の設定値。(b) ドレイン電圧とドレイン電流の関係。ゲート電圧を0.2 V刻みで最大2.0 Vまで変化させて測定。これらの測定より、トランジスタが正常動作することが確認できた。 |

トランジスタの高性能化には、チャネルの厚さも重要なパラメータの一つである。SOI基板のチャネル部分の厚さの効果を系統的に調べた結果を図4に示す。厚さを1 nm相当に薄くすることが、高性能化に必須であることが分かった。微細化が進行した極限では、構造をナノメートルの寸法で制御することが必要である。

|

|

図4 チャネル厚さをナノメートルスケールで変化させたときの電気特性

SOI基板のチャネル部分の厚さを変化させて作製したチャネル長3 nmトランジスタのゲート電圧とドレイン電流の関係。チャネル部分の厚さを1 nm相当に薄くすることが、高性能化にとって必須である。 |

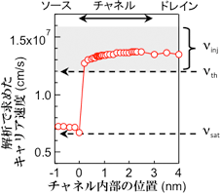

さらに今回開発したトランジスタ内部の電子の速度を解析した結果を図5に示す。ソース端からドレイン端まで一定の速度で電子が流れている。通常のトランジスタの場合、ソース端から注入された電子はチャネル内部での散乱を受けるために次第に速度が低下する。ところがチャネル長3 nmのトランジスタでは、電子がほとんど散乱を受けずにドレインまで到達するので、速度が一定に保たれている。散乱を受けないということは、トランジスタ内部でエネルギーを損失しないことを意味する。このようなトランジスタを将来のLSIに用いれば、消費エネルギーの低減が期待できる。

|

|

図5 チャネル内部の電子の速度の解析結果

ソース端から注入された電子は、速度が低下することなくドレインに到達している。すなわち大部分の電子は散乱を受けることなくチャネル内部を通過していることを意味する。 |

今回開発したトランジスタを元に、さらに低消費電力化が可能な新原理トランジスタの研究を発展させる。