独立行政法人 産業技術総合研究所【理事長 中鉢 良治】(以下「産総研」という)ナノエレクトロニクス研究部門【研究部門長 金丸 正剛】シリコンナノデバイスグループ 水林 亘 主任研究員、昌原 明植 研究グループ長は、日新イオン機器株式会社【代表取締役社長 長井 宣夫】と共同で、14 nm世代以降のフィンFETに適用できる、低抵抗ソース・ドレイン形成技術を開発した。

14 nm世代以降のフィンFETでは、極薄(10 nm以下)のシリコンフィン部分に低抵抗のソース・ドレインを形成することが最大の課題となっていた。通常、低抵抗化は不純物イオン注入により行うが、フィン部分では、注入時に結晶欠陥が生成して抵抗が大きくなってしまう。この結晶欠陥の解消が困難であるため、結果として低抵抗化が困難となっている。今回開発した高温イオン注入技術は、結晶欠陥を発生させずに極薄のフィン部分に不純物イオンを注入し、低抵抗化できる。また、フィンFETの信頼性も大幅に向上した。今回開発した技術は、14 nm世代以降のフィンFETにおける低抵抗ソース・ドレイン形成の課題を解決することにつながった。

なお、この技術の詳細は、平成25年12月9~11日に米国ワシントンD.C.で開催されるInternational Electron Device Meeting(IEDM)で発表される。

|

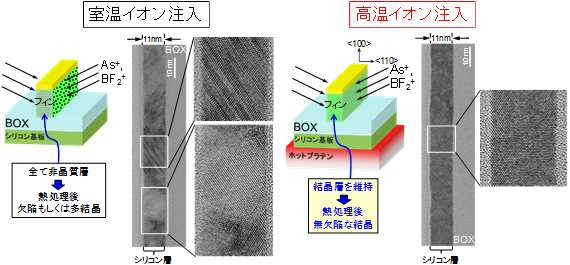

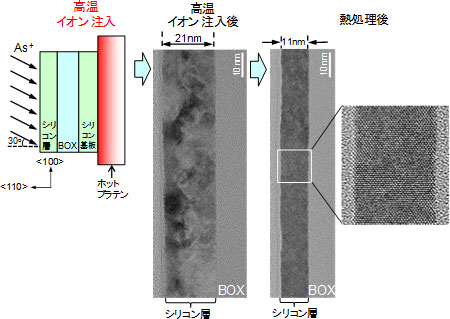

室温イオン注入と高温イオン注入の模式図と熱処理後の極薄シリコン層の結晶状態

図中のBOXは二酸化シリコン(SiO2)、As+はヒ素イオン、BF2+は二フッ化ホウ素イオン |

これまで、シリコン集積回路は、その最小構成単位であるトランジスタ素子を微細化することによって高性能化・高集積化を実現してきた。素子の微細化はコスト削減にもつながるため、微細素子開発の激烈な競争が続いている。しかし、2017年以降に市場投入が想定されている14 nm世代やそれ以降のトランジスタ技術では、極薄フィン部分のソース・ドレインの抵抗の寄与が顕在化することが最大の課題となっている。抵抗増大はトランジスタの性能低下の要因となるため、低抵抗のソース・ドレインを形成する技術が強く求められている。

これまで、産総研では、フィンFETと呼ばれる新構造トランジスタの研究開発を行ってきた。2003年にゲートを独立に制御できる4端子フィンFETを開発し、電気的にしきい値電圧(Vth)を制御できることを実証した(2003年12月9日 産総研プレス発表)。2012年には、Vthのバラツキを低減するため、通常の多結晶金属のゲート電極の代わりに非晶質金属のゲート電極を用いて、バラツキの大幅な低減に成功した(2012年12月12日 産総研プレス発表)。現在、フィンFETの性能を一層向上させるため、プロセス技術について研究開発を継続している。

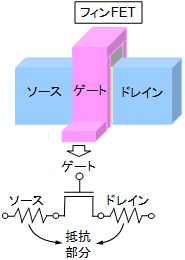

図1にフィンFETの模式図を示す。もし、ソース・ドレインの抵抗が大きいと、トランジスタの動作時に電圧降下が顕著となり、性能の指標となるドレイン電流が減少してしまう。高性能フィンFETを実現するには、低抵抗ソース・ドレインを形成する技術が必要となる。一般的なソース・ドレインの形成方法として、不純物をイオン注入して、その後の熱処理により、注入した不純物を活性化させる方法がある。しかし、この方法では、極薄フィン部分のソース・ドレインでは抵抗が増大してしまうという課題がある。

|

|

図1 フィンFETとソース・ドレインの抵抗の模式図 |

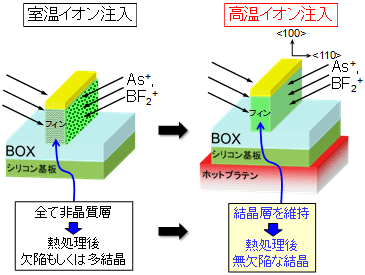

図2に従来の室温イオン注入と、今回開発した高温イオン注入を比較した模式図を示す。従来の室温イオン注入の場合、イオン注入後フィン部分全体が非晶質層となる。結晶層がほとんどないため、その後の活性化熱処理の際にも、欠陥の多い結晶か多結晶となってしまい、抵抗増大を引き起こす。イオン注入後も結晶層を維持する方法として高温イオン注入がある。高温イオン注入は、フィン部分の結晶層が維持できる反面、室温イオン注入に比べ欠陥が多く生成する。従来の平面型トランジスタでは、高温イオン注入後に熱処理を行っても結晶回復ができないか欠陥が残り、トランジスタの性能低下を起こす。このため、平面型トランジスタでは、高温イオン注入が用いられてこなかった。しかし、フィンFETは、フィンの膜厚が薄いので、高温イオン注入で生成された欠陥は熱処理によりフィンから抜け、残留欠陥の課題を解決できる。図2に示すように、フィンFETにおける高温イオン注入の場合、熱処理によって欠陥がなくなり、無欠陥の結晶へと回復できるため、抵抗が大幅に低減する。すなわち、高温イオン注入により、無欠陥で低抵抗のソース・ドレイン形成が期待できる。

|

|

図2 従来の室温イオン注入と今回開発した高温イオン注入によるフィンFETのソース・ドレイン形成の模式図 |

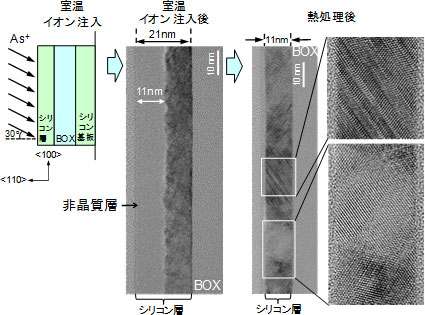

フィンFETのソース・ドレインの作製と同じ条件で極薄シリコン層に室温イオン注入と高温イオン注入を行い、シリコン層の結晶状態に及ぼす影響を調べた(図3、4)。まず、室温イオン注入の場合、厚さ21 nmのシリコン層にイオン注入すると、厚さ11 nmの非晶質層が生成した(図3)。次に、厚さ11 nmのシリコン層がすべて非晶質の試料を作製して、それを熱処理した。この場合、シリコン層に結晶の回復に必要な種となる結晶部分がないため、結晶を回復できず、多結晶や双晶などが形成される(図3)。これは、ソース・ドレインの抵抗増大を引き起こす。

|

|

図3 室温イオン注入の場合の活性化熱処理前後のシリコン層の結晶状態 |

高温イオン注入は、注入温度500 ℃で行った。イオン注入後も、シリコン層全体で結晶層が維持されていた(図4)。これらが結晶の回復に必要な種となるので、11 nmと極薄のシリコン層でも、熱処理によって結晶を回復でき、無欠陥の結晶層となった。これは、ソース・ドレインの抵抗の低減につながるため、高温イオン注入により極薄フィン部分に無欠陥で低抵抗のソース・ドレインを形成できる。

|

|

図4 高温イオン注入の場合の活性化熱処理前後のシリコン層の結晶状態 |

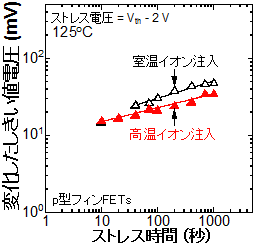

次に、高温イオン注入がフィンFETの信頼性に及ぼす影響について評価した(図5)。信頼性は、ゲートに一定電圧をかけた時のしきい値電圧の経時変化から評価した。高温イオン注入によるフィンFETのしきい値電圧の変化は、室温イオン注入によるフィンFETの変化よりも小さく、信頼性が向上したことが分かった。すなわち、高温イオン注入により高信頼性フィンFETが作製できる。これらの結果は、高温イオン注入は、14 nm世代以降のフィンFETのフィン部分のソース・ドレイン形成技術として有望な技術であることを示している。

|

|

図5 室温イオン注入と高温イオン注入によるフィンFETのしきい値電圧の経時変化 |

今後は、高温イオン注入を量産フィンFET製造プロセスへの適用に向け、フィンFET製造プロセスの最適化、量産用装置開発を行う。