国立研究開発法人 産業技術総合研究所(以下「産総研」という)デバイス技術研究部門 先端集積回路研究グループ 更田 裕司 主任研究員、新原理デバイス研究グループ 森 貴洋 上級主任研究員らは、極低温4ケルビンで動作する半導体スピン量子ビットの状態読み出しのための、小型で高速な電流計測回路を開発した。

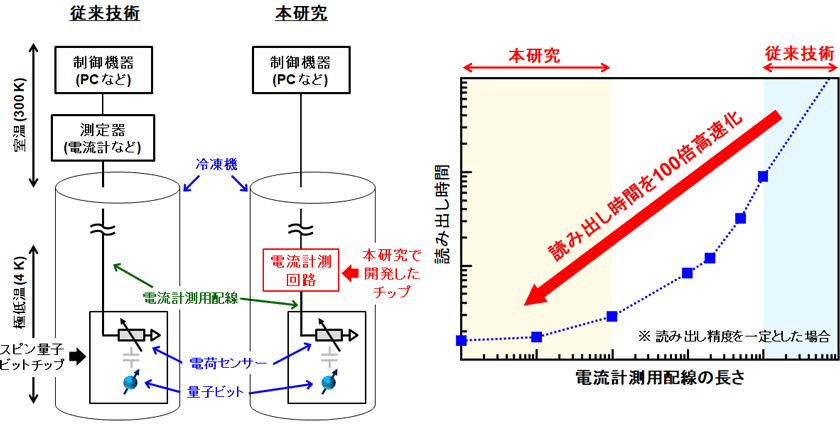

大規模な誤り訂正型(汎用)量子コンピューターは、量子ビットの状態を読み出しながら演算が行われる。したがって、性能の向上には、量子ビットの状態を速く正確に検出する必要がある。この検知は、スピン量子ビットの状態読み出しといい、量子ビットの近傍に置かれた電荷センサーの電流変化を計測する手法が一般的である。従来この電流の計測には、室温で作動する測定器が用いられてきたので、測定器と冷凍機内の電荷センサーとの間に長い配線が必要となる。そのため、電流の読み出し速度が遅いという問題があった。本研究では、冷凍機内の電荷センサー近傍で動作可能な電流計測回路を新たに設計し、配線を大幅に短くする技術を開発した。一般的な半導体プロセスで製造された電流計測回路のチップを4ケルビンに冷却し動作を検証した結果、従来の室温での計測方式に比べて、読み出し速度を100倍に高速化できることを確認した。

なお、この技術の詳細は、2022年6月13~17日に米国ハワイで開催される2022 IEEE VLSI Symposium on Technology and Circuitsで発表される。

開発した極低温で動作する電流計測回路と従来技術との比較

量子コンピューターの実用化には100万超の量子ビットを集積した誤り訂正型(汎用)量子コンピューターが望まれる。このような量子コンピューターは、演算の誤りを訂正しながら演算を実行するものであるが、それぞれの誤り訂正には量子ビットの状態読み出しが伴うため、高速な読み出し動作が求められる。特に、演算の実行から量子ビット読み出しまでの一連の操作を、スピン緩和時間(数十マイクロ秒程度)内に完了させる必要がある。

現時点では、スピン量子ビットは数ビットの集積にとどまっており、その状態読み出しには、室温に置かれた測定器が用いられている。この方式では、冷凍機内にある量子ビットから、室温にある測定器まで長い配線が必要で、量子ビットの読み出し速度が1ミリ秒程度に制限されるという課題がある。したがって、数十マイクロ秒のスピン緩和時間内に収めるためには、少なくともこれを100倍以上高速化する必要がある。このことを実現する技術として、ゲートリフレクトメトリと呼ばれる手法が提案されているが、回路規模が大きくなるため、多数の量子ビット読み出しに対応する集積化には課題が多い。

そこで、集積化が容易な汎用半導体プロセスで読み出し回路を製造し、それを量子ビット近傍の極低温下で動作させることで、両者の距離を大幅に短縮し高速動作を実現する技術開発に期待が高まっている。これは、いわゆるクライオCMOS技術の一種である。

産総研ではこれまでに、高温動作可能なスピン量子ビットの開発(2019年1月24日 産総研プレス発表)やシリコン量子ビットの高速化を実現する新集積構造の提案(2021年8月5日 産総研成果発表)など、シリコン量子コンピューターの実現に向けたデバイス技術に関する成果を得てきた。これに加えて、量子ビットの大規模集積化に向けた量子ビットの制御・読み出しなどに必要な極低温で回路を動作させるための集積回路設計技術、および冷凍機内でも正確に回路動作を検証・評価する技術の開発にも取り組んできた。

また、以前から産総研では、室温動作を前提としてさまざまなセンサー向け計測用集積回路の研究開発を実施しており、今回そこで培われた回路設計に関する知見を応用し、低温で動作する量子ビット読み出し向けの電流計測回路を開発した。

なお、本研究開発は、文部科学省光・量子飛躍フラッグシッププログラム(Q-LEAP)における量子情報処理領域・基礎基盤研究「シリコン量子ビットによる量子計算機向け大規模集積回路の実現」 (JPMXS0118069228)の助成を受けて行った。

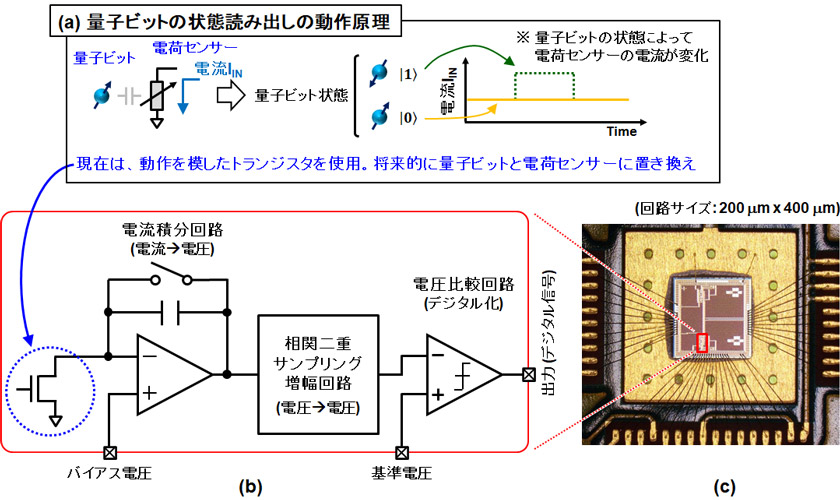

スピン量子ビットの状態読み出しには、量子ビットの近傍に電荷センサーを置き、量子ビットの状態によって変化する電荷センサーを流れる電流を計測する手法が一般的である(図1(a))。この電流変化は、1ナノアンペア以下の微小電流であり、従来は室温に置かれた電流計などの測定器で検出する。この手法では、室温の測定器と冷凍機内の量子ビット・電荷センサーの間に長い配線が必要で、これにより動作が遅くなるという課題があった。そこで本研究では、4ケルビンでも動作する電流計測回路を開発し、電流の計測を極低温の冷凍機内で行い、量子ビット・電荷センサーとの配線を大幅に短縮することで、高速読み出しを実現した。

開発した電流計測回路は、大きく3つの回路ブロックで構成される(図1(b))。まず、積分回路で計測する電流を電圧に変換する。産総研におけるこれまでの極低温トランジスタ特性の評価から、極低温ではフリッカ雑音が増大することが明らかになっており、その影響で読み出し時間が増加する恐れがあったため、本回路ではその対策として積分回路の出力に対して相関二重サンプリングを行うことにした。最後にその出力を基準電圧と比較し、スピン量子ビットの状態(スピンの向き)を表すデジタル値を出力する(例えば、スピンの上向きはデジタル値0、下向きはデジタル値1など)。なお、今回の回路では、量子ビットと電荷センサーの代わりに、その動作を模したトランジスタを使用した。

図1 (a) 量子ビット状態の読み出し動作原理 (b) 開発した電流計測回路のブロック図 (c) 本回路を実装したチップの写真

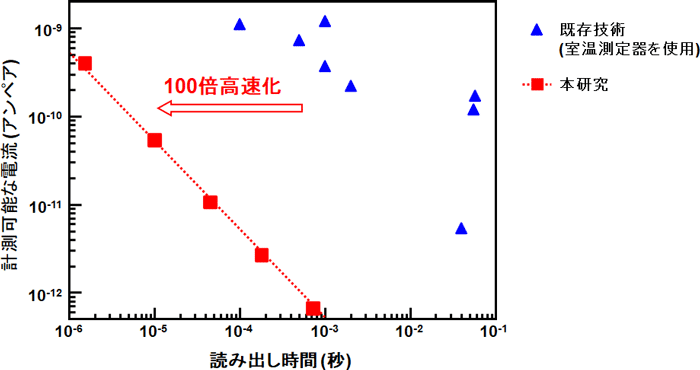

本回路を一般的な商用CMOS半導体プロセスで製造し(チップ写真を図1(c)に示す)、極低温4ケルビンに冷却し評価した。通常、チップの評価には、電力供給・信号入出力用の配線とチップの間をつなぐ評価用基板が必要となるが、今回、冷凍機内での回路性能評価のために、独自の評価用基板も併せて開発した。図2に、計測可能な(電荷センサーの)電流値とその読み出し時間について、室温の測定器を用いる既存技術と本研究の比較を示す。計測可能な電流値と測定時間は、トレードオフの関係にあり、開発した電流計測チップを使用することで、電流値一定の条件で、従来よりも100倍高速に計測が可能である。

誤り訂正型(汎用)量子コンピューターの実現には高速な量子ビットの状態読み出しが必須であり、今回開発した量子ビット読み出し向け電流計測回路は、将来の大規模量子コンピューターを実現する基盤技術の一つとしての応用が期待できる。

図2 既存技術と本研究の性能比較

(発表論文の図を改変して引用)

今後は開発した電流計測回路とスピン量子ビット・電荷センサーを接続し、量子ビットの状態読み出し動作を検証する予定である。

掲載誌: 2022 IEEE VLSI Symposium on Technology and Circuits, Digest of Technical Papers

論文タイトル: A Cryogenic CMOS Current Comparator for Spin Qubit Readout Achieving Fast Readout Time and High Current Resolution

著者: Hiroshi Fuketa, Ippei Akita, Tomohiro Ishikawa, Hanpei Koike, Takahiro Mori