国立研究開発法人 産業技術総合研究所【理事長 石村 和彦】(以下「産総研」という)デバイス技術研究部門【研究部門長 中野 隆志】新原理デバイス研究グループ 飯塚 将太 産総研特別研究員、森 貴洋 主任研究員らは、シリコンスピン量子ビット素子を用いた大規模集積量子コンピューターの実現に向けて、スピン量子ビット素子と演算に必要な微小磁石を集積した新しい集積構造を考案した。

量子コンピューターの実用化には100万超の量子ビットを集積した誤り訂正型(汎用)量子コンピューターが望まれる。産総研では、既存の半導体集積化技術を利用できるシリコンスピン量子ビット素子に関する研究を進めている。大規模な集積のためには、製造プロセスにおいて生じる加工線幅の不均一性や配置時の位置誤差などの製造ばらつきに起因する特性不良の発生率を低減し、多数のスピン量子ビット素子を同時に正常動作させる必要がある。しかし、多数のスピン量子ビット素子を大規模に評価する実験技術がないために、素子や集積構造の製造ばらつき耐性を実験で評価できないのが現状である。産総研ではこれらを評価できるシミュレーターの開発を進めてきた。今回の研究ではスピン量子ビット素子の高速動作に必要な微小磁石を素子側方下部に埋め込む構造を新たに考案し、シミュレーターによって高速動作と製造ばらつき耐性を評価した。その結果、配線層に磁石を形成する従来構造と比較してラビ振動(スピンの操作速度)が約10倍速くなるとともに、最大集積可能量子ビット数を制限する要因となっている製造ばらつき耐性を大幅に改善できることを示した。

なお、この研究の詳細は、2021年6月13~19日にオンライン開催される国際会議「2021 Symposia on VLSI Technology and Circuits」において発表され、ハイライトペーパーに選ばれた。

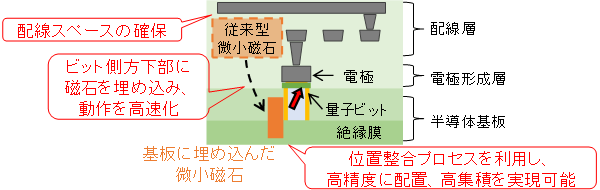

今回考案した新しいシリコンスピン量子ビット素子と微小磁石の集積構造の模式図

大規模集積回路の基本素子であるトランジスタの技術は、これまでの情報処理技術の高度化を支えてきたものの、近年ではその発展速度は鈍化しつつある。しかし一方で、人工知能(AI)やビッグデータを活用して高度に複雑な情報処理を実現することで、複雑化した社会問題を解決し得る情報処理技術が望まれており、このような情報処理に特化したコンピューターハードウエアの研究開発が盛んになっている。その中でも量子コンピューターは、これまでの情報処理技術では解を得られなかった複雑な問題を短時間で解くことができ、物流や金融などの実社会で用いられる組合せ最適化問題の計算や、新規材料の開発や創薬をはじめとする材料分野で用いられる量子化学計算などへの応用が期待される。実用化には100万個を越すスピン量子ビットを集積する必要があるが、現時点では、超伝導量子ビット素子型では100量子ビット以下の集積、シリコンスピン量子ビット素子型では3量子ビットの集積にとどまっており、両者ともに集積度の向上を可能にする技術の確立が望まれている。

産総研ではこれまでに、高温動作可能なスピン量子ビットの開発(産総研プレス発表2019年1月24日)、量子ビット制御回路の開発など、微細シリコン量子コンピューターハードウエアの実現に向けたデバイス技術・集積化技術に関する成果を得てきた。

スピン量子ビット素子において製造ばらつきの評価は、絶対温度1ケルビン前後という極低温下で行われる。現行の冷凍機では数個までの同時評価が限界であるが、産総研では、この既存の評価手法の困難さを補うべく、従来型半導体素子のために開発してきたデバイスシミュレーターImpulse TCADをベースに、シリコンスピン量子ビット素子の性能評価を行うシミュレーターの開発を進めてきた。フランスの電子情報技術研究所(Laboratoire d'électronique des technologies de l'information、略称:LETI)やベルギーのInteruniversity Microelectronics Centre (IMEC)なども同様の開発に取り組んでいるが、スピン量子ビット素子特性を模擬できるデバイスシミュレーターの開発は始まったばかりである。

なお、本研究開発は、文部科学省光・量子飛躍フラッグシッププログラム(Q-LEAP)における量子情報処理領域・基礎基盤研究「シリコン量子ビットによる量子計算機向け大規模集積回路の実現」 (JPMXS0118069228)の助成を受けて行われている。

今回、産総研はスピン量子ビット素子の高速動作に必要な微小磁石を集積する新しい構造を発表した。提案した構造では、従来スピン量子ビット素子の上部にあった微小磁石を、素子の側方下部に形成する。微小磁石がスピン量子ビット素子により近づくので、高速操作に適したより強い傾斜磁場を得ることができるとともに、上部に配線スペースを確保できるので、自己整合型プロセス技術と呼ばれる製造ばらつき耐性を高める製造方法を採用することができる。

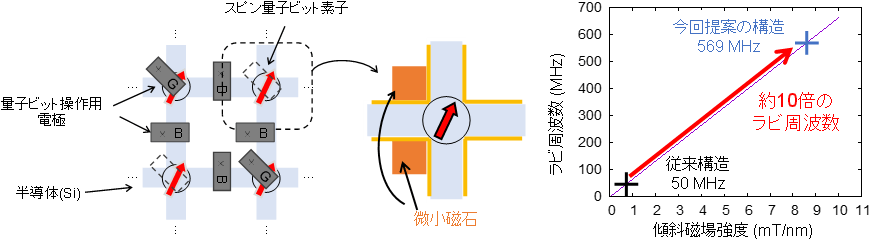

提案した構造では、まず汎用量子コンピューターの実現に必要とされる格子状のビット配置を想定した(図1左)。シミュレーターの計算結果からは、上面から見たときに、スピン量子ビット素子の四隅のうち2カ所に微小磁石を配置した場合(図1中央)が最も強い傾斜磁場強度を得られることがわかった。ラビ周波数は傾斜磁場の大きさに比例して高くなることが知られているが、今回考案した構造では従来構造の約10倍にまで高くできることを示した。

図1 上面から見た格子状ビット配置(左)および微小磁石の位置(中央)と、得られたラビ周波数(右)

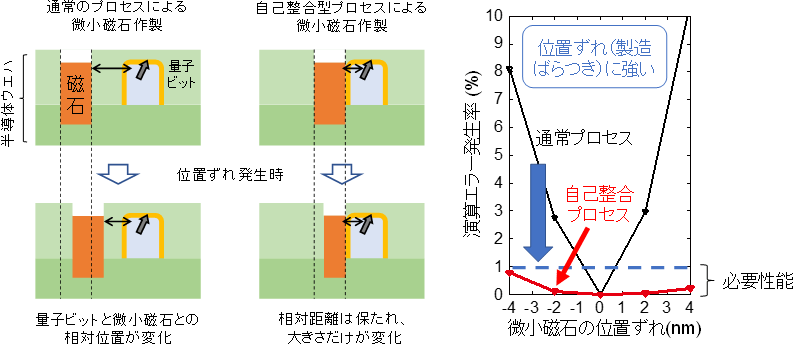

次に、提案した構造について製造ばらつき耐性をシミュレーターによって検証した。通常の製造プロセスでは、スピン量子ビット素子と微小磁石との相対位置に製造ばらつきの一種である微小なずれが生じる。これに対して自己整合型プロセス技術を採用すると、量子ビットそのものが位置基準となるので、スピン量子ビット素子と微小磁石との相対ずれがないため(図2左)、製造ばらつき耐性が高く、製造ばらつきによる特性不良が発生しにくい。このメリットをスピン量子ビット素子の最も重要な性能パラメーターである演算エラー発生率を用いて検証した。特性不良の判定値は、汎用量子コンピューターに必要とされる演算エラー発生率1 %に設定した。通常の形成方法ではスピン量子ビットと微小磁石の位置にわずか1 nmのずれも許容できないが、本構造を採用することで4 nmでも演算エラー発生率を1 %以下に保つことができる(図2右)。現行最先端の極端紫外線リソグラフィ装置で発生する位置ずれは不良発生率の指標である3σ値が2 nm程度とされているが、本構造ではその2倍である4 nm、すなわち6σ値までのずれを許容できる。デバイス構造において6σ値を超える不良発生率は100万個に3個であることから、今回の構造は位置ずれに対して100万個程度までの集積が可能な製造ばらつき耐性を持つと期待される。従来構造では10個程度の集積が限界であったことから大幅な改善が期待できる結果となった。

図2 製造プロセスの違い(左)と位置ずれ発生時の演算エラー発生率(右)

産総研の開発したスピン量子ビット素子特性を模擬できるデバイスシミュレーション技術を生かして、大規模集積が可能な量子コンピューター技術の設計や検証を引き続き進める。さらに、量子コンピューターの実現に必要となる演算の実行、演算結果の読み出し、スピン量子ビット素子の結合などの要素を含めた量子回路の設計を行う。併せて、大規模な極低温実験評価技術についても、その実用化に貢献していきたい。

国立研究開発法人 産業技術総合研究所

デバイス技術研究部門 新原理デバイス研究グループ

産総研特別研究員 飯塚 将太 E-mail:s-iizuka*aist.go.jp(*を@に変更して送信下さい。)

主任研究員 森 貴洋 E-mail:mori-takahiro*aist.go.jp(*を@に変更して送信下さい。)