国立研究開発法人 産業技術総合研究所【理事長 中鉢 良治】(以下「産総研」という)スピントロニクス研究センター【研究センター長 湯浅 新治】金属スピントロニクスチーム 薬師寺 啓 研究チーム長、集積マイクロシステム研究センター【研究センター長 廣島 洋】 高木 秀樹 総括研究主幹、ウエハレベル実装研究チーム 倉島 優一 主任研究員、ナノエレクトロニクス研究部門【研究部門長 安田 哲二】3D集積システムグループ 菊地 克弥 研究グループ長、渡辺 直也 主任研究員は、内閣府 総合科学技術・イノベーション会議(CSTI)が主導する革新的研究開発推進プログラム(ImPACT)の佐橋 政司 プログラム・マネージャーの研究プログラムの一環として、次世代の不揮発性メモリーである磁気ランダムアクセスメモリー(MRAM)の3次元積層プロセス技術を開発した。

MRAMは垂直磁化TMR素子をベースとする記録ビットと、ビット選択に用いる半導体トランジスタ(CMOS)、金属配線(通常、多結晶の銅配線)からなり、通常、垂直磁化TMR素子薄膜(TMR薄膜)は、CMOS形成後に金属配線上に直接形成される(逐次積層)。MRAMの大容量化には、原子レベルの不均一性や凹凸によるTMR薄膜のバラツキ抑制や、材料の選択が重要だが、多結晶銅配線上へのTMR薄膜形成ではバラツキ抑制や材料の選択肢には限界がある。

今回、CMOS形成ウエハー(今回は銅電極形成ウエハーで代用)とTMR薄膜ウエハーを別体形成した後に圧着して接合する、3次元積層プロセス技術によるTMR素子の作製に世界で初めて成功した。この技術開発によりウエハーの別体形成が可能になったことで、薄膜のバラツキが極めて小さく、高性能材料候補の選択肢が広い単結晶材料をMRAM製造に用いる目途が立った。これにより、MRAMの飛躍的な大容量化と高性能化につながると期待される。

この技術の詳細は、2017年5月15日にApplied Physics Expressにオンライン掲載された。

|

|

3次元積層プロセス技術の概要 |

MRAMは、不揮発性、高速、高書き換え耐性などの特徴を持ち、特に不揮発性による省エネルギーの観点から、新世代ユニバーサルメモリーとして注目を集めている。MRAMには、磁界書き込み型MRAM、電流書き込み型MRAM(STT-MRAM)、電圧書き込み型MRAM(電圧トルクMRAM)の3種類がある。垂直磁化TMR素子をベースとしたSTT-MRAMはギガビット級の大容量化が可能であり、国内外のメーカーが製品化を進めている。また、電圧トルクMRAMは基礎開発段階であるが、STT-MRAM以上の省電力性と高速が見込まれる。これらは、不揮発性を活かした周辺メモリーや、従来の半導体メモリー(DRAM)を凌駕する大容量メインメモリーへの応用が考えられる。MRAM開発は、DRAM代替に必要なTMR素子直径20 nm以下の実現に向けて着実に進展しているが、製品化に必要な性能マージンや性能バラツキ抑制について多くの課題が残され、それらの解決が望まれている。

産総研は、大容量MRAMを実現するための中核技術として、2004年に酸化マグネシウム(MgO)トンネル障壁層を持つ高性能TMR素子を発明し、国内外をリードするSTT-MRAM開発を行ってきた。(2004年に産総研が最初に開発したTMR素子は、特殊な単結晶基板上に形成された単結晶TMR素子であった(産総研プレス発表 2004年3月2日))。しかし、通常のMRAM製造プロセスでは、TMR薄膜を多結晶の金属配線上に形成しなくてはならないという制約上、単結晶TMR素子の産業応用は当時の技術では不可能であった。その後、産総研は多結晶のMgOトンネル障壁層とCoFeB強磁性層を組み合わせた多結晶TMR素子を開発し、その産業応用を実現した(産総研プレス発表 2004年9月7日)。もし、単結晶TMR薄膜を用いたMRAMの製造プロセスが実現できれば、原子レベルでの薄膜平坦性や、薄膜均質化による性能バラツキ抑制、さらに多結晶材料にはない高性能な新材料の利用などが可能になり、TMR素子直径20 nm以下の実現に向けた課題の解決に道が開ける。単結晶TMR薄膜のCMOS上への積層は、TMR薄膜を別途単結晶シリコンウエハー上に形成し、後でCMOSウエハーと統合するという、「3次元積層プロセス」を活用することで可能となる。しかし、これまで半導体デバイス分野で開発されてきた3次元積層プロセスは、マイクロメートルスケールでは実績の蓄積があるものの、TMR薄膜ウエハーとCMOSウエハーの組み合わせのような、全く異なる動作原理をもつデバイスを形成したウエハーによるナノメートルスケール厚さの薄膜同士の積層技術は十分に確立されていない。また、TMR素子には厚さわずか1 nmと極めて薄いMgOトンネル絶縁層が含まれ、その機械的強度は非常に弱いため、加重やシリコン基板剥離といったさまざまな機械的ダメージが素子に直接的に加わる3次元積層プロセスのTMR素子への応用は難しいと考えられ、3次元積層プロセス技術によるMRAM製造の可能性は未知であった。そこで今回、単結晶TMR薄膜よりもさらに機械的強度の脆弱な多結晶TMR薄膜を用い、低ダメージなMRAM製造用3次元積層プロセス技術開発に取り組むこととした。

なお、この研究開発は、内閣府 革新的研究開発推進プログラム(ImPACT)「無充電で長期間使用できる究極のエコIT機器の実現(平成26~30年度)」による支援を受けて行った。

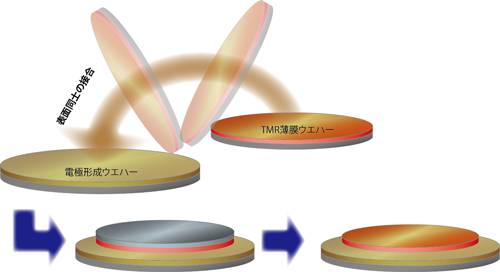

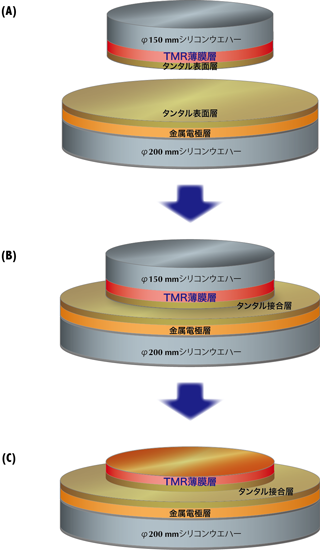

今回開発した3次元積層プロセス技術の概略を図1に示す。図の(A)はプロセス直前の試料の概要であり、直径150 mmのシリコンウエハー上に、単結晶TMR薄膜よりも機械的強度の弱い多結晶TMR薄膜層を形成したウエハー試料と、直径200 mmのシリコンウエハー上に銅電極層を形成したウエハー試料を別々に作製する。なお、ウエハー径は同じでも異なっていてもよい。両試料とも、表面には金属タンタルの接合層を形成する。(B)のウエハーダイレクト接合プロセスでは、タンタル接合層の表面同士を接合面として両ウエハーを接合する。接合界面に欠陥や空隙が生じないように、高真空中で両試料のタンタル接合層表面の平坦化と清浄化を行った後、そのまま真空中で両ウエハーの背面から荷重をかけてタンタル接合層同士を接合する。(C)のウエハー裏面研削プロセスでは、不要となる片方のウエハーを研削して除去する。今回は、多結晶TMR薄膜層のウエハーを裏面から研削して除去した。これらのプロセスを経て、直径200 mmシリコンウエハー上に、銅電極層、タンタル接合層、多結晶TMR薄膜層の順に形成された3次元積層試料が得られた。

|

|

図1 今回開発した3次元積層プロセス技術の概要 |

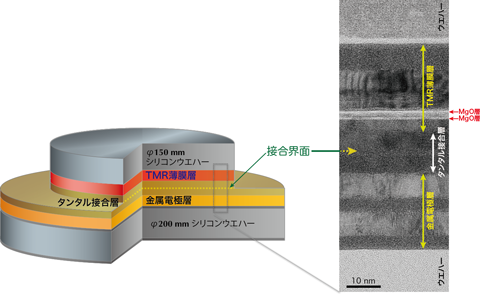

図2は、図1(B)のウエハーダイレクト接合直後の試料断面の電子顕微鏡像である。3次元積層プロセスでは、高品位のウエハー接合が重要である。図2では、接合界面の位置を矢印にて示したが、界面部分が完全に連続膜としてつながっており、欠陥や空隙がまったく無く、高品位の接合であることを示している。既存のナノメートルレベルの接合プロセスでは、タンタルのような硬質で酸化しやすい材料は用いられず、金などの柔軟で酸化しにくい材料が用いられる。しかし、今回は、タンタルの表面平坦性や活性化条件の適正化のしやすさに着眼し、厚さがナノメートルスケールの接合層同士である高品位のダイレクト接合を実現した。同時に、当初、懸念されたウエハー接合後のMgOトンネル絶縁層(図2中では赤矢印で示したTMR薄膜層内の2本の白い帯線)の破壊は回避できた。なお、タンタルはTMR素子と非常に相性が良い材料であり、タンタルを用いて高品位の接合ができたことは、MRAM製造上重要である。

|

|

図2 ウエハーダイレクト接合後の断面電子顕微鏡像 |

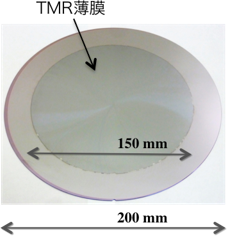

図3は、図1(C)で示したウエハー裏面研削プロセス直後の試料写真である。TMR薄膜層を完全に残しながら、TMR薄膜層よりも約1万倍厚いウエハーだけを選択的に除去するには高い技術が必要であるが、今回は、研削と化学的エッチングを併用し、機械的ダメージがTMR薄膜層に及ばないような詳細な条件を見出した。図3で示すように、TMR薄膜層(色の異なる中心直径150 mm部分)を残しながら、ウエハーは完全に除去されていることが確認できた。

|

|

図3 ウエハー裏面研削後のサンプル写真 |

一連の3次元積層プロセスにより、ウエハー上に銅電極層、タンタル接合層、多結晶TMR薄膜層の順に形成された3次元積層試料に微細加工を行い、サイズが28 nmから65 nmのMRAMデバイスを作製し、動作を確認した。比較のために、3次元積層プロセスを行わないTMR薄膜を用いたMRAMデバイスも作製して動作確認を行った。その結果、3次元積層プロセスを経た後のMRAMデバイスは、読出性能・書込性能は全く劣化せず、STT-MRAMで重要な性能指標となる「データ書き込み効率」は2に達し、世界トップクラスの性能を維持していた。ウエハー接合時の圧着荷重やウエハー裏面研磨時の摩擦など、さまざまなダメージ要因はMRAM動作には全く影響しておらず、今回開発した3次元積層プロセスによるMRAM製造の可能性が示された。

今回用いた多結晶TMR薄膜よりも単結晶TMR薄膜の方が機械的強度が強いので、今回の3次元積層プロセスは単結晶TMR薄膜にもそのまま適用できると考えられる。これが実現すれば、単結晶TMR薄膜の特徴である、原子レベルでの薄膜平坦性や薄膜均質化による性能バラツキの排除、高性能な単結晶材料の使用などのメリットが得られると考えられる。それにより、20 nm以下世代のSTT-MRAMに求められる性能マージンや性能バラツキ抑制を満たせる可能性があり、今後の飛躍的なMRAMの高容量化や、生産性向上への貢献が期待される。

現在、単結晶TMR薄膜の開発を進めている。今後2年以内に単結晶TMR薄膜とCMOSウエハーの3次元積層プロセスを確立し、5年以内に3次元積層MRAMの製品開発の着手を目指す。