独立行政法人 産業技術総合研究所【理事長 中鉢 良治】(以下「産総研」という)ナノエレクトロニクス研究部門【研究部門長 安田 哲二】シリコンナノデバイスグループ 松川 貴 上級主任研究員、昌原 明植 研究グループ長らは、立体型トランジスタ(フィンFET)の低周波ノイズをこれまでの最小レベルに低減する技術の開発を行った。

トランジスタの低周波ノイズはフリッカノイズとしても知られ、トランジスタの面積に反比例して増加するため、アナログ集積回路の縮小の妨げになっていた。また、寸法を小さくすることにより性能が向上したトランジスタをアナログ集積回路で活用する際の障害になっていた。今回、均質な状態が得られる非晶質金属ゲートを導入したフィンFETにおいて低周波ノイズを従来技術の約5分の1へ低減することに成功した。この技術によりアナログ集積回路の低コスト化につながるチップサイズ縮小と高性能化が進むと期待される。

なお、この技術の詳細は、2014年12月15~17日に米国サンフランシスコで開催される国際会議2014 International Electron Devices Meeting (IEDM2014)で発表される。

|

|

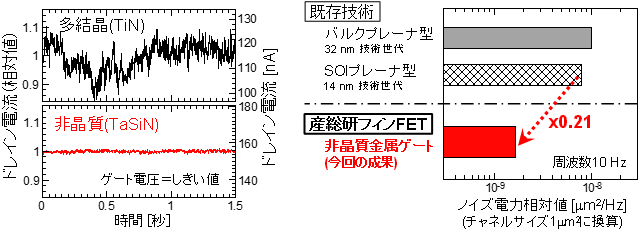

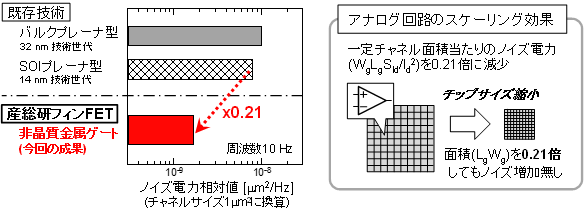

試作した非晶質金属ゲートフィンFETによるノイズ低減効果(左)と既存のデバイス技術との比較(右) |

これまで、シリコン集積回路は、その最小構成単位であるトランジスタを微細化することにより高性能化・低コスト化を実現してきた。また、近年のスマートフォンに代表される高性能な携帯用電子機器の普及は、アナログ・高周波回路も含めたシステム集積回路の高性能化・低コスト化に大きく依存している。しかしながらアナログ回路は、デジタル回路に比べ、低周波ノイズの影響を大きく受けてしまうという問題を抱えている。この低周波ノイズは、トランジスタを微細にするほど増加するため、ノイズの影響を受けずに微細化が進んでいるデジタル回路に対して、アナログ回路においてはより大きなトランジスタを使用する必要があり、コスト削減につながるチップ面積縮小と高性能化の障害になっていた。このため、アナログ集積回路向けのトランジスタにおいてノイズを格段に低減させる技術が強く求められている。

産総研は、微細化に適したフィンFETと呼ばれる新構造トランジスタの研究を推進してきた。とりわけ、デジタル回路の微細化において最大の技術課題であった特性ばらつきの問題に取り組み、2011年にはフィンFETにおけるオン電流のばらつきの主要因が金属ゲート材料の物性のばらつきであることを解明し(2011年12月8日 産総研プレス発表)、さらにゲート電極に物性ばらつきの少ない非晶質金属を用いることにより劇的にばらつきを低減させ、フィンFETとして世界最小のばらつきを実現している(2012年12月12日 産総研プレス発表)。特性ばらつきの低減は、特にデジタル集積回路の微細化・高性能化に貢献する。加えて、アナログ回路の微細化と高性能化を進めるための技術開発に取り組んできた。

なお、本研究開発は、独立行政法人 日本学術振興会より科学研究費(基盤研究B、課題番号26289113)の支援を受けて行ったものである。

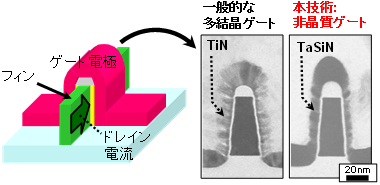

今回の技術は、特性ばらつきの抑制に有効である非晶質金属ゲートをフィンFETに導入することにより、通常の多結晶金属ゲート電極を用いる場合に比べ、低周波ノイズを劇的に低減させることに成功したものである。フィンFETのゲート電極は、一般的に多結晶金属が使用されている。図1に示すように、多結晶金属である窒化チタン(TiN)ゲート電極を持つフィンFETに加え、非晶質金属である窒化タンタルシリコン(TaSiN)をゲート電極に使用したフィンFETを作製した。非晶質金属ゲートを用いることで、トランジスタの動作を決める重要なパラメータであるしきい値電圧や相互コンダクタンスのばらつきが劇的に低減できることを既に発見しているので、今回はトランジスタのドレイン電流に生じるノイズレベルの測定と比較を行った。

|

|

図1 フィンFETの模式図(左)と非晶質金属ゲートおよび多結晶金属ゲート電極の断面電子顕微鏡写真(右) |

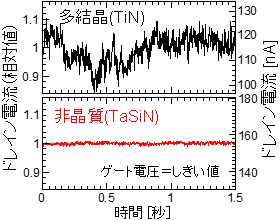

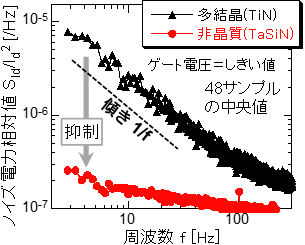

図2に、多結晶金属ゲート電極と非晶質金属ゲート電極を持つフィンFETのドレイン電流の低周波ノイズ波形を示す。多結晶金属ゲート電極においては顕著なノイズが観測されているが、非晶質金属ゲート電極においてはノイズの振幅が非常に小さく抑えられていることが分かる。図3に、ノイズを構成する周波数の分布を示す。顕著なノイズが観測された多結晶金属ゲート電極の場合、フリッカノイズ特有の周波数に反比例する特性を示している。一方、非晶質ゲート電極では、周波数に反比例する特性を示すフリッカノイズが顕著に抑制されていることが分かる。

|

|

図2 非晶質金属ゲートおよび多結晶金属ゲート電極フィンFETのノイズ波形の比較 |

|

|

図3 非晶質金属ゲートフィンFETおよび多結晶金属ゲート電極フィンFETにおけるノイズの周波数分布 |

今回達成された低周波ノイズの抑制効果を、これまで一般的に集積回路に使用されてきたバルクプレーナ型トランジスタ、フィンFET同様に低ばらつきである特長をもつSOIプレーナ型トランジスタと比較した結果を図4に示す。これらの既存トランジスタでは、多結晶金属ゲートが使用されている。異なるトランジスタ構造の公平な比較のために、同じトランジスタサイズ(チャネル面積1ミクロン四方)のノイズレベルに換算して比較を行った。非晶質金属ゲートフィンFETは、他のトランジスタ構造に比べても約5分の1程度(0.21倍)までノイズが抑制されていることが分かる。このようなノイズ抑制効果が得られると、アナログ集積回路のチップ面積を5分の1まで縮小してもノイズ増加を引き起こすことがなく、集積回路のコスト低減のメリットをもたらすと期待される。また、0.21倍の面積縮小はゲート長を約半分に縮小できることに相当し、ノイズの増加を引き起こすことなく、さらに高速動作が可能なトランジスタをアナログ回路で利用できるようになる。波及効果として、スマートフォンやタブレット等の高性能な無線端末の低コスト化や、現状よりも高い周波数動作が必要な次世代高速無線通信の普及促進が期待できる。

|

|

図4 既存のデバイス技術に対する非晶質金属ゲートフィンFETによるノイズ低減効果(左)と、アナログ回路のスケーリングへの影響(右) |

今回の技術はデバイス製造企業だけでなく、最先端トランジスタを活用したアナログ回路設計企業においても活用可能な技術であり、これらの企業への技術移転、協働も念頭に研究を推進する。今後は、フィンFETにより実現可能な非常に短いゲート長のトランジスタのアナログ・高周波回路の試作を行い、回路レベルでのメリットの実証を目指す。