独立行政法人 産業技術総合研究所【理事長 野間口 有】(以下「産総研」という)ナノエレクトロニクス研究部門【研究部門長 金丸 正剛】シリコンナノデバイスグループ 松川 貴 主任研究員、昌原 明植 研究グループ長らは、14 nm世代立体型トランジスタ(フィンFET)のオン電流ばらつきの主要因を解明した。

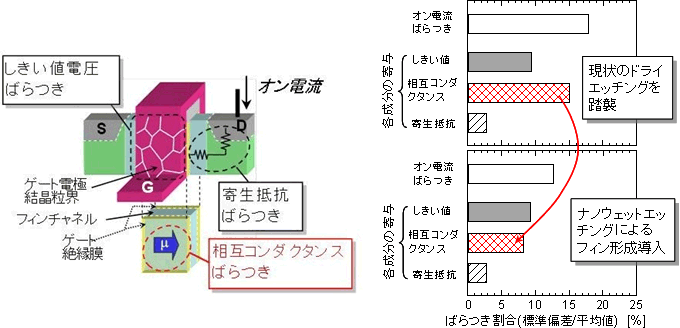

トランジスタのオン電流ばらつきの要因は、しきい値電圧ばらつき、寄生抵抗ばらつき、相互コンダクタンスばらつきである。今回、各要因の寄与を詳細に解析することで、14 nm世代のフィンFETでは相互コンダクタンスばらつきがオン電流ばらつきの主要因となることを明らかにした。また、シリコン起立型チャネル(フィンチャネル)の加工を高精度に行うと、オン電流ばらつきが低減すると予測された。さらにばらつき低減に有効なフィンチャネルの加工法を提案した。14 nm世代以降のSRAM(Static Random Access Memory)をはじめとする集積回路では、許容量を超えてオン電流がばらついたトランジスタが回路動作の不具合を引き起こし、これによって素子の歩留まりが低下することが最大の課題となっていたが、今回の成果はこの課題の解決に貢献するものと期待される。

なお、この技術の詳細は、2011年12月5~7日(現地時間)に米国ワシントンDCで開催される国際電子デバイス会議(2011 IEDM)で発表される。

|

|

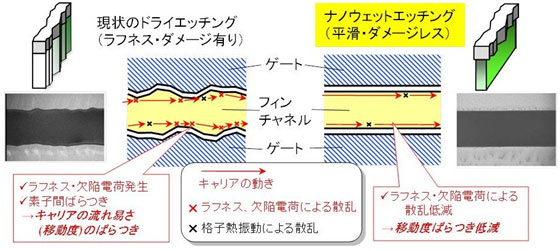

図1 立体型トランジスタのオン電流ばらつき要因(左)と、14 nm世代のばらつき予測(右) |

これまで、シリコン集積回路は、その最小構成単位であるトランジスタを微細化することで高性能化・高集積化を実現してきた。素子微細化はコスト削減にもつながるため、微細素子開発の熾烈な競争が続いている。しかし、2017年以降に市場投入が想定されている14 nm世代トランジスタ技術では、その寸法の小ささから素子間の特性ばらつきの問題が顕在化してくると考えられ、製品の著しい歩留まり低下が懸念されている。とりわけ、システムLSIやマイクロプロセッサの50%以上の面積を占めるSRAMは、最小寸法のトランジスタを多用するので特性ばらつきの影響を受けやすい。このため、特性ばらつきの少ない微細トランジスタの開発が強く求められている。

産総研は、3次元立体構造にしたフィンFETと呼ばれる新構造トランジスタの研究を推進してきた。また、素子特性を電気的に制御するための端子が付加された4端子型フィンFETを提案し、2003年に動作検証に成功している。また、2008年にはフィンFETにおける新たな特性ばらつき要因として、金属ゲート電極材料の物性のばらつきを提唱、2010年には、その物性ばらつきの低減を可能とする相補型金属酸化膜半導体(CMOS)プロセスを提唱した(2010年6月15日産総研プレス発表)。その後も継続してフィンFETの特性ばらつきを抑えるための研究開発を行ってきている。

本研究開発は、独立行政法人 新エネルギー・産業技術総合開発機構(NEDO)の委託事業「ナノエレクトロニクス半導体新材料・新構造ナノ電子デバイス技術開発(平成21~23年度)」の一環として行われている。

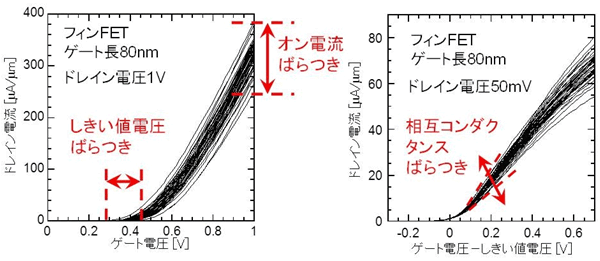

図2に、実測したフィンFETの電気的特性ばらつきを示す。ゲート長80 nm、フィン厚さ25 nm、48素子のフィンFETについて、ばらつきを評価した。集積回路の性能に直結するオン電流ばらつきの主要因としては、従来、しきい値電圧ばらつきが指摘されている。図2左にしきい値電圧ばらつきの寄与を示す。しかし、横軸をゲート電圧としきい値電圧の差として、しきい値電圧ばらつきを揃えても、図2右からわかるように、相互コンダクタンスばらつきによりオン電流ばらつきが発生している。

|

|

図2 オン電流ばらつきをもたらすしきい値電圧ばらつきと相互コンダクタンスばらつき |

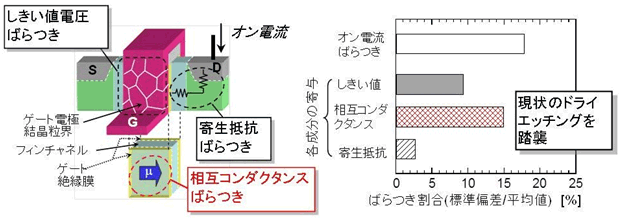

そこで、電気的特性より、しきい値電圧ばらつき、寄生抵抗ばらつき、相互コンダクタンスの3つのパラメータのばらつきを評価した。3つのパラメータ同士の相関、それぞれのオン電流との相関、素子寸法との相関を詳細に解析し、オン電流ばらつきへの3つの独立したばらつき要因の寄与率と素子寸法縮小による増加傾向予測を得ることができた。その結果、しきい値電圧ばらつきの寄与がゲート絶縁膜厚の縮小により低減できる(2010年6月15日産総研プレス発表)のに対して、相互コンダクタンスばらつきは素子微細化による低減が困難であるため、さらなる素子縮小に伴い重要な要因として顕在化し、14 nm世代のフィンFETでは、相互コンダクタンスばらつきが、オン電流ばらつきの主要因となると予測された(図3)。

|

|

図3 14 nm世代のフィンFETにおけるオン電流ばらつきの要因(左)とそれらの寄与(右) |

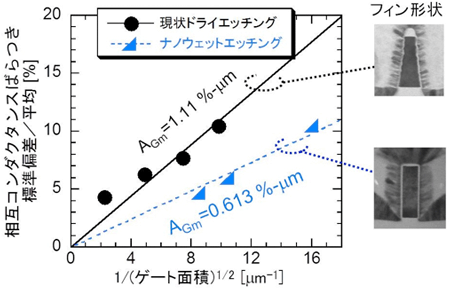

さらに、通常の加工技術(ドライエッチング技術)でフィンチャネルを形成したFETと、産総研で開発されたナノウェットエッチング技術で形成したFETについて相互コンダクタンスばらつきを測定した。図4に実測した相互コンダクタンスばらつきに関するPelgromプロットを示す。Pelgromプロットは、トランジスタ特性ばらつきの指標として広く使われており、横軸はゲート面積の平方根の逆数、縦軸は相互コンダクタンスのばらつき割合(標準偏差/平均値)を示している。プロットの傾きAGmは、ゲート寸法の縮小に対するばらつきの増加率で、このAGmが小さいほど特性ばらつきが小さく抑えられることを示す。ナノウェットエッチング技術によるシリコンフィンチャネルの高精度な加工により、相互コンダクタンスばらつきが低減されることがわかった。

|

|

図4 相互コンダクタンスばらつきの評価結果 |

図5に、ナノウェットエッチング技術による相互コンダクタンスばらつき低減のメカニズムを示す。実測された相互コンダクタンスばらつきの要因をさらに解析した結果、移動度ばらつきが主要因であることがわかった。移動度はチャネル中でのキャリアの散乱頻度により決まる。通常のドライエッチング技術によるフィン加工では、レジストの凹凸(ラフネス)を反映してフィンの側面にも凹凸が生じる。また、加工の際にプラズマによってフィンチャネルにダメージや欠陥電荷が発生する。これらはキャリアの散乱体として作用して移動度を減少させるが、従来の加工技術では素子間に散乱体の密度のばらつきが生じて、結果的に移動度のばらつきを引き起こす。一方、ナノウェットエッチング技術による加工では、フィンチャネルへのダメージがなく、また、フィンの側面は極めて平滑となる。そのため、散乱体の密度が低く抑えられ、移動度のばらつきや、それによって生じる相互コンダクタンスばらつきが抑制されていると考えられる。

|

|

図5 ナノウェットエッチング技術による相互コンダクタンスばらつき低減のメカニズム |

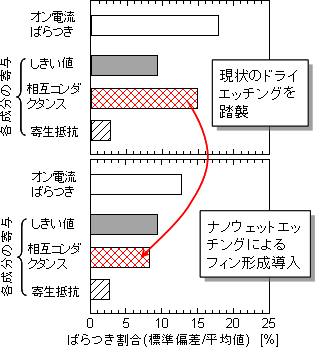

図6に、14 nm世代フィンFETのオン電流ばらつきと、各要因の寄与を予測した結果を示す。通常のドライエッチング技術を用いてフィンチャネルを作製した場合、相互コンダクタンスばらつきが主要因となり、結果として大きなオン電流ばらつきが発生するが、ナノウェットエッチング技術を用いて高精度にフィンチャネル加工を行うと、相互コンダクタンスばらつきが低く抑えられ、オン電流ばらつきが低減すると予測される。

|

|

図6 14 nm世代フィンFETのオン電流ばらつきの各要因の寄与の予測 |

今回の成果は、14 nm世代以降で深刻になるトランジスタ特性ばらつきの解決案を提示するものであり、ひいてはSRAMをはじめとする集積回路の歩留まりが低下する問題の解決に貢献できると考えられる。

今後は、フィンFETを用いた集積回路を作製し、回路レベルでの歩留まり向上の実証を目指す。