独立行政法人 産業技術総合研究所【理事長 野間口 有】(以下「産総研」という)エレクトロニクス研究部門【研究部門長 金丸 正剛】先端シリコンデバイスグループ 柳 永勛(りゅう ゆうしゅん) 主任研究員、昌原 明植 研究グループ長らは、現在、最も特性ばらつきが抑えられた22 nm世代立体型トランジスタ(フィンFET)の試作に成功した。

フィンFETの特性ばらつきの主要な原因は、チャネル不純物統計ばらつき、フィンチャネル厚ばらつき、金属ゲート電極材料の物性ばらつきである。今回、チャネル材料である純シリコンを高精度で加工可能な高異方性ナノウェットエッチングプロセスを採用することで、これらの原因を解消した相補型金属酸化膜半導体(CMOS)プロセスを開発した。さらにこの技術を用いて、特性ばらつきが最小に抑えられている22 nm世代フィンFETの試作に成功した。22 nm世代以降のSRAMをはじめとする集積回路では、素子間特性ばらつきに対する許容範囲が非常に小さいことから、ばらつきによる素子の歩留まりの低下が最大の懸念事項であるが、今回作製したフィンFETを用いれば解決できる。

なお、本研究開発は、独立行政法人 新エネルギー・産業技術総合開発機構(NEDO)委託事業「ナノエレクトロニクス半導体新材料・新構造ナノ電子デバイス技術開発(平成21~23年度)」の一環として行われた。

この技術の詳細は、2010年6月15~17日に米国ハワイ州で開催される国際会議「VLSI技術シンポジウム」(2010 Symposium on VLSI Technology)で発表される。

|

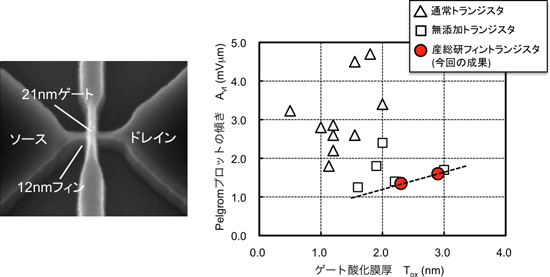

図1 試作したフィンFET(左)と、特性ばらつき強度のゲート酸化膜厚依存性(右) |

これまで、シリコン集積回路は、その最小構成単位であるトランジスタを微細化することにより高性能化・高集積化を実現してきた。素子微細化はコスト削減にもつながるため、微細素子開発の熾烈な競争が続いている。しかし、2013年以降に市場投入が想定されている22 nm世代トランジスタ技術では、その寸法の小ささから素子間の特性ばらつきの問題が大きく顕在化してくると考えられており、製品の著しい歩留まり低下が懸念されている。とりわけ、システムLSIやマイクロプロセッサの50 %以上の面積を占めるSRAMでは、最小寸法のトランジスタを多用するため、特性ばらつきの影響を受けやすい。このため、特性ばらつきの少ない微細トランジスタの開発が強く求められている。

産総研とその前身である工業技術院 電子技術総合研究所は、素子寸法を縮小しても性能劣化を起こさない2重ゲート電界効果型トランジスタ(XMOSFET)を、1984年に世界に先駆けて提案し、3次元立体構造にしたフィンFETと呼ばれる新構造トランジスタの研究を推進してきた。また、素子特性を電気的に制御するための端子が付加された4端子型フィンFETを提案し、2003年に動作検証に成功している。また、2008年にはフィンFETにおける新たな特性ばらつき要因として、金属ゲート電極材料の物性のばらつきを提唱した。その後もフィンFETの特性ばらつきを抑えるための研究開発を継続している。

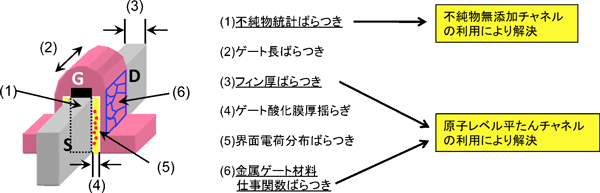

22 nm世代に実用が見込まれているフィンFETの特性ばらつき(具体的には、しきい値電圧のばらつき) の低減を目指して、今回新たな22 nm世代フィンFET作製プロセスを開発した。図 2に特性ばらつきの要因を示すが、この中で主な要因と考えられているのは、チャネル不純物の統計ばらつき、フィンチャネル厚ばらつき、金属ゲート電極材料の物性(仕事関数)ばらつきがある。

|

図2 フィンFETの特性ばらつきの主要な原因(下線)と今回用いた解決法 |

まず、チャネル不純物の統計ばらつきを完全に除去するため、チャネル材料として不純物無添加の純シリコンを用いた。通常のトランジスタの場合、チャネル中に不純物を添加することで短チャネル効果の抑制を行っているが、フィンFETでは立体チャネルをゲートが覆う構造にすることで短チャネル効果を抑制できるため、不純物を添加しないチャネル材料の利用が可能となる。

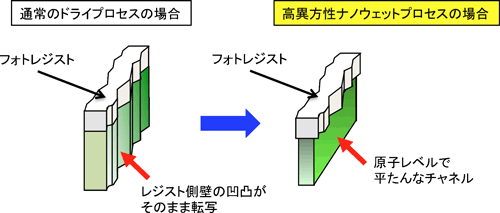

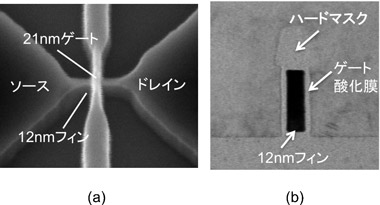

次にフィン厚ばらつきを抑制するため、チャネル形成時のプロセスに、高異方性ナノウェットエッチングプロセスを用いた。このプロセスは、シリコン(ケイ素:Si)の結晶面によってエッチングの速度が異なる性質を利用する異方性ウエットエッチングという方法を応用したものである。通常のドライエッチングプロセスでは、フォトレジストのマスクの側壁に凹凸があった場合、その凹凸はそのままSiチャネルに転写されてしまうが、今回用いた高異方性ナノウェットエッチングプロセスでは、凸部分のエッチングされる速度が速く、結果的に先に凸部分がなくなっていく。すなわち、自己修復的に側壁が平たん化されるので、原子レベルで平たんな側壁が形成される(図 3)。図 4に今回試作した22 nm世代フィンFETの上面電子顕微鏡像とフィン断面電子顕微鏡像を示す。高異方性ナノウェットエッチングプロセスにより、平たん性の高い側壁チャネルが形成されていることがわかる。

さらに、この原子レベルで平たんな側壁は、フィンFETの特性ばらつきにおいて最も大きな要因である金属仕事関数ばらつきの抑制にも効果を発揮する。通常のドライエッチングプロセスで形成されたフィンチャネル側壁にはミクロな凹凸が存在する。このミクロな凹凸の上に金属を堆積した場合、凹凸に伴い堆積が様々な方向に進行するため、結果として金属ゲート電極材料の仕事関数に大きなばらつきを発生させてしまう。しかし、原子レベルで平たんなチャネル側壁であれば、金属が一様に堆積されるため、金属ゲート電極材料の仕事関数ばらつきを極限まで低減させることができる。

|

図3フィンチャネル形成時における、通常のドライエッチングプロセスと高異方性ナノウェットエッチングプロセスの違い |

|

図4 試作したフィンFET上面の走査型電子顕微鏡像(a)、フィンチャネル断面の透過型電子顕微鏡像(b) |

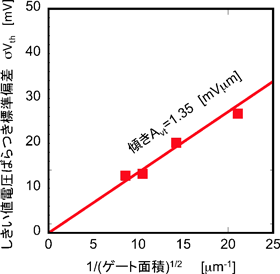

図 5に、今回試作したフィンFETのPelgromプロットを示す。このプロットはトランジスタ特性ばらつきの指標としてよく用いられ、横軸はゲート面積の平方根の逆数、縦軸はあるゲート面積におけるトランジスタ群のしきい値電圧の標準偏差(ばらつき)を示している。この図の傾きは通常Avtと定義されており、Avtが小さければ小さい程、特性ばらつきがよく抑えられていることを意味する。

|

図5 今回試作したフィンFET群のPelgromプロット |

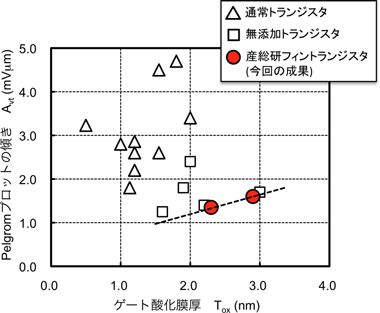

図6に、これまで学会で発表されているAvt値と、今回試作したフィンFETのAvtを比較した結果を示す。今回試作したフィンFETでは、通常タイプのトランジスタに比べてAvtが劇的に改善されている。また、同じように不純物無添加チャネルを用いたトランジスタと比べても、同程度以下のレベルであった。これらの結果は、今回開発したフィンFETとその作製プロセス技術が、22 nm世代以降の集積回路の有力な候補であることを示している。

|

図6 今回開発したフィンFETのPelgromプロットの傾きと学会報告値との比較

フィンFETが、同一の酸化膜厚では最小値を示している。 |

今回の成果は、22 nm世代以降で深刻になるトランジスタ特性ばらつきの解決案を提示するものであり、ひいてはSRAMをはじめとする集積回路の歩留まりが低下する問題の解決につながると考えられる。今後は、フィンFETを用いた集積回路を作製し、回路レベルでの歩留まり向上の実証を目指す。