国立研究開発法人 産業技術総合研究所【理事長 中鉢 良治】(以下「産総研」という)ナノエレクトロニクス研究部門【研究部門長 安田 哲二】Wen Hsin Chang 産総研特別研究員、3D集積システムグループ 入沢 寿史 主任研究員、同研究部門 前田 辰郎 研究主幹らは、シリコン(Si)の性能を凌駕する材料として有望視されているゲルマニウム(Ge)の膜厚10 nm以下の均一な超薄膜構造の作製法を開発した。さらにこのナノメートルレベルの均一なGe超薄膜を絶縁膜で挟むと、Ge超薄膜中の電子移動度が著しく向上することを発見した。これは、絶縁膜で挟まれた5 nm以下の半導体薄膜では、界面の不均一性や半導体薄膜の膜厚揺らぎの影響によって電子移動度が著しく減少するという、従来の半導体の常識を覆す現象である。

Geは、従来の大規模集積回路(LSI)で用いられているSiに比べて移動度が高く、より低電圧で多くの電流を流すことができることから、SiをGeに置き換えることでLSIの高速化が可能になる。今回、半導体転写技術の高度化により、絶縁膜に挟まれた10 nm 以下の超薄膜Ge構造を作製できたことは、高速性と消費電力低減が期待されるGeのLSI(Ge-LSI)実現の大きな一歩となる。さらに、今回発見したGe超薄膜の電子移動度が急激に向上する現象は、高性能超低消費電力Ge-LSI実現だけではなく、新たな電子・光デバイスへの応用展開も期待される。

なお、この技術の詳細は、6月5~8日に京都で開催される2017 VLSI Technology シンポジウムで発表される。

|

|

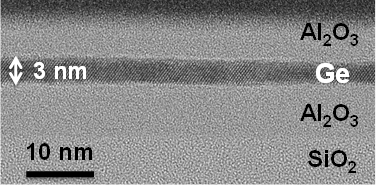

超薄膜Ge構造断面の透過電子顕微鏡像 |

携帯情報端末の普及や、IT機器の高機能化に伴う消費電力の増大により、電子情報機器の消費電力低減が求められている。そのためには、搭載されているLSIを構成する個々のトランジスタの動作電圧の低減が有効である。これまでトランジスタを微細化することで動作電圧は徐々に下げられてきたが、これまでLSIで使われていたSiの物性の物理的限界に近づいてきており、近年は1 V程度で停滞している。そこで、Siより電子や正孔の移動度が高く、低電圧で動作するGeを用いた微細なトランジスタの研究開発が進められている。

Geはトランジスタ現象が初めて観測された半導体として知られている。長い間トランジスタには、集積化が容易なことからSiが用いられてきたが、2000年ころからGeの本質的に高いトランジスタ性能が再評価されだしている。産総研では、高性能Geトランジスタの研究を、国立研究開発法人 新エネルギー・産業技術総合開発機構「次世代半導体材料・プロセス基盤(MIRAI)プロジェクト(平成13~22年度)」にて開始し、独立行政法人 日本学術振興会「最先端研究開発支援プログラム(FIRST)(平成21~25年度)」、同事業で設置した連携研究体グリーン・ナノエレクトロニクスセンターを経て、現在はナノエレクトニクス研究部門で行っている(産総研プレス発表 2011年9月27日、産総研プレス発表 2014年6月9日)。その間、Geトランジスタ高性能化に向けた各要素技術は着実に進歩してきたが、当初実用化を期待された時期は後ろ倒しされている。高品質の単結晶Ge薄膜の形成が難しいことがその大きな要因であり、産総研では、独自の低温貼り合せ技術と高度な半導体転写法を用いた高品質Ge薄膜の形成技術を開発してきた。

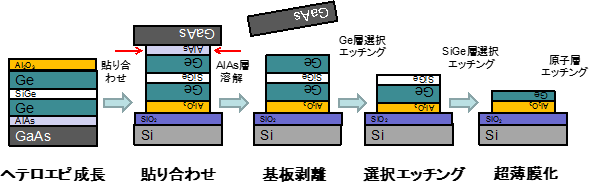

今回、半導体転写技術を高度化することによって、膜厚10 nmというGeの単結晶薄膜を作成する方法を開発した。図1に今回開発した超薄膜Ge構造の形成法、HEtero-Layer Lift-Off (HELLO)法の概要を示す。まず、ヒ化ガリウム(GaAs)基板上に剥離層となるヒ化アルミニウム(AlAs)層を形成し、その上に高品質の超薄膜ゲルマニウム/シリコンゲルマニウム/ゲルマニウム(Ge/SiGe/Ge)の複層膜構造をヘテロエピタキシャル成長させる。SiGe層は後述の選択エッチングプロセスでのエッチングストップ層となる。ここで、AlAs層やSiGe層のように化学的な性質は大きく異なるがGe結晶の格子とは一致した結晶を成長させることがポイントとなる。その後、酸化アルミニウム(Al2O3)絶縁膜を堆積させた。剥離層であるAlAs層を露出させるためにAl2O3/Ge/SiGe/Ge/AlAs層を部分的にエッチングした後、二酸化ケイ素(SiO2)膜を付けたSi基板と貼り合わせる。剥離層であるAlAs層だけを薬液により溶解してGaAs基板を剥離すると、Al2O3/Ge/SiGe/Ge層が転写されたSi基板が得られる。さらに転写されたGe/SiGe/Ge層のうち上側のGe層とSiGe層を選択エッチングして順次取り除くと、絶縁膜上に均一な超薄膜Ge構造ができる。最終的には、この超薄膜Ge構造を、原子層レベルで繰り返しエッチングすることで精密に膜厚を制御する。

|

|

図1 超薄膜Ge構造の形成プロセス |

この超薄膜Ge構造の断面透過電子顕微鏡像を図2に示す。上下のAl2O3絶縁膜で挟まれた明瞭なGe格子像が観察されており、緻密な膜厚制御手法によりそれぞれ(a)3 nmと(b)9 nmの均一な単結晶Ge超薄膜が形成されている。なお、図2はトランジスタ試作後の写真で、下部にはSiO2膜を付けたSi基板、上部には窒化タンタル(TaN)の金属ゲート電極層がある。

|

|

図2 超薄膜Ge構造断面の透過電子顕微鏡像 |

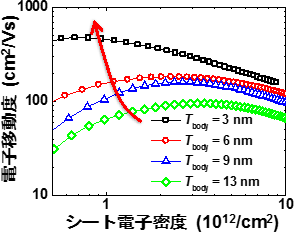

また、単結晶Ge超薄膜の膜厚13 nmから3 nmにおける電子移動度のシート電子密度依存性を確認すると、13 nmから3 nmに薄膜化するにつれて電子移動度が急激に上昇する現象が見られた(図3)。シート電子密度5x1012 cm-2で、移動度は2.5倍にまで増加している。従来、絶縁膜で上下を挟まれたSiやGeといった半導体薄膜では、上下の絶縁層と半導体薄膜の界面の不均一性や、半導体薄膜の膜厚揺らぎの影響が大きくなるため、5 nm以下の膜厚では電子移動度が著しく減少することが報告されていたが、今回の発見はこれまでの常識を覆す結果と言える。

|

|

図3 超薄膜Ge層における電子移動度のシート電子密度依存性 |

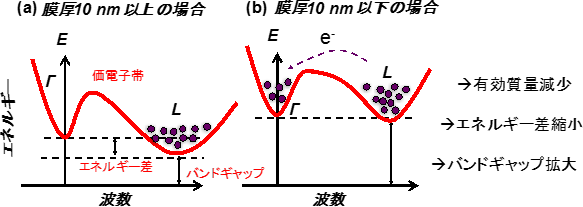

今回発見した現象は、ナノ構造化に伴い、超薄膜Ge構造では単結晶Geと比較してエネルギーバンド構造が大きく変化したためと考えられる。これは第一原理計算によると、10 nm以下のGe構造は量子構造化し、電子が(001)の結晶軸方向に閉じ込められると、電子が選択的に占有するL谷の有効質量が大幅に減少すること、また、有効質量の小さなΓ谷とのエネルギー差が縮小し、Γ谷の電子占有率が上昇することが予測されている(図4) 。その結果、電子の伝導に寄与する有効質量が小さな電子が増加して電子移動度が向上すると考えられる。今回の発見は、この第一原理計算の予測を支持する初めての実験結果である。

|

|

図4 Ge薄膜のエネルギーバンド構造((a)膜厚10 nm以上、(b)膜厚10 nm以下) |

Geの超薄膜化によるエネルギーバンド構造の変調は、電子、正孔といったキャリアの輸送特性に大幅な変化をもたらす。この特性は、超低消費電力LSIへの貢献だけではなく、新たな量子効果デバイスや光デバイスへの応用も期待されるものである。

今回の成果は、Ge-LSI実現に向けて大きな契機となるものであるが、その物理的なメカニズムなどはまだ未解明であり、さらなる移動度の向上も期待できる。今後2年以内により精度の高い薄膜化プロセスを確立し、移動度向上を実証するとともにそのメカニズムを解明する。また、3年以内に民間企業などへの技術移転を目指す。