独立行政法人 産業技術総合研究所【理事長 中鉢 良治】(以下「産総研」という)ナノエレクトロニクス研究部門【研究部門長 安田 哲二】新材料・機能インテグレーショングループ 前田 辰郎 主任研究員らは、大規模集積回路(LSI)の消費電力低減に有効な、インジウムガリウムヒ素(InGaAs)n型MOSFET(nMOSFET)とシリコンゲルマニウム(SiGe)p型MOSFET(pMOSFET)により構成される3次元積層CMOSリングオシレーター回路を試作し、その回路動作に成功した。

ポストシリコン材料と呼ばれるInGaAsやSiGeは、従来のLSIで用いられているシリコン(Si)に比べ、より低電圧で多くの電流を流すことができる。そのため、これらのポストシリコン材料を組み合わせたデュアルチャネルCMOS回路は、高速性などの性能を維持したままで、大幅な消費電力低減が期待できる。今回、InGaAs-nMOSFETとSiGe-pMOSFETの双方に、高速性と省電力に優れた絶縁膜上の細線チャネル構造を採用して高性能化し、はり合わせによる3次元集積化技術を用いて、省スペース化されたCMOSリングオシレーター回路を作製した。この回路により低電圧動作(電源電圧0.37 V)を実証した。今回の成果により、低炭素社会を実現するための次世代超低消費電力LSIの実現が期待される。

なお、本成果は2014年6月10~12日(現地時間)に米国ハワイ州ホノルルで開催される2014 VLSI Technology シンポジウムで発表される。

|

|

InGaAs-nMOSFET/SiGe-pMOSFET 3次元積層CMOSの断面電子顕微鏡像 |

携帯情報端末の爆発的な普及やIT機器の高機能化に伴って電子情報機器の消費電力が増大している。電子情報機器の消費電力低減のためには、これらに搭載されている大規模集積回路(LSI)に供給される電源電圧を低減することが極めて有効である。これまでも電源電圧は徐々に下げられてきていたが、近年、低減ペースは鈍化して1 V程度となっている。これは、トランジスタを構成するシリコンの物性の限界や平面型トランジスタの構造的限界によるものである。そこで、低電圧で動作するポストシリコン材料を用い、Fin構造や細線構造など立体的なトランジスタ構造を採用したCMOS回路の研究開発が活発化している。

産総研 ナノエレクトロニクス研究部門では、連携研究体 グリーン・ナノエレクトロニクスセンター 新材料・新構造CMOS開発グループの手塚 勉 研究分担者、入沢 寿史 特定集中研究専門員(ともに現在は株式会社東芝)らと共同でLSIの低消費電力化と高性能化の両立を目指しSiGeやInGaAsを用いたMOSFETに関する研究開発を行ってきた。今回、トランジスタ構造の高度化により、回路のさらなる性能向上を目指した。

なお本研究開発は、総合科学技術会議により制度設計された、独立行政法人 日本学術振興会の最先端研究開発支援プログラム(FIRST)の助成を受けて行った(平成22年度から平成25年度)。

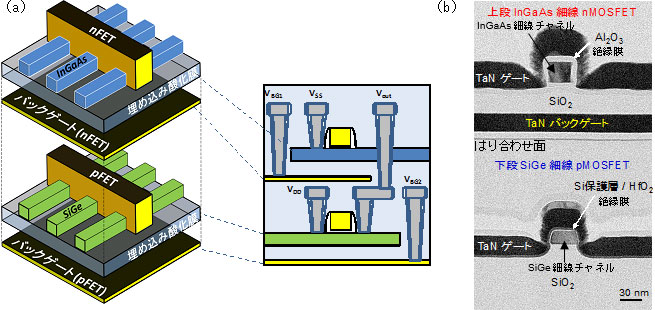

図1に今回試作したInGaAsとSiGeを用いた3次元積層CMOSの模式図と断面図を示す。上段のInGaAs-nMOSFETと下段のSiGe-pMOSFETは、双方とも絶縁膜上に形成された幅30 nm程度の細線チャネル型MOSFETである。精密な3次元積層化により上下のMOSFETは10 nm程度の精度で位置合わせされ、回路面積の縮小化と近接配線による高性能化が期待される。なお、SiGeの細線チャネルは酸化濃縮法により形成し、チャネル表面のGe組成は70 %以上と高濃度である。一方、InGaAsの細線チャネルは、下段のSiGe-pMOSFETの作製後、InGaAs層をはり合わせ、エッチング加工して形成した。また、InGaAs-nMOSFETの下部に形成されたTaNバックゲート層は、InGaAs層をはり合わせる前に、SiGe-pMOSFET上に絶縁膜を介して堆積させた。これら上下段のMOSFETを図1aの模式図のように配線することにより、CMOS回路を作製した。

|

|

図1 InGaAsとSiGeを用いた3次元積層CMOSの模式図(a)と試作したデバイスの断面図(b) |

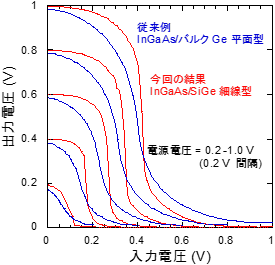

図2に、InGaAsとSiGeを用いて作製したCMOSインバーターと、従来のGe基板を用いた平面型InGaAs/Ge-CMOSインバーターの伝達特性を示す。絶縁膜上の細線チャネル構造により、個々のMOSFETのソース/ドレイン間のオフリーク電流が抑制され、伝達特性が急峻となり、低電圧下でも正常な回路動作が可能となった。

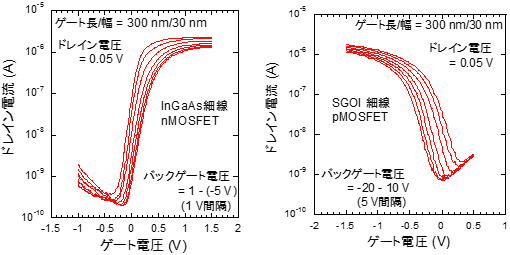

図3に、InGaAs-nMOSFETとSiGe-pMOSFETのカットオフ特性とバックゲート電圧依存性を示す。細線チャネル型であるため、どちらのMOSFETもドレイン電流のオンオフ比が3桁以上となり、消費電力の低減が図られた。また、各トランジスタに形成したバックゲート電圧を変化させることで、しきい値電圧を制御できることもわかる。バックゲート電圧によって、それぞれのMOSFETのしきい値電圧を独立に制御できることは、回路全体の低消費電力化に寄与する。

|

|

図2 InGaAsとSiGeを用いた3次元積層CMOSインバーターの伝達特性 |

|

|

図3 InGaAsとSiGeを用いた3次元積層CMOSのカットオフ特性とバックゲート電圧依存性 |

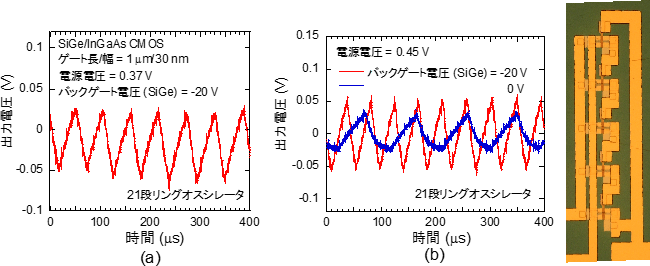

今回開発したInGaAsとSiGeを用いた3次元積層CMOSインバーターを用いて、代表的なダイナミックデジタル回路であるCMOSリングオシレーターを試作した。図4に21段CMOSリングオシレーターの出力特性とリング状に接続された5段リングオシレーターの顕微鏡像を示す。電源電圧0.37 Vという低電圧でのリングオシレーター動作を確認した(図4a)。これはインバーター伝達特性が良好で、素子間の特性が均一なことによると考えられる。また、−20 Vのバックゲート電圧をかけると、発振周波数が増加することが確認された(図4b)。

このようなバックゲート電圧をかけることによるCMOS性能・消費電力の変調は消費電力制御に有用であり、今回開発した3次元積層CMOS回路は、超低消費電力を実現するデュアルチャネルCMOS構造として有望である。

|

|

図4 InGaAsとSiGeを用いた3次元積層CMOSで試作したリングオシレーターの出力特性と顕微鏡像 |

今後もポストシリコン材料を用いた3次元積層CMOSの開発を進め、LSIのさらなる高性能、低消費電力化を目指す。また、はり合わせ技術を応用して、これまでシリコンでは困難であった発光や受光デバイスなどと3次元集積し、LSIとポストシリコンデバイスをワンチップ化した、多機能集積化デバイスの開発を目指す。