内閣府 総合科学技術・イノベーション会議が主導する革新的研究開発推進プログラム(ImPACT)[プログラム・マネージャー:佐橋政司]の一環として、株式会社東芝 研究開発センター【所長 堀 修】の藤田 忍 研究主幹、国立研究開発法人 産業技術総合研究所【理事長 中鉢 良治】(以下「産総研」という)スピントロニクス研究センター【研究センター長 湯浅 新治】の野崎 隆行 研究チーム長らの研究開発チームは、電圧駆動型の不揮発性磁気メモリ「電圧トルクMRAM」(注1)の書き込みエラー率(注2)を低減する新しい書き込み方式を開発しました。

本研究開発チームはこれまで、高速パルス電圧によって磁化反転(注3)を制御可能な磁気トンネル接合素子(MTJ素子)(注4)を開発し、電圧駆動型の新しい磁気メモリ「電圧トルクMRAM」の実現に取り組んできました。電圧トルクMRAMでは、従来の電流駆動型磁気メモリ(STT-MRAM(注5))と比較して飛躍的な低駆動電力化が期待されていますが、書き込みエラー率の低減が実用化に向けた重要課題となっています。 今回、書き込み時に印加するパルスの前後に書き込みとは逆極性のパルス電圧を印加することにより、熱ゆらぎによる書き込み失敗の発生を抑制して書き込みエラー率を低減する手法、およびそれを実現する新しい書き込み用回路を開発しました。この成果により、プロセッサ用ラストレベルキャッシュ(注6)の大容量化と、それによるプロセッサの高性能化・低消費電力化が期待されます。

この成果の詳細は、2016年12月7日に、米国サンフランシスコにて開催される半導体国際会議International Electron Devices Meeting (IEDM:会期12月3日~7日)にて技術発表されます。また、本研究成果は2016年12月3日13時30分(米国太平洋標準時間(PST))発行予定の「IEDM 2016 Technical Digest」に掲載されます。

本成果は、以下のプログラム・研究開発課題によって得られました。

内閣府革新的研究開発推進プログラム(ImPACT)

プログラム・マネージャー : 佐橋 政司

研究開発プログラム : 無充電で長期間使用できる究極のエコIT機器の実現

研究開発課題 : 電圧駆動MRAM のための回路設計

研究開発責任者 : 藤田 忍(株式会社 東芝 研究開発センター 研究主幹)

研究期間 : 平成28年度~平成30年度

研究開発課題 : 電圧駆動MRAMのための新材料素子の開発

研究開発責任者 : 野崎 隆行(国立研究開発法人 産業技術総合研究所 スピントロニクス研究センター 電圧スピントロニクスチーム 研究チーム長)

研究期間 : 平成28年度~平成30年度

研究開発課題 : 電圧駆動MRAMのプロセス技術およびメモリアレイの開発

研究開発責任者 : 湯浅 新治(国立研究開発法人 産業技術総合研究所 スピントロニクス研究センター 研究センター長)

研究期間 : 平成28年度~平成30年度

本研究開発課題では、電圧駆動MRAM実現のためのメモリの動作実証と電圧制御用の回路開発、および材料・プロセス技術の開発に取り組んでいます。

ImPACT「無充電で長期間使用できる究極のエコIT機器の実現」では、究極の超低消費電力かつ高記憶密度の不揮発性メモリの実現に挑戦し、電圧書き込み方式の不揮発性磁気メモリ「電圧駆動MRAM」の研究開発に取り組んでいます。今回、株式会社 東芝と産総研の研究開発チームは、電圧トルクMRAMの物理に立脚した新たな電圧駆動書き込み方式とそれを実現する回路を開発しました。また、併せて開発した「電圧駆動に必要な高抵抗MTJ素子に適した新たな高速読み出し回路」を用い、電圧トルクMRAMの性能を、実際に作製したメモリ素子の実測データをもとに、先端CMOS(注7)の回路シミュレーションにより示し、1~2 Gbit(ギガビット)の大容量のラストレベルキャッシュへの電圧トルクMRAMの適用可能性を明らかにしました。本研究開発成果は、究極の省電力メモリである「電圧駆動MRAM」の実用化を目指すにあたって大きなインパクトある成果です。

本成果は2016年12月3日から米国サンフランシスコで開催されるInternational Electron Devices Meetingで技術発表されますが、本研究開発成果を弾みに、実用化につなげる課題の克服に産官学連携で取り組み、市場展開に向けた活動を一層加速したいと考えています。

IT機器の低消費電力化は、社会生活を豊かにしながら地球環境を維持する上で極めて重要な課題となっています。エレクトロニクスの分野においてそれを実現するキーテクノロジーとして注目されているのが、情報維持に電力を必要としない"不揮発性"メモリです。スピントロニクス(注8)分野では、磁石が有する不揮発性を利用した、不揮発性磁気メモリ「MRAM」の開発が進められており、大容量性、高速性、高い耐繰り返し動作性を満たし得る唯一の不揮発性メモリとして期待されています。しかし、現状の磁気メモリは、磁気トンネル接合素子(MTJ素子)への電流通電により情報書き込み(磁化反転)を行う"電流駆動型"であるため、半導体メモリと比べて書き込み時の消費電力が大きいことが課題となっています。この問題を抜本的に解決するために本研究開発チームは、ImPACTプログラム「無充電で長期間使用できる究極のエコIT機器の実現(プログラム・マネージャー 佐橋政司)」において、待機電力ゼロの不揮発性メモリMRAMのうち、書き込み時の消費電力が極めて小さい"電圧駆動型"である「電圧トルクMRAM」の開発に取り組んでいます。

本研究開発チームは、これまでに非常に薄い金属磁石薄膜に電圧をかけることで、磁化の向きやすい方向(磁気異方性(注9))を制御する技術(電圧磁気異方性制御)と、それを用いた新しい磁化反転制御法の開発に取り組んできました(2015年12月10日 産総研プレス発表「電圧書き込み方式不揮発性メモリの安定動作の実証と書き込みエラー率評価」参照)。電圧トルクMRAMの実用化において特に重要となるのが、情報書き込みに失敗する確率(書き込みエラー率)をいかに小さくするかです。上記のプレス発表では、実用化の目処となるエラー率10-10~10-15を実現するための材料設計の指針を示し、現在ImPACTプログラムにて指針に沿った材料開発を進めています。

一方、今回本研究開発チームは、書き込み時のパルス電圧の形状を工夫することにより疑似的に材料特性を向上させて書き込みエラー率を低減する手法の開発、ならびにそれを実現する回路設計を行いました。

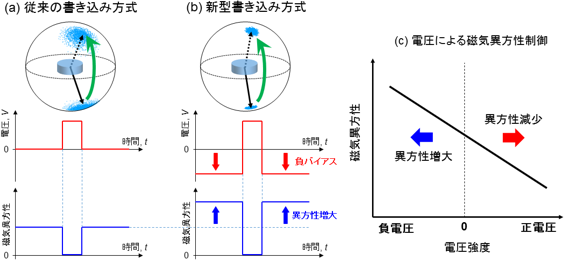

図1に電圧書き込みの(a)従来方式、および(b)新方式の模式図を示します。図1(a)において、電圧をかけていないとき、磁化は磁気エネルギーの低い下向き(もしくは上向き)として安定し、1ビットの情報が不揮発に保存されています。ここに正の電圧パルスをかけると、瞬間的に磁気異方性がゼロとなることにより磁化が回転運動を始めます。ちょうど磁化が初期状態と反対向きになった時にパルス電圧を切ると、反対側の安定点である上向き(もしくは下向き)に磁化が反転し、情報が書き込まれます。これが電圧による磁化反転(情報書き込み)の基本動作となります。ここで、磁化反転が起きる前の初期状態(始状態)、および反転後の終了状態(終状態)において熱エネルギーの影響によって磁化の向きが揺らいでいます(熱揺らぎ)。この揺らぎが大きいほど、正確な反転が行えずに書き込みに失敗する確率(書き込みエラー率)が増大してしまいます。つまり、始状態および終状態における磁化の熱揺らぎをいかに抑制するかが、書き込みエラー率を低減するための鍵となります。

この熱揺らぎを小さくするには、磁気異方性の大きい金属磁石材料を用いて熱エネルギーに対する磁化の安定性を高めることが基本となりますが、金属磁石材料の改良だけでは限界がありました。

|

| 図1 電圧パルスによる磁化反転の模式図 |

| (a) 従来のパルス電圧による書き込み方式。黒矢印はMTJ素子の金属磁石層の磁化の向き。パルス電圧印加により磁気異方性が減少し、磁化が下向きから上向きに反転する。熱エネルギーによって始状態と終状態の磁化の向きが水色の領域で揺らいでおり、これが書き込み失敗の原因となる。(b) 新型書き込み方式。書き込み前後に逆極性の電圧をかけることにより金属磁石層の磁気異方性を増大させ、揺らぎを抑制することにより書き込みエラー率を低減する。(c) 電圧による磁気異方性変化の概念図 |

今回本研究開発チームが新たに開発した手法では、電圧を用いて疑似的に垂直磁気異方性を増大させて書き込みエラー率を低減します。図1(c)は電圧による磁気異方性変化の模式図です。通常電圧に対して磁気異方性は線形に変化するため、正電圧では磁気異方性が小さくなるのに対し、負電圧では逆に大きくなります。従来の電圧書き込みでは、正の電圧パルスをかけることによって磁気異方性が小さくなることのみを利用して磁化反転を行っていました。一方、新手法では図1(b)に示すように磁気異方性が大きくなる負の電圧を始状態と終状態で加えることによって、始状態と終状態における磁化の熱揺らぎを抑制し、書き込みエラー率を大幅に改善可能であることが分かりました。

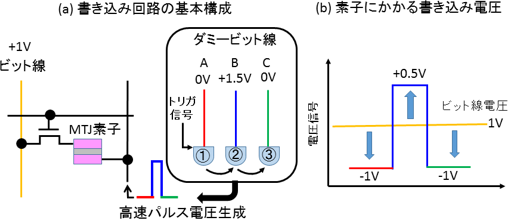

ただし、上述のような効果を実現するためには、1ナノ秒程度のパルス幅と数100ピコ秒程度の急峻な極性反転を有するパルス電圧をメモリアレイ内の個々の素子に正確にかける必要があります。従来の磁気メモリ用書き込み回路では、配線の充・放電に時間がかかるためパルス電圧の波形の立ち上がり、立ち下がり時間がなだらかなものに変化してしまい(波形のなまり)、かつ電圧の極性を高速に切り替えることも困難であるため、正確に形状制御された高速パルス電圧を生成することは困難でした。そこで今回、極性反転を伴う高速パルス電圧を生成できる電圧トルクMRAM専用の書き込み回路を新たに開発しました。図2(a)にその概念図を示します。高速に切り替えた3段階のパルス電圧を3本の配線(ダミービット線A、B、C)にあらかじめかけておきます。この各配線は書き込みの命令(トリガ信号)に対してループ構造となっており、前の信号を受けて次の信号が発生する、つまりA⇒B⇒Cの順で連続して素子にかかるように工夫されています。これにより書き込みパルス電圧を遅延やなまりが無く高速で正確に制御することが可能となります。図2(a)は、A:0V、B:1.5V、C:0Vとした例ですが、これにより非常に急峻に立ち上がり(立ち下がり)、かつ幅の短い1.5Vのパルス電圧を生成することができます(A、Cを0V以外に設定することも可能)。ここで逆側のビット線に例えば1Vの電圧をかけていると、素子に実効的にかかる電圧信号は-1V⇒0.5V⇒-1Vとなり、極性反転を伴う高速パルスを正確にかけることが可能となります(図2(b))。

|

| 図2 電圧トルクMRAM用書き込み回路の概念図 |

| (a) 極性反転を伴う高速パルス電圧を生成する回路。あらかじめ所定の電圧に設定されたダミービット線からの供給電圧をループ構成として①⇒②⇒③と切り替えることで高速パルス電圧を生成する。(b) ビット線側に印加された電圧との相対関係により素子には極性反転を伴う高速パルス電圧がかかる。 |

さらに、逆極性のパルス電圧を印加している間に読み出しを同時に行うことで、無駄なメモリ回路の動作を省くことが可能です。これにより、初期状態の記録情報を読み出して、情報を書き込む必要が無い場合には書き込みプロセスをスキップし、書き込み後に記録情報を再度確認し、書き込みエラーが発生していた場合には再度書き込み行うという「Verifyと呼ばれるエラー訂正プロセス」が高速で動作可能となります。これらのエラー率の低減手法を組み合わせることにより、実用化の目標となるエラー率10-10~10-15の達成を可能とします。

また、本研究開発では書き込みエラー率の低減以外にも、電圧トルクMRAM用の高抵抗MTJ素子でも情報読み出しを容易に行うために、読み出し電圧に対してMTJ素子の抵抗が変化する現象を活用した新しい読み出し回路も併せて開発しました。

実際に作製した直径30ナノメートルのメモリ素子における実測データをもとに書き込み・読み出しのエラー率が大幅に改善されることを先端CMOSの回路シミュレーションにより示し、現状の3倍程度の電圧磁気異方性制御の効率が実現されれば1~2 Gbitと大容量のラストレベルキャッシュへの適用が可能であることが明らかとなりました。

今後は、今回得られた指針をもとに、大容量のラストレベルキャッシュ、もしくはさらに大容量のメインメモリにおける仕様を満たす電圧磁気異方性制御を数十ナノメートルの実MTJ素子において実証することを目指すとともに、より高品質な回路システム設計を進めます。