独立行政法人 産業技術総合研究所【理事長 野間口 有】(以下「産総研」という)ナノエレクトロニクス研究部門【研究部門長 金丸 正剛】連携研究体グリーン・ナノエレクトロニクスセンター(以下「GNC」という)横山 直樹 連携研究体長、中払 周 特定集中研究専門員ら、ナノエレクトロニクス研究部門 小川 真一 招聘研究員らは、産総研ナノデバイスセンター【センター長 秋永 広幸】、独立行政法人 物質・材料研究機構【理事長 潮田 資勝】(以下「物材機構」という)国際ナノアーキテクトニクス研究拠点【拠点長 青野 正和】(以下「WPI-MANA」という)塚越 一仁 主任研究者らと共同で新しい動作原理のグラフェントランジスタを開発した。

今回開発したトランジスタでは、グラフェン上に2つの電極と2つのトップゲートを置き、トップゲート間のグラフェンにヘリウムイオンを照射して結晶欠陥を導入した。2つのトップゲートに独立した電圧をかけて、効率的に電荷の動きを制御できる。200 K(約-73℃)で、約4桁の電流オン・オフ比を示した。さらにトランジスタ極性を電気的に制御して反転させることができるが、これまで、このような動作が可能なトランジスタはなかった。この技術は、既存のシリコン集積回路の製造技術の中で利用でき、将来の動作電圧低減によって超低消費電力化されたエレクトロニクスの実現に貢献すると期待される。

この技術の詳細は、2012年12月10~12日に米国サンフランシスコ市で開催される国際会議2012 International Electron Devices Meeting(IEDM 2012)で発表される。

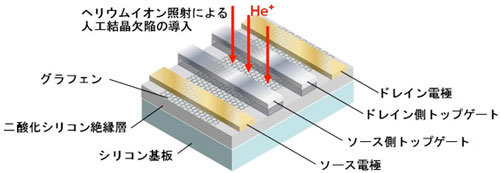

|

|

試作したグラフェントランジスタの概念図 |

近年、携帯情報端末の普及や、IT機器の高機能化に伴う消費電力の増大が懸念され、電子情報機器の消費電力低減への社会的要求が高まっている。このため、大規模集積回路(LSI)の消費電力低減の試みは急速な進展を見せているが、従来のトランジスタ構造では、本質的な限界があるとされている。一方、グラフェンは、電子の動きやすさを表す電子移動度がシリコンの100倍以上もあり、さらに、シリコンなどの本質的な限界の問題も解決できると期待されている。これらのことから、グラフェンはLSI低消費電力化への障害を解決する可能性を秘めており、ポストシリコン世代の新しい機能性原子薄膜を用いた超低消費電力トランジスタの材料としても期待を集めている。

しかし、グラフェンにはバンドギャップがないため、スイッチングトランジスタとして使用した場合に電流を十分に遮断できない。また、バンドギャップを形成する技術もあるが、スイッチング動作に必要なバンドギャップを形成すると、電子移動度が低くなってしまう。そのため、小さなバンドギャップで効率的にスイッチング動作ができる、新しい動作原理のグラフェントランジスタが求められている。

GNCは、内閣府と独立行政法人 日本学術振興会によって運営される最先端研究開発支援プログラム(FIRST)に採択されたプロジェクトを実施するために2010年4月に設立された。企業5社(富士通株式会社、株式会社 東芝、株式会社 日立製作所、ルネサスエレクトロニクス株式会社、株式会社 アルバック)からの出向研究者と産総研研究者によって構成されている。GNCでは、2010年度より、つくばイノベーションアリーナによる研究支援のフレームワークのもとで、産総研ナノエレクトロニクス研究部門、産総研ナノデバイスセンター、物材機構WPI-MANAと、グラフェンのエレクトロニクス応用に関する共同研究を行ってきた。

なお、この研究は、FIRSTのプロジェクト「グリーン・ナノエレクトロニクスのコア技術開発」(中心研究者 横山 直樹)の助成により行われた。

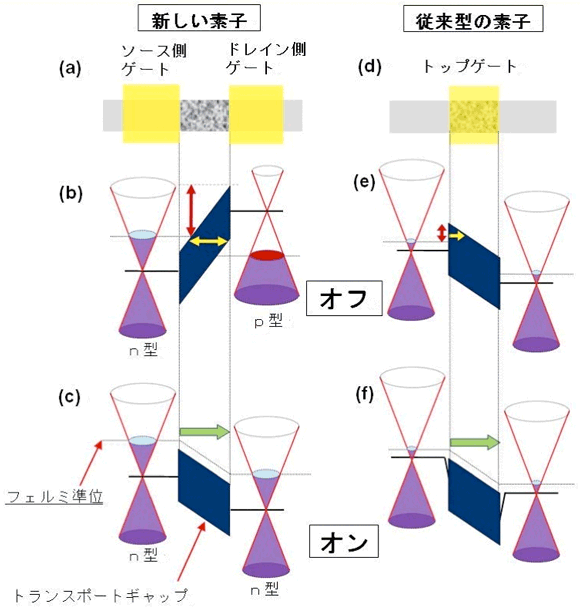

今回開発した新しいグラフェントランジスタの動作原理を図1(a)~(c)に示す。2つのトップゲートの間のチャネル部分のグラフェンにトランスポートギャップを生じさせるためにヘリウムイオン顕微鏡を用いてヘリウムイオンを6.9 x 1015 ions/cm2の密度で照射して結晶欠陥を導入してある。トップゲートに電圧をかけ静電的な制御によってチャネル両側のグラフェンのエネルギーバンドを変調できるが、トップゲート電圧の極性によってグラフェンの電流を運ぶキャリアの極性がn型、p型と変化する。チャネルの両側の極性が異なる場合トランジスタはオフ状態となり(図1(b))、同じ極性の場合はオン状態となる(図1(c))。オフ状態のとき、従来型のトランジスタ(図1(d)~(f))ではトランスポートギャップを持つチャネルのソース側あるいはドレイン側の端に形成される障壁で電荷の移動を阻止するが、図1(e)に示すように小さい障壁しか得られないためオフ状態におけるリーク電流が大きい。一方、今回開発したトランジスタでは、図1(b)に示すようにトランスポートギャップが従来型の場合(図1(e))よりも大きな障壁となって電荷の移動を阻止する。その結果、従来型と比較してより良好なオフ状態を得ることができる。

このトランジスタでは、通常移動度が劣化するチャネル部分の長さを、従来型の素子よりも短くできる。さらに、小さなトランスポートギャップでも有効にオフ状態をとれるため、従来型の素子よりもトランスポートギャップをより小さくできる。これらの特質により、トランジスタのオン・オフ動作を従来型よりも高速にできるため、回路の動作電圧を低減して低消費電力化したLSIが実現できると考えられる。また、リソグラフィーや蒸着、不純物注入工程など、既存のシリコン集積回路の製造技術の枠内で作製でき、大面積ウェハでも製造が容易である。

|

|

図1 新しいグラフェントランジスタと従来型トランジスタの動作原理 |

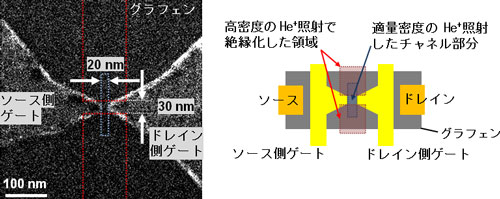

この新しい動作原理のトランジスタ動作を実証するために、グラファイトから剥離した単層グラフェン上にソース・ドレイン電極および1対のトップゲートを形成し、トランジスタを形成した。1対のトップゲートの間に適量のヘリウムイオンを照射してチャネルとし(図2の青点線部)、その外側の不要な部分のグラフェンはヘリウムイオンを多く照射して絶縁化した(図2の赤点線部)。その結果、トランジスタのチャネル部分は、長さ20 nm、幅 30 nmのサイズとなった。

|

|

図2 試作した素子のヘリウムイオン顕微鏡像と模式図 |

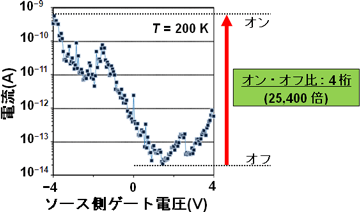

作製したトランジスタを200 K(約-73℃)の低温でオン・オフ動作させた。ソース・ドレイン端子にはそれぞれ −100 mV、+100 mVの電圧をかけ、ドレイン側ゲート電圧を−2 Vに固定して、ソース側ゲート電圧を−4 Vから+4 Vまで変化させて、ソース・ドレイン電極間に流れる電流を測定したところ、約4桁のオン・オフ比を示した(図3)。

|

|

図3 新しいグラフェントランジスタの電流のオン・オフ比 |

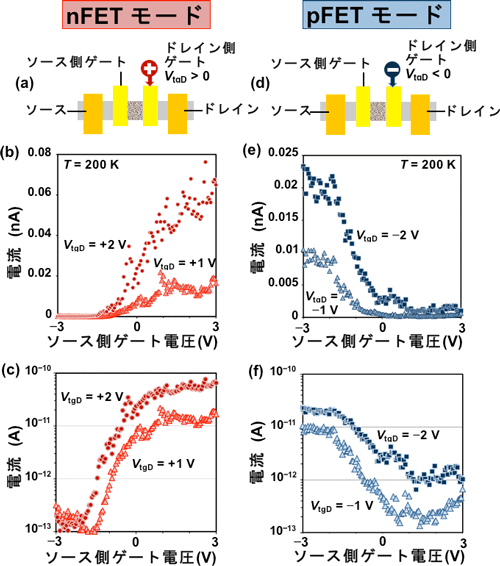

今回開発したトランジスタは、2つのトップゲートに与える電圧の極性が同じか異なるかによってオン状態かオフ状態かが決まる。そのため、片方のゲート電圧を固定しその極性を変化させることで、もう一方のゲート電圧によるトランジスタ動作がn型かp型かを制御できる。今回、ソース・ドレイン端子にそれぞれ −100 mV、+100 mVの電圧をかけ、ドレイン側ゲートの電圧VtgDを正に固定した場合(図4(a))の、ソース側ゲート電圧の変化に対するソース・ドレイン間の電流の変化を図4(b)に示す。図4(c)はその対数プロットである。ソース側ゲート電圧が負の場合にオフ状態、正の場合にオン状態となり、n型トランジスタとして動作している。一方、ドレイン側ゲート電圧を負に固定した場合(図4(d))の、ソース側ゲート電圧の変化に対する電流の変化を図4(e)、(f)に示す。この場合は、ソース側ゲート電圧が負の場合にオン状態、正の場合にオフ状態となり、p型トランジスタとして動作している。すなわち、単一のトランジスタが、電気的な制御によって極性が反転したトランジスタとして動作していることが実証できた。

従来のシリコン素子のトランジスタ極性は半導体への不純物ドーピングのイオンの種類で決まるため、回路を形成後の変更はできなかった。しかし、今回開発したトランジスタではトランジスタ極性を電気的に制御できるため、回路の構成自体を電気的に変更できる集積回路が実現する可能性がある。

|

図4 トランジスタ極性を電気的に反転させたトランジスタ動作の実証

ここでVtgDはドレイン側ゲート電圧 |

トランジスタ極性を電気的制御により変更できるCMOS動作の実現を目指す。さらに、CVD法(化学的気相堆積法)にて合成されたグラフェンを用いた大面積ウェハによる素子試作を目指す。同時に、室温における電流のオン・オフ比の向上や、電荷の移動度の向上のためのグラフェンの高品質化を実現していく。