独立行政法人 産業技術総合研究所【理事長 野間口 有】(以下「産総研」という)ナノエレクトロニクス研究部門【研究部門長 金丸 正剛】シリコンナノデバイスグループ 水林 亘 研究員、右田 真司 主任研究員、太田 裕之 主任研究員、昌原 明植 研究グループ長らは、16 nm世代以降のトランジスタに適用できる、新しい金属ソース・ドレイン接合技術を開発した。

16 nm世代以降の極微細MOSトランジスタでは、ソース・ドレイン接合領域の寄生抵抗が顕在化するため微細化に伴う特性向上の頭打ちや、10 nm程度のゲート長に対し精度よくソース・ドレイン接合を形成することが最大の懸念事項となっている。今回開発した技術により、極低抵抗の金属ソース・ドレイン接合の位置をサブナノメートルレベルで制御できる。また、これによってトランジスタ性能が大幅に向上することを確認した。今回の制御技術によって、16 nm世代以降のMOSトランジスタにおける接合位置制御の課題を解決することにつながる。なお、この研究開発は、独立行政法人 新エネルギー・産業技術総合開発機構(NEDO)の「次世代半導体材料・プロセス基盤(MIRAI)プロジェクト」の委託を受けて行われた。

この技術の詳細は、2011年6月14~16日に京都市で開催される国際会議「VLSI技術シンポジウム」(2011 Symposium on VLSI Technology)で発表される。

|

|

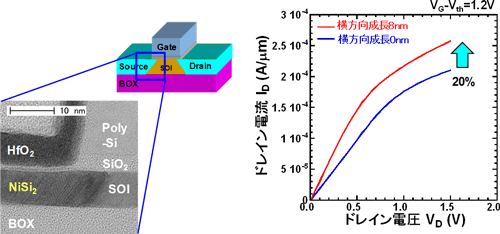

今回開発した技術で作製した金属ソース・ドレイン接合極薄MOSトランジスタとその特性

図中のBOXは埋め込みSiO2、poly-Siは多結晶Siのこと。横方向成長8 nmは、実効ゲート長が16 nm縮小されたことを意味する。

|

これまで、シリコン集積回路は、その最小構成単位であるトランジスタ素子を微細化することによって高性能化・高集積化を実現してきた。素子の微細化はコスト削減にもつながるため、微細素子開発の熾烈な競争が続いている。しかし、2016年以降に市場投入が想定されている16 nm世代やそれ以降のトランジスタ技術では、リン、ヒ素、ホウ素などの不純物を高濃度に添加したシリコン半導体ソース・ドレイン接合領域の寄生抵抗の顕在化と、10 nm程度のゲート長に対して精度よくソース・ドレイン接合を形成できる技術開発が最大の課題となっている。とりわけ、接合位置の揺らぎは、トランジスタ特性を大きくばらつかせる要因となるため、ナノメートルレベルで接合位置を制御できる技術の開発が強く求められている。

産総研は、これまでNEDOの次世代半導体材料・プロセス基盤(MIRAI)プロジェクト委託事業の中で極微細トランジスタの実用化に向け、最先端CMOSプロセス技術の開発を行ってきている。2005年には極低抵抗の二ケイ化ニッケル(NiSi2)金属ソース・ドレイン接合を開発し、これまでのシリコン半導体接合に比べ、抵抗が約100分の1にまで低減することを確認している。2010年にはシリコン酸化膜換算膜厚で0.5nmと世界最薄となる高誘電率ゲート絶縁膜の開発とトランジスタへの導入に成功している(2010年12月8日産総研プレス発表)。また、Silicon-On-Insulator (SOI)基板を用いたトランジスタ開発の研究も推進している。

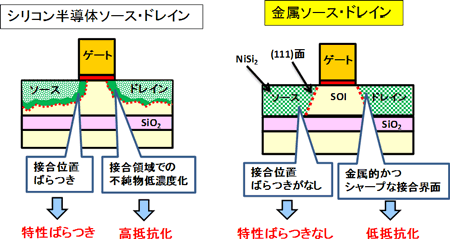

図1に従来型のシリコン半導体ソース・ドレイン接合と金属ソース・ドレイン接合の比較を示す。シリコン半導体ソース・ドレイン接合は、リン、ヒ素、ホウ素などをイオン注入し高温で熱処理して形成するために、注入位置ばらつきや熱拡散による特性ばらつき、接合界面でのドーパント(リン、ヒ素、ホウ素など)の低濃度化による高抵抗化といった問題がある。一方、金属ソース・ドレイン接合は、金属とシリコン(Si)の固相反応により比較的低温で形成するために、接合位置にばらつきがなく、また、接合界面が急峻になるので、特性ばらつきを大幅に抑制することができる。

|

|

図1 シリコン半導体ソース・ドレイン接合と金属ソース・ドレイン接合の比較

|

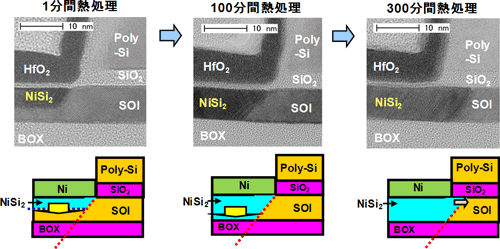

NiSi2結晶は (111)面で囲まれた安定構造を作る性質がある。今回、非常に薄いSi層に対してNiSi2の形成を行った場合の結晶成長の振る舞いを調べて、極微細トランジスタにおける金属ソース・ドレイン接合位置制御の可能性を探った。8 nmの厚さのSOI層を用意し、ダミーゲート構造を作った。Ni膜の成膜後500℃で熱処理して、NiSi2結晶を形成した。この結晶のサイズはSi結晶のサイズとほぼ一致しているためエピタキシャル構造となる。透過型電子顕微鏡(TEM)による断面観察の際、初期の反応端の位置を明確にするために、未反応Niを除去した後にHfO2膜を堆積した。

熱処理時間を変化させたときのエピタキシャルNiSi2ソース・ドレイン接合位置の断面TEM像を図2に示す。1分間の熱処理後にはNiSi2の準安定な(100)面と安定な(111)面が見られる。100分間の熱処理では、<100>方向の結晶成長が進行し、埋め込みSiO2(図中ではBOXと表記)界面に到達して成長が止まっている。このとき、NiSi2の(111)面の位置は変化していない。さらに、その後300分間の熱処理では、NiSi2は安定な(111)面を維持しながら横方向に結晶成長している。これは、トランジスタの接合位置の変化に対応しており、300分間の熱処理により横方向に8 nm進入している。この現象では、原子の固体中での拡散によって成長速度が決まるので、成長量は時間の平方根に依存するが、あえて成長速度を見積もると0.04 nm/分と非常に遅く、ナノメートルレベルで制御できると考えられる。

|

|

図2 熱処理時間に対するエピタキシャルNiSi2ソース・ドレイン接合の位置変化の断面TEM像

図中のBOXは埋め込みSiO2、poly-Siは多結晶Siのこと。 |

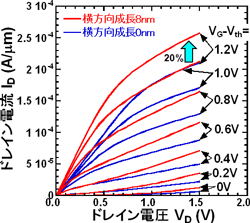

同じゲート構造やゲート長で熱処理時間だけを変化させてトランジスタを試作し、接合位置の効果を調べた。トランジスタ特性の比較を図3に示す。接合位置を近づけたことでドレイン電流が20 %以上増加している。また、特性ばらつきは増えていないことを確認している。このようなNiSi2結晶成長の性質を利用した金属ソース・ドレイン接合の位置制御技術は、16 nm世代以降のMOSトランジスタの新たな接合技術として期待できる。

|

|

図3 ゲート長50 nmのエピタキシャルNiSi2ソース・ドレイン接合MOSトランジスタのドレイン電流-ドレイン電圧(Id-Vd)特性。熱処理時間1分間(横方向成長0nm)と300分(横方向成長8nm)の試作トランジスタの性能比較

横方向成長8 nmは、実効ゲート長が16 nm縮小されたことを意味する。

|

今回開発した技術は、16 nm世代以降で深刻になる特性向上の頭打ち問題の解決につながり、MOSトランジスタの一層の微細化を可能とする。今後は、より微細化したトランジスタの実現や回路レベルでの性能向上の実証を目指す。