独立行政法人 産業技術総合研究所【理事長 吉川 弘之】(以下「産総研」という)情報セキュリティ研究センター【研究センター長 今井 秀樹】物理解析研究チーム【研究チーム長 今福 健太郎】佐藤 証 主任研究員と国立大学法人 東北大学【総長 井上 明久】(以下「東北大学」という)大学院 情報科学研究科 青木 孝文 教授、本間 尚文 助教らが開発した、暗号機能を実装したFPGAボードが、暗号ハードウェアモジュールとしては初めて、独立行政法人 情報処理推進機構(以下「IPA®」という)が運用する「暗号モジュール試験及び認証制度(JCMVP®)」の認証を取得した(平成19年12月17日)。暗号FPGAボードは国際標準暗号AESを実装したもので、セキュリティレベル1の認証である。

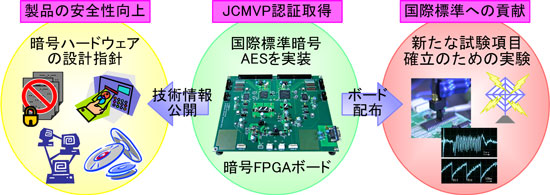

産総研は、今後新たな試験項目・手法の確立に貢献すべく、今回開発したFPGAボードを標準評価ボードとして国内外の大学・研究機関に無償配付する。また、暗号ハードウェアの設計指針となるように、ボードの詳細な設計仕様書やソースコードもウェブサイトで無償公開し、第三者評価された製品の普及による情報セキュリティ製品全体の安全性向上に貢献する。

|

|

暗号FPGAボードの概要 |

ブロードバンド・ネットワークの急速な拡大と、情報家電、ICカード、RFIDタグ等の普及により、生活のあらゆる場面で大量のデータがやりとりされ、情報の漏洩(ろうえい)や改ざんといったセキュリティ上の脅威が増している。暗号はそのような脅威へ対抗するために必須の基礎技術として民生品にも広く利用されるようになってきた。しかし、暗号アルゴリズムが正しく実装されていることを利用者自身で判断することは難しく、また、万全なセキュリティを謳(うた)っている製品に欠陥が見つかることも少なくない。そこで、IPA®による「暗号モジュール試験及び認証制度(JCMVP®:Japan Cryptographic Module Validation Program)」の正式運用が平成19年4月から始まった。これは暗号機能を持つ製品に暗号アルゴリズムが正しく実装されていることや、暗号の鍵、パスワードといった重要な情報の安全性を確保していることを試験および認証する第三者評価制度である。

安全で安心な情報ネットワークの実現には、安全性が確保された製品の普及が重要な鍵となるが、第三者評価に耐えうる暗号ハードウェアの開発には高い専門知識が必要とされる。そのため、実装方式の手本とするために、認証を取得した暗号モジュールの内部仕様やソースコードの公開が強く求められていた。しかしながら、セキュリティ製品の核となる暗号ハードウェアの詳細な実装情報が公開されることはこれまでなかった。

米国国立標準技術研究所(NIST)は現在、試験項目の拡充に向けた取組を行っており、国際標準規格も同様に将来改定される見込みである。国際標準規格の策定には、統一された実験環境の構築が重要となるが、現在は各研究機関が独自の実験装置を用いているため、各機関による提案手法の第三者検証や標準規格化が難しい。

産総研の情報セキュリティ研究センターでは、高性能な暗号ハードウェア実装技術の開発と、ICカードに代表される暗号機能を持つ製品の安全性評価手法の研究に取り組んできた。また、IPA®と独立行政法人 情報通信研究機構が共同で運営するCRYPTRECの暗号モジュール委員会および電力解析実験ワーキンググループ活動に主体的に参画し、 電子政府推奨暗号に準拠した暗号モジュールに対するセキュリティ要件および試験要件の策定に向けた検討を行っている。

なお、今回の認証を受けたFPGAボードの開発は、経済産業省の委託事業「暗号モジュールの実装攻撃の評価に関する調査研究」の一環として行われた。

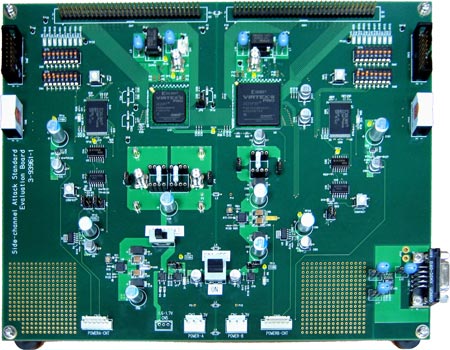

今回開発した暗号FPGAボード(図1)は、標準暗号アルゴリズムであるAESをFPGA上に実装し、パーソナルコンピューターと接続してデータの暗号化・復号を行う装置である。FPGAは機能の書き換えが可能なLSIであるため、攻撃によって回路が改ざんされ秘密情報が盗み出される可能性があり、また回路の故障によってデータが複号できなくなる危険性もある。そこで、国際標準規格(ISO/IEC 19790)に定められたセキュリティ要件を満たす改ざん防止機能とエラー検知機能を開発し、本FPGAボードに実装した。産総研は第三者評価に耐えうる暗号ハードウェアの設計手法を示すために、暗号FPGAボードの仕様書、回路図、FPGAに実装した全てのソースコードをウェブページ( http://www.rcis.aist.go.jp/special/SASEBO)で無償公開することとした。

|

|

図1 JCMVP認証を取得したAES暗号FPGAボード |

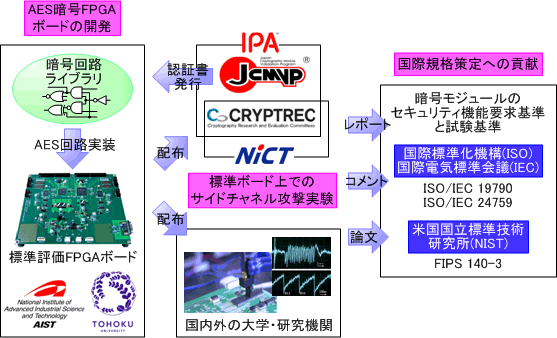

また本FPGAボードは、新たな試験項目の確立とその有効性検証のための実験用ボードとしての役割も持っており、暗号回路が発生する電力波形や電磁波形を精密に測定できる。このボードは国内外の大学・研究機関に標準評価ボードとして利用すべく配布される予定である。これにより新たな試験項目に係る研究を促進し、暗号モジュールの国際標準規格改定に貢献するものと期待される(図2)。また、多くの有効な実験データを得るためには装置に実装する暗号回路も標準となるものが必要である。暗号回路の設計は知的財産として高い価値を持つため、これまでソースコードの公開はほとんどない。そこで産総研と東北大学は、今回実装したAES暗号回路に加え、全てのISO/IEC標準暗号の回路を設計し、これらのソースコードも上記のウェブページで無償公開する。

|

|

図2 標準評価FPGAボードの学術研究および国際標準化活動 |

国際標準規格(ISO/IEC 18033-3)の全ての暗号アルゴリズムを実装した専用LSIボードや、今回とは異なるアーキテクチャのFPGAボードも開発していく。また、各ボードのFPGAはマイクロプロセッサ機能を持つものを使用しており、暗号ハードウェアだけでなく暗号ソフトウェア・モジュールに係る実験も行っていく。

これらを安全性評価標準ボードとして普及させ、暗号ハードウェアおよびソフトウェアの設計情報を公開することで、実験環境の整備と測定評価手法の統一を図り、暗号モジュール評価認証制度の普及と国際標準規格の改定に貢献したい。