独立行政法人 産業技術総合研究所【理事長 吉川 弘之】(以下「産総研」という)パワーエレクトロニクス研究センター【センター長 荒井 和雄】は、国立大学法人 山梨大学【学長 貫井 英明】大学院 医学工学総合研究部【部長 前田 秀一郎】春日・矢野研究室(以下「山梨大大学院」という)と共同で、六方晶炭化珪素(4H-SiC)を用い、p+ゲート領域を埋め込んだ構造を採用した静電誘導型トランジスタ(埋込ゲート型SiC-SIT:SiC-Static Induction Transistor)を、独自に開発した製造プロセスを駆使して作製し、耐圧700V、オン抵抗1.01 mΩcm2という、耐圧600 V~1.2 kV系のスイッチング素子としては、世界最小のオン抵抗を実現した【図1及び図2参照】。これにより、従来のインバータ回路で用いられているSi(シリコン)-IGBT(Insulated Gate Bipolar Transistor)と比較して、1/12と大幅な電力損失削減が可能となると見積もられる。

今回開発した、埋込ゲート型SiC-SITの応用範囲は、商用AC100/200 Vを電源とする家電機器(IHクッキングヒータ、エアコン、エコキュート等)や無停電電源(UPS)等の小容量インバータ、DC300/400 Vを電源とする自動車(ハイブリッド車、電気自動車、燃料電池車等)の中容量インバータ、産業用大型モータ制御の大容量インバータを始め、分散電源、太陽光発電等、多岐にわたり、その市場規模は1兆円を超えると予想される。また、この素子がこれらの分野において実用化された場合、2020年時点での我が国の炭酸ガス排出量削減効果は、1990年の我が国の全炭酸ガス排出量の1%に相当すると試算することが出来、本年2月16日に発効した京都議定書で義務付けられている地球温暖化ガス(炭酸ガス)排出削減に大きく寄与することが期待される。

なお、本研究成果の詳細については、2005年3月29日~4月1日の日程で埼玉大学において開催される第52回応用物理学関係連合講演会において発表する予定である。

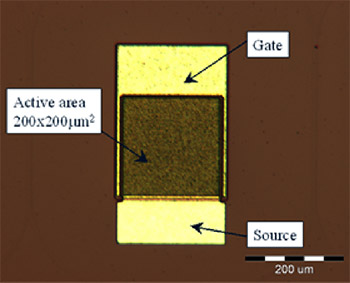

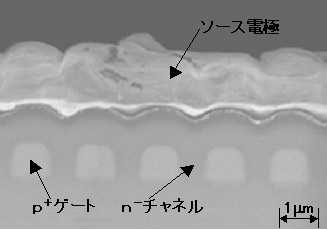

図1.今回作製した埋込ゲート型SiC-SIT素子

|

|

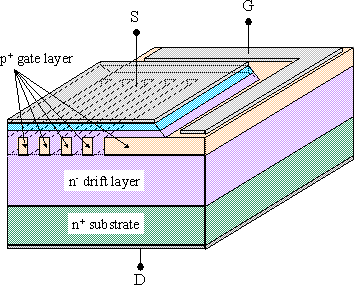

図2.今回作製した埋込ゲート型SiC-SIT素子の模式図

|

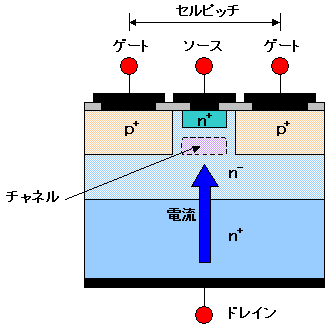

炭化珪素(SiC)は、シリコン(Si)と比較してバンドギャップ幅が約3倍広く、絶縁破壊電界強度が約10倍大きいため、耐熱性や耐電圧性に優れ、Siに置き換わる超低電力損失パワー素子の半導体材料として注目されており、世界中で研究・開発が進められている。SiCを用いた素子の中でも、静電誘導型トランジスタ(SiC-SIT)は、SiC結晶中の高い電子移動度(~900 cm2/Vs)をそのまま生かせる、超低オン抵抗、高速スイッチング素子として非常に期待されている。現在、唯一市販されているSiCスイッチング素子はSITであり、ドイツの半導体メーカーから供給されている(耐圧1200 V、オン抵抗12 mΩcm2)。SITの性能を向上させるためのキーポイントはチャネル構造を如何に微細化するかであるが、従来試みられてきた構造【図3参照】では微細化が容易ではなく、市販されている素子を含めてSiCの材料自体が持つ物理特性の限界には程遠い性能しか得られていなかった。

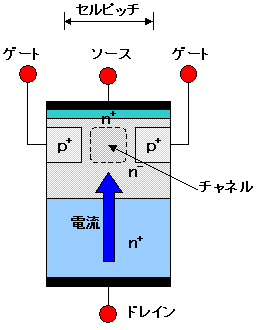

産総研と山梨大大学院は、上記の様な問題点を解決するためにp+ゲート領域を完全に埋め込んだ構造(埋込ゲート型SiC-SIT)を提案した【図4参照】。埋込ゲート型構造では、ソース電極、及びゲート電極形成時の精密な位置合わせ精度は必要なく、単位素子サイズ(セルピッチ)も大幅に縮小する事が出来る。この様な素子構造の微細化により、単位面積当たりに流すことの出来る電流量を多く出来、即ち素子のオン抵抗を下げることが可能となる。デバイスシミュレータを用いた計算結果においても、同構造を最適化することにより大幅なオン抵抗の改善が可能であることが確認された。この埋込ゲート型SIT構造は、シリコンを用いたSi-SITでは最も初期に提案され、数多くの試作が行われてきたが、SiCの場合、素子の微細化を進める上で従来のプロセスでは、埋込ゲート型SIT構造を実現することが極めて困難な事もあり、これまで試みられてこなかった。今回、独自の製造プロセス技術を開発することにより、微細埋込ゲート構造を実現することが可能となり、超低電力損失パワートランジスタの実現につながった。

図3.従来型SiC-SIT素子の断面構造図

|

素子の微細化は

素子性能の改善に直結!!

|

図4.今回作製した埋込ゲート型SiC-SIT素子の断面構造図

|

【図5】に今回新たに開発した埋込ゲート型SiC-SITの製造工程の概略図を示す。まず、(a)n+4H-SiC基板上にn-ドリフト層、p+ゲート層をエピタキシャル成長させる。次に、(b)ドライエッチング法によりp+ゲート層を離間させ、微細な溝構造を形成する。このエッチングプロセスの精度(p+ゲート領域の幅x, 隣り合ったp+ゲート領域の間隔y)により素子特性がほぼ決定されるため、素子の歩留まりを確保するためには同プロセスを再現性良く行うことが最も重要である。今回は、エッチングマスク材の選定、及びドライエッチング条件(ガス種、ガス圧力、ガス流量、時間)の最適化を図ることにより、ドライエッチングによる微細な溝構造の形成が初めて可能となった。この溝構造上に、(c)n-チャネル領域をエピタキシャル成長により形成する。通常、エピタキシャル成長は平坦な基板上に行われるが、SiC基板の結晶方位やエピタキシャル成長の条件(温度、ガス流量等)を最適化することにより、微細な溝構造上のエピタキシャル成長が初めて可能となった。その後、(d)n+ソース領域をイオン注入により形成し、活性化熱処理(1600 ℃)後、(e)ソース電極及びドレイン電極を形成し素子が完成する。この様にして作製した埋込ゲート型SiC-SIT素子の断面電子顕微鏡像では、p+ゲート領域が完全に埋め込まれ、それらの間にサブミクロンの幅でn-チャネル領域が形成されていることが分かる【図6参照】。

|

|

|

図5.今回作製した埋込ゲート型SiC-SIT素子のプロセスフロー概略図。p+ゲート領域を形成するドライエッチング技術、及び微細な溝構造上へのエピタキシャル技術(前処理技術を含む)を新たに開発した。

|

図6.今回作製した埋込ゲート型SiC-SIT素子の断面電子顕微鏡像の一例

|

|

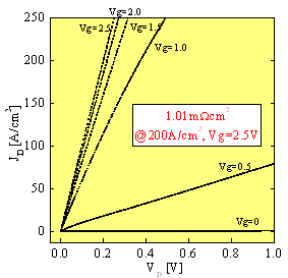

図7.今回作製した埋込ゲート型SiC-SIT素子の電圧電流特性

|

今回作製した埋込ゲート型SiC-SITの電圧・電流特性では、ゲート電圧VG=2.5 Vにおいて室温で1.01 mΩcm2という極めて低いオン抵抗が得られた【図7参照】。逆方向特性ではVG=-12 Vにおいて700 Vの耐圧が得られており、これまで報告されたSiCを含めた600 V~1.2 kV耐圧のスイッチング素子の中で、最も低いオン抵抗が実現された。従来のインバータ回路で用いられているSiパワートランジスタ(IGBT)は、耐圧600 V、オン抵抗12~13 mΩcm2程度であるが、これと比較して1/12のオン抵抗値であるため、電力損失も1/12と大幅な削減が可能になると見積もられる。

また、今回作製した埋込ゲート型SiC-SITが各応用分野において実用化された場合、2020年時点での我が国の炭酸ガス排出量削減効果は、1990年の我が国の全炭酸ガス排出量の1%に相当すると試算する事が出来る【図8参照】。

|

|

|

図8.今回作製した埋込ゲート型SiC-SITが各応用分野において実用化された場合の、2020年時点における我が国の炭酸ガス排出削減量の見積り(参考:「SiC素子の基礎と応用」オーム社刊) |

まず、実用化レベルの電流容量(10~20 A)を目標として研究開発を更に進めていく予定である。また、同素子の応用範囲を広げるために、素子の基本構造はそのままに、n-ドリフト層の不純物濃度、及び厚みを最適化することにより、更なる高耐圧化(1.2~2.0 kV)を図る。更に、素子設計の最適化を図ることにより、従来SiC-SITでは困難と言われてきたノーマリオフ特性の実現を目指す。