半導体MIRAIプロジェクトを構成する独立行政法人 産業技術総合研究所【理事長 吉川 弘之】(以下「産総研」という)次世代半導体研究センター【センター長 廣瀬 全孝】及び、技術研究組合 超先端電子技術開発機構【理事長 佐々木 元】(以下「ASET」という)は、遺伝的アルゴリズムに基づくクロック調整方式を開発することにより、ギガヘルツ以上の高速動作LSIにおいて、動作クロック周波数を向上させ、消費電力を半減することに成功した。

一般にギガヘルツを超える高速動作LSIでは、クロックスキュー(クロック信号の伝播時間のずれ)によって、設計どおりのスペックで動作できるLSIの比率(動作歩留)が低下し、価格の上昇を招いている。また高速なクロック動作による消費電力の大きさも問題とされてきた。

このような背景において、本方式は、目標設計値よりも高いクロック周波数(最大25%向上)でLSI(1GHzALUを含むメモリテストパターン生成器と1GHz乗算器の2種類の回路を実装)を動作させ、電源電圧を標準の1.2Vから0.8Vに下げることで消費電力を54%低減することに成功した。クロック調整は電源電圧の低下によって正しいタイミングで動作できないLSIに対しても有効に働くことが示された。

また本方式を前提とした回路設計を行うことで、タイミング設計がより簡単となり、その結果、従来よりも設計工数を20%低減できることも明らかになった(高速メモリDDR-SDRAMのコントローラの設計工程を対象として評価)。

今後は、本クロック調整方式の実用化をさらに進めるために、3ギガヘルツ動作を目標とした実用的LSIチップの開発と、数百メガヘルツ程度のモバイルコンピュータにおける低消費電力化の実験を予定している。

なお本研究成果の詳細は、2003年6月12~14日に、京都(リーガロイヤルホテル京都)において開催される ”2003 Symposium on VLSI Circuits” において発表される。また、本研究に関連した特許を数件出願中である。

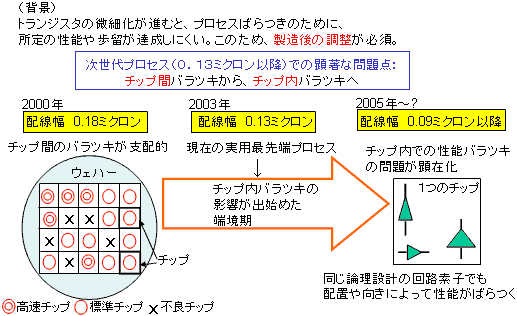

LSIの微細化と高集積化が進むにつれてクロックスキューの問題は深刻化している。しかしこれについての抜本的な解決策は与えられていない。一方、LSIに対して調整を施すというアプローチは従来付加的な手段であり、主体的に導入されることはなかった。しかし、LSIの微細化によりいよいよ歩留の問題が深刻化したため、従来のように、設計段階で性能を追い込むことの限界が昨今叫ばれ始めている(図1)。

|

|

|

図1 本研究の背景と位置付け

|

|

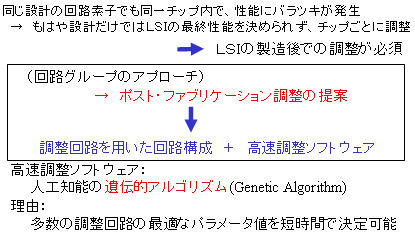

半導体MIRAIプロジェクトで回路システム技術開発を遂行する産総研次世代半導体研究センターの回路システム技術グループは、MIRAIスタート以来、LSIの製造後の調整を重視した回路設計・調整方式として、ポストファブリケーション調整を提唱している。図2のように、ポストファブリケーション調整は「調整回路用いた回路構成」と遺伝的アルゴリズムを用いた「高速調整ソフトウェア」の2つから構成される汎用性の高い技術である。

|

|

|

図2 本研究のアプローチ

|

|

○クロックスキューのために、高速デジタルLSIの動作歩留は低下し、価格は上昇

クロックは、デジタルLSIの内部動作を制御するための同期信号であり、ある一定周期で発生するパルス信号を用いて、例えばLSI内各部でのデータの取り込み等を行っている。図3はクロックによるデジタルLSIの動作の一例である。 図3(1)において、“+1”と示したのは、入力データを1だけ増加する回路であり、これらがレジスタをはさんで縦列に接続され、クロックが入力されるたびにデータが1ずつ加算されて、LSI内部を転送される様子を示している。入力データは、クロックが入力されるたびにデータが1ずつ加算されて、LSI内部を転送される。例えば、”5”というデータが初段のレジスタに入力された場合(図3(1)の(1)-a)、次のクロックでは2段目のレジスタには”6”というデータが入り((1)-b)、3段目には”7”というデータが入って、”7”が出力される((1)-c)。

最近のLSIの微細化、高集積化に伴って、本来全く同時にLSIの各部に伝達されるべきクロック信号が、配線の状況等によってそうならないケースが多くなっている。このような本来のクロックタイミングからのずれのことを、クロックスキューと呼んでいる。例えば図3(2)ではレジスタ2へのクロック信号が本来あるべきタイミングよりも早く到着するために、正しい値がレジスタに取り込まれない例を示している(図3(2)の(2)-b)。

このようなクロックスキューはクロックの高速化、トランジスタの微細化が進むほど、その影響が顕著となるが、これまでのところ抜本的な解決策は与えられていない。

○遺伝的アルゴリズムによるクロック調整方式を提案

このようなクロックスキューの問題を制御するアプローチをとることで、低消費電力化、クロック周波数向上、設計工数の低減の3つの利点を達成している。

図3(3)に、本方式の基本アイデアを述べる。先の図3(2)においてクロックの到着が早すぎて誤動作する例を示したが、その誤動作部分のクロック信号線にプログラマブルな遅延素子(以下、「プログラマブル遅延素子」という。)を挿入したのが図3(3)の状態(3)-aと状態(3)-bである。このプログラマブル遅延素子の値を最適な値に設定することにより、正しい演算結果である6をレジスタに取り込めることを示している。このような調整箇所は、LSI全体では多数にのぼるため、もはや人手で発見、調整することは不可能である。そこで遺伝的アルゴリズムを用いたクロック調整方式を考案した。

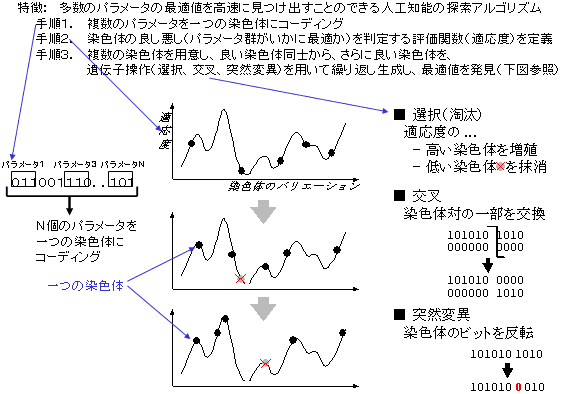

遺伝的アルゴリズムは、図4に示すように多数のパラメータの最適値を高速に決定することができる人工知能の探索アルゴリズムである。このクロック調整の場合のパラメータとは、多数のプログラマブル遅延素子の各々における遅延値である。

|

|

|

図4 遺伝的アルゴリズムについて

|

|

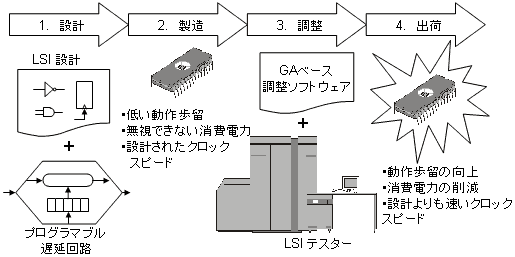

○タイミングの余裕が少ない回路部分にプログラマブル遅延素子を設計段階から挿入し、LSI製造後にテスタで各チップごとにプログラマブル遅延素子を調整して出荷

本クロック調整方式が、LSIの開発全体の流れの中で、どのように位置付けられるのかを示したのが図5である。タイミングの余裕が少ないことが設計段階でわかっている場合、その部分にあらかじめプログラマブル遅延素子を挿入した(図5の「1.設計」)上で、LSIを製造する(図5の「2.製造」)。製造後に、遺伝的アルゴリズムを用いた調整ソフトウェアを搭載したテスタによって、各LSIごとに最適な遅延値を遺伝的アルゴリズムによって求め(図5の「3.調整」)、その遅延値をLSIに書き込んで出荷する(図5の「4.出荷」)。

従来のLSI開発では、調整は最小限にとどめるのが常であるが、本方式は、LSIの製造後での調整を主眼とするため、この回路設計・調整方式を、ポストファブリケーション調整技術と名づけている。

プログラマブル遅延素子を挿入する部分には、いろいろな階層が考えられる。第一はクロックドメインと呼ばれる、ある程度大きな回路ブロック間でのクロックスキューの解消のためにプログラマブル遅延素子を入れる場合がある。第二は、各ドメインの中でタイミングの余裕が少ない箇所にプログラマブル遅延素子を入れる場合である。

このようにプログラマブル遅延素子は、必要に応じてLSIの各階層に挿入可能であり、その総数は数百箇所程度までは十分に遺伝的アルゴリズムで扱うことができ、1秒程度の調整時間で各LSIの最適な遅延値を設定可能である。

|

|

|

図5 ポストファブリケーション調整(製造後調整)

|

|

○クロック調整により電源電圧を下げたLSIでも動作可能

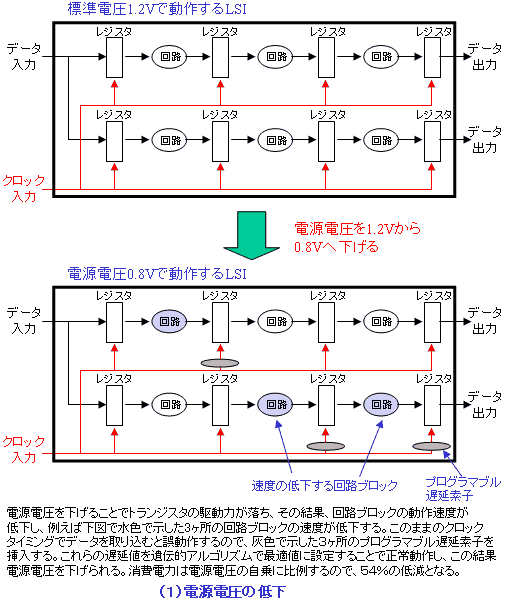

図6(1)に、クロック調整により、電源電圧の低減が可能な仕組みを示している。LSIの電源電圧を下げると、トランジスタの駆動能力が低下するため、回路ブロックの動作速度も落ちてその結果、クロックによるデータ取り込みのタイミングに間に合わない箇所がいくつも出てくる。図6(1)において水色で示した回路ブロックがそのような遅くなった回路ブロックの例である。そこでこれらの回路ブロックの出力を取り込むクロック信号線に、プログラマブル遅延素子を挿入し、適切な遅延値を与えることで、電源電圧を下げた状態でも、正常な論理動作を実現することができる。本開発では、電源電圧を標準電圧である1.2Vから0.8Vに低下させたが、その状態においてクロック調整を行うことで、全LSIにおいて正常動作を再現した。消費電力は電源電圧の自乗に比例するため、電源電圧が3分の2になったことで、消費電力は54%減となる。

○クロック調整によりクロック動作周波数を最大25%向上

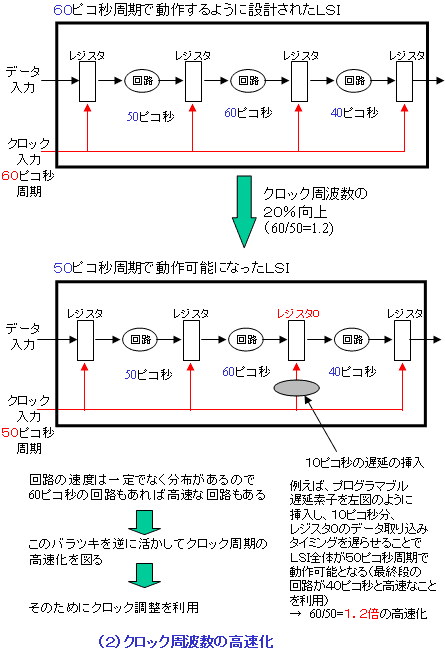

製造プロセスのバラツキにより、各回路ブロックの動作速度のズレが生じるが、このズレをクロック調整では積極的に生かすことで、最大動作クロック周波数を高めることが可能である。本開発では、消費電力を半減し、クロック周波数の最大25%の向上を実現した。その仕組みを図6(2)で説明する。

図6(2)の上部では、60ピコ周期で動作するように設計、製作されたLSIでの実行が示されているが、製造バラツキにより、本来の設計よりも早く動く、40ピコ秒や50ピコ秒の回路ブロックが含まれていることがわかる。このような速度のバラツキは、今後LSIの微細化が進むほど発生するので、これを逆に利用することで、クロック周波数の向上が可能である。すなわち、中央の回路ブロックは60ピコ秒でしか動けないが、続く回路ブロックは40ピコ秒で動作する。そこで、プログラマブル遅延素子を挿入し、10ピコ秒の遅延を意図的に入れることで、この二つの回路ブロックの間でタイミングの貸し借りが行われ、50ピコ秒周期での実行が可能となる。つまり、60ピコ秒周期から50ピコ秒周期へのクロック周波数向上が行われるわけで、この例だと20%の向上であるが、実際の実験では25%向上を果たしている。

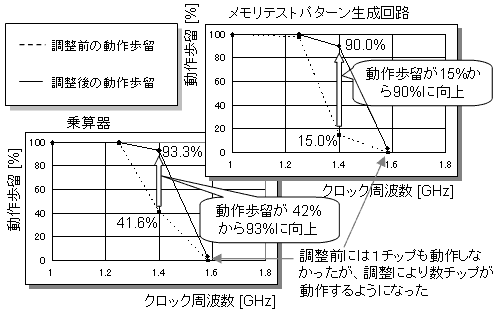

図7に、本技術の基本的な測定結果を示す。2種類の中規模回路(メモリテストパターン生成回路と乗算器)において、クロック調整の前後で動作歩留が最大で15%から90%まで向上している様子が示されている。また、動作するチップの分布が高速側にシフトしていると理解することもできる。

|

|

|

|

図6 クロック調整による電源電圧の低下とクロック周波数の高速化

|

|

|

|

図7 ポストファブリケーション・クロック調整の効果

|

|

○2種の1GHzデジタル回路を試作して実証。設計実験での検証も達成

本研究開発では、まずプログラマブル遅延素子のLSI回路を作成した。このプログラマブル遅延素子は、最短で30ピコ秒のクロックスキューを調整することができる。30ピコ秒は、1Ghzのクロック周波数では3%の誤差に相当する値である。これを用いて、2種の1GHzデジタル回路(1GHzALUを含むメモリテストパターン生成器、1GHz乗算器)を作成し、クロック調整実験を行った。その結果は、すでに述べたように、全チップにおいて最大25%のクロック周波数の向上と0.8V動作(54%の低消費電力化)が実現した。

さらに、高速メモリDDR-SDRAM用コントローラの設計工程を評価対象として、クロック調整方式の適用を前提とした回路設計を行い、表1に示すように、従来手法に比較して、回路設計の種々の段階での工数低減、トータルで20%の低減が可能なことを実証した。

|

表1 クロック調整・前提設計による設計工数の低減

|

|

設計ステージ

|

従来の方法 [人日] |

本手法 [人日] |

|

機能設計 |

12.0 |

1.5 |

|

ロジック設計 |

30.0 |

30.0 |

|

フロアプランニング |

7.0 |

2.0 |

|

検証(1) |

5.0 |

5.0 |

|

レイアウト |

7.0 |

1.5 |

|

検証(2) |

6.0 |

4.0 |

|

ライブラリ設計 |

42.0 |

42.0 |

|

合計

|

109.0 |

86.0 |

|

|

DDR-SDRAMインタフェースの設計実験で、設計工数2割削減

|

本クロック調整方式の実用化をさらに進めるために、3ギガヘルツ動作を目標とした実用的LSIチップの開発と、数百メガヘルツ程度のモバイルコンピュータにおける低消費電力化の実験を予定している。