国立研究開発法人 産業技術総合研究所【理事長 中鉢 良治】(以下「産総研」という)フレキシブルエレクトロニクス研究センター【研究センター長 鎌田 俊英】 フレキシブル材料基盤チーム 堤 潤也 主任研究員、同研究センター 長谷川 達生 総括研究主幹らは、産総研が独自に開発した薄膜トランジスタ(TFT)アレイ一括検査技術の測定感度と検査面積を大幅に向上させるとともに、本技術を応用したストレージキャパシターの検査を可能にした。

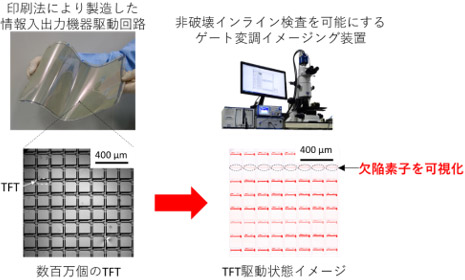

大面積化・省エネルギー化が可能な印刷法は、ディスプレーやタッチパネルなどの情報入出力機器の製造技術として期待されている。しかし、数百万個のTFTとストレージキャパシターがアレイ状に配置された情報入出力機器の駆動回路(アクティブバックプレーン)を短時間で検査することは難しく、高生産効率と高品質を両立させる上での大きな課題となっていた。

今回、TFTアレイの駆動状態を光学イメージ化して一括検査できる産総研独自のデバイス評価技術(ゲート変調イメージング技術)を改良し、検査時間を10分以上から3分以内に短縮し、検査面積を1 mm角から3 cm角に大幅に向上させた。これは、画素密度150 ppiのバックプレーンでは、TFT約30,000素子を3分以内に検査することに相当する。さらに、本技術を応用したストレージキャパシターの検査も可能にした。これにより、膨大な数のTFTとストレージキャパシターを配置する大面積デバイスを非破壊インライン検査できるため、印刷法による大面積デバイスの高品質化が期待できる。

なお、この技術の詳細は、2018年1月15日(現地時間)に欧州科学誌Organic Electronicsに掲載される。

|

|

印刷法で製造したデバイスの高品質化に向けた非破壊インライン検査技術 |

情報化社会の進展とともに、あらゆる生活シーンにエレクトロニクス技術が浸透していく中、情報入出力機器のさらなる使用利便性の向上と多様化、製造技術の簡易化・低コスト化が求められている。これらを達成するキーテクノロジーのひとつが、軽量で柔軟なプラスチックフィルム上に、省資源・省エネルギーの印刷技術を用いてデバイスを製造する「プリンテッドエレクトロニクス」技術であり、現在、基礎から製品開発まで幅広いレベルでの研究開発が世界的に進行している。

中でも、大面積の高精細ディスプレーを全印刷で製造する技術の開発は、プリンテッドエレクトロニクスの重要な課題となっている。しかし、ディスプレーの各画素を制御する駆動回路(アクティブバックプレーン)は、通常、画素数に対応した数百万個のTFTとストレージキャパシターで構成されるため、性能平準化に改善の余地を残す印刷法による製造技術の確立は容易ではない。このため、液晶や有機EL素子などの表示素子(フロントプレーン)を載せる前に、バックプレーンの動作を高速に非破壊検査することが求められるが、膨大な数のTFTとストレージキャパシターを短時間で検査することは難しく、高生産効率と高品質を両立できるインライン検査技術の開発が喫緊の課題となっている。

産総研は、プリンテッドエレクトロニクス技術の実用化を目指した研究開発の一環として、印刷法によるアクティブバックプレーンの製造技術と、これに対応できる非破壊・高速のデバイス評価技術の開発を進めてきた。特に、バックプレーン上のTFTアレイを高速に一括して検査するため、ゲート電圧をかけることでTFTに生じる光透過率・反射率の微小変化を可視化するゲート変調イメージング技術の開発を進めてきた。2014年には、5×5の小規模なTFTアレイの動作不良個所と性能分布を10分程度で可視化できた。今回、ゲート変調イメージング技術を改良して測定感度と検査面積の大幅向上に取り組むとともに、本技術を応用したストレージキャパシターの検査に取り組んだ。

なお、本研究開発の一部は、独立行政法人 日本学術振興会の科学研究費助成事業若手研究(A)の研究課題「多結晶薄膜デバイスのための高空間分解能キャリアイメージング技術開発」(研究課題番号:16H05976)と、国立研究開発法人 科学技術振興機構の戦略的イノベーション創出推進プログラム(S-イノベ)の研究開発テーマ「有機材料を基礎とした新規エレクトロニクス技術の開発」の研究課題「新しい高性能ポリマー半導体材料と印刷プロセスによるAM-TFTを基盤とするフレキシブルディスプレイの開発」の助成を受けて行った。

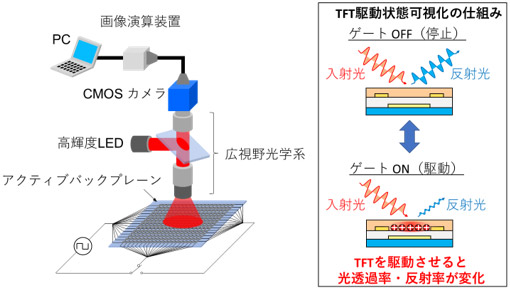

図1に、今回改良したゲート変調イメージング装置の概略を示す。TFTにゲート電圧をかけて、キャリアを蓄積(TFTを駆動)すると、半導体層の光透過率・反射率がごくわずか(1万分の1程度)だけ変化する。この装置では、アクティブバックプレーンの全てのTFTにゲート電圧をかけた状態(TFTを駆動した状態)と、かけない状態(TFTを停止させた状態)の光学イメージをそれぞれ撮影し、画像演算により両者の差分イメージを求めて微小な変化のイメージ(ゲート変調イメージ)を得る。正常動作するTFTだけがゲート変調イメージに現れるので、TFTの動作不良個所をイメージから一括して特定できる。

今回、ゲート変調イメージの演算とSN比向上のための積算を、毎秒約1ギガバイトのデータ処理速度で光学イメージの撮影と同時に実行できる高速の画像演算装置を新たに開発した。これを高解像度・高フレームレートのCMOSカメラと組み合わせることで、ゲート変調イメージの解像度と単位時間当たりの積算回数を、これまでの11万画素・毎秒15回から415万画素・毎秒45回へと大幅に向上させた。イメージのSN比は積算回数の平方根に比例するので、単位時間当たりの積算回数の増加により測定感度が向上する。また、大幅な高解像度化により、一括検査できる面積が大幅に増加する。今回、広視野光学系と高輝度LEDを組み合わせることで、一括検査できる面積を従来の1 mm角から3 cm角に向上させた。これは、画素密度150 ppiのバックプレーンの場合、TFT約30,000素子に相当する。

|

|

図1 ゲート変調イメージング装置の概略と、TFTの駆動状態を可視化する仕組み |

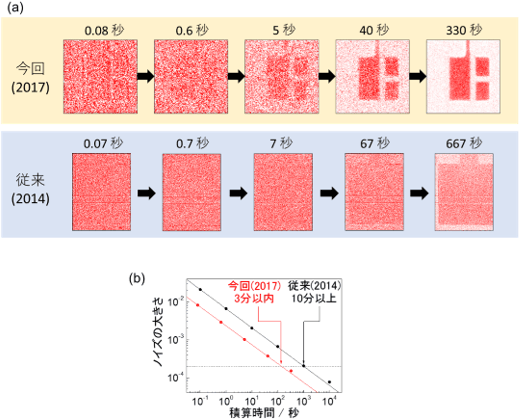

図2にゲート変調イメージと、そのノイズの大きさの積算時間依存性を示す。2014年に開発したこれまでの装置では、十分なSN比のゲート変調イメージを得るのに10分以上かかっていたのに対し、今回開発した装置では3分以内に、これまでと同程度のSN比のイメージを得ることができた。

|

|

図2 (a)ゲート変調イメージと、(b)そのノイズの大きさの積算時間依存性 |

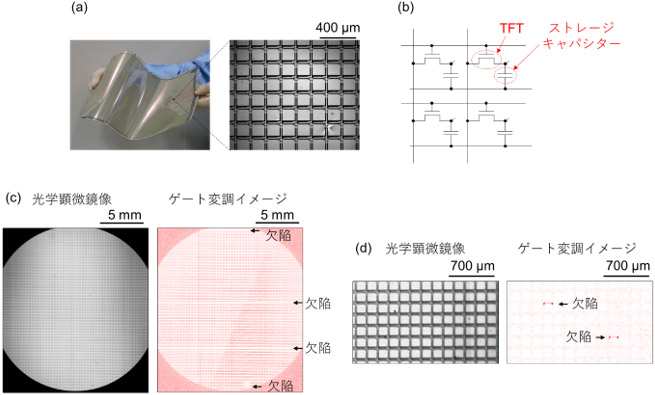

今回開発したゲート変調イメージング装置を用いて、各画素にひとつのTFTとひとつのストレージキャパシターを配置したアクティブバックプレーン(画素密度150 ppi、全印刷により製造)の検査を行った(図3)。まず、アクティブバックプレーン(図3(a)、3(b))に液晶表示素子(フロントプレーン)を装着して表示試験を行い、不良個所を大まかに特定した後に、フロントプレーンを取り除いて、ゲート変調イメージング装置により測定した。

動作不良のTFTを特定する通常の測定モード(TFT欠陥検出モード)で測定を行った結果を図3(c)に示す。図の四隅の影を除いた部分が、4 cm2の面積範囲(TFT15,000素子に相当)について測定した結果に対応する。小さな赤い点のひとつひとつが正常動作するTFTに生じた光反射率変化によるもので、色調が変化していない部分が動作不良のTFTに対応する。ゲート変調イメージング装置により特定した不良個所は、表示試験により特定したものとよく対応していた。このように、広い範囲に含まれる多数のTFTを一括検査し、動作不良のTFTを特定することができる。

さらに、ストレージキャパシターの絶縁不良を特定する測定モード(キャパシター欠陥検出モード)による検査結果を図3(d)に示す。この測定モードでは、絶縁不良のキャパシターと同じ画素に配置されたTFTがゲート変調イメージに色調変化を与えるため、絶縁不良個所を検出できる(図中の赤点)。今回開発した装置により、動作不良のTFT素子だけでなく、絶縁不良のキャパシターについても、広い面積範囲を一括検査できる。

|

図3 (a)全印刷により製造した画素密度150ppiのアクティブバックプレーン、(b)アクティブバックプレーンの等価回路図、(c)アクティブバックプレーンをTFT欠陥検出モードで測定したゲート変調イメージと光学顕微鏡像、(d)キャパシター欠陥検出モードで測定したゲート変調イメージと光学顕微鏡像

(c)(d)の黒矢印は欠陥個所を示す。(c)の四隅の影は、測定装置のカメラマウントによる。 |

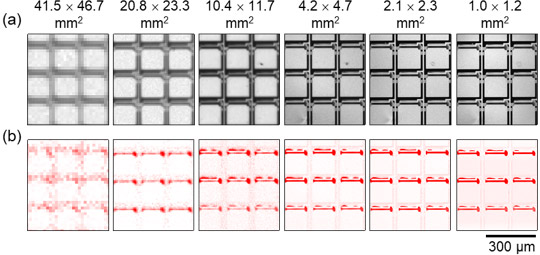

ゲート変調イメージング技術により一括検査できる面積は、カメラの解像度により決まる。今回開発した装置では、4,147,200画素のCMOSカメラを用いており、検査面積が3 cm角のときの空間分解能は約10 µmとなる。これは画素密度150 ppiのアクティブバックプレーンのTFTの寸法と同程度である。このため、検査面積が3 cm角を超えると解像度が不足して個々のTFTを識別できなくなる(図4)。このように、今回開発したゲート変調イメージング装置では、150 ppiのアクティブバックプレーンの場合には、最大3 cm角の範囲のTFT(とストレージキャパシター)約30,000素子を3分以内に一括検査できる。

|

|

図4 検査面積を変えて撮影した同じ箇所のゲート変調イメージ |

今後は、今回開発したゲート変調イメージング技術を用いた非破壊インライン検査技術により、電子ペーパーなどをターゲットとした印刷製造ラインへの実装に向けた実用化研究に取り組む。