国立研究開発法人 産業技術総合研究所【理事長 中鉢 良治】(以下「産総研」という)先進パワーエレクトロニクス研究センター【研究センター長 奥村 元】SiCパワーデバイスチーム 原田 信介 研究チーム長らのグループは、富士電機株式会社との共同研究で、炭化ケイ素(SiC)半導体を用いた1200 V(ボルト)耐電圧(耐圧)クラスのトランジスタである縦型MOSFETとして、低いオン抵抗と内蔵ダイオードの高い信頼性を両立した独自構造のデバイス(SWITCH-MOS:SBD-Wall Integrated Trench MOS)を開発し、量産レベルの試作品で性能を実証した。

SiCデバイスだけを用いたパワーモジュール(オールSiCモジュール)により、電力変換(直流・交流変換や電圧変換)が大幅に高効率化すると考えられている。その低コスト化、高信頼性化にはSBD(ショットキーバリアダイオード)内蔵型MOSFETを用いることが有効とされているが、これまで3300 Vクラス以上の比較的高い耐圧のMOSFETでだけ信頼性向上の効果が実証されていた。今回開発したSWITCH-MOSはトレンチ型MOSFETにトレンチSBDを内蔵することで、1200 Vクラスの低い耐圧デバイスでも高い信頼性が実証できた。従来技術では信頼性向上の効果が低いために1200 V耐圧クラスでは困難であったSiC-MOSFETとSiC-SBDの一体化が量産試作レベルで実証できたので、今後はハイブリッド電気自動車(HEV)/電気自動車(EV)の電力変換システムでの使用が期待されるオールSiCモジュールの市場導入が大幅に前進すると期待される。

この成果の詳細は、米国サンフランシスコ市で開催のIEDM 2017(International Electron Device Meeting)にて2017年12月4日(現地時間)に発表された。

|

|

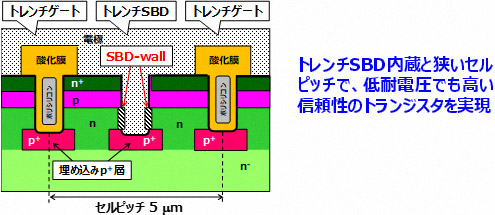

今回開発したトランジスタ(SWITCH-MOS)の断面模式図 |

エネルギーの有効利用を促進し低炭素社会の実現を目指していくには、電力の変換(直流・交流変換や電圧変換)や制御を担うパワーエレクトロニクス(パワエレ)技術を進展させ、パワエレ電力機器を飛躍的に効率化、小型軽量化、高機能化することが求められている。特に自動車産業では、HEV/EVの普及が加速度的に進むと見込まれ、モーター制御に用いられる1200 V耐圧クラスのパワーモジュールの高効率化、小型化が競争力に直結する重要なキーテクノロジーと考えられている。これまでのパワーモジュールはSi (シリコン)デバイスのIGBTやダイオードが使われてきたが、デバイス性能はSiの材料物性で決まる理論限界に近づきつつあり、今後の大幅な性能向上は望めない。ワイドギャップ半導体であるSiCは高い絶縁破壊電界強度などパワーデバイスの小型化、高効率化に有利な物性をもつためSiCデバイスを用いたパワーモジュールの開発が求められていた。

産総研はパワーエレクトロニクスを、産総研が大学や研究機関4機関と連携するオープンイノベーション拠点 TIAの戦略的研究領域の一つと位置付け、SiCパワーデバイスの量産試作ラインを整備し、民活型共同研究体「つくばパワーエレクトロニクスコンステレーション(TPEC)」を発足させ、SiCパワーデバイスの量産試作技術開発に関する共同研究を推進してきた。富士電機株会社との共同研究ではこれまで独自構造のSiCパワーMOSFET(トランジスタ)として、第1世代のプレーナー型MOSFET(IE-MOSFET)、第2世代のトレンチ型MOSFET(IE-UMOSFET)を開発し、量産試作を実証してきている。今回はSiCパワーデバイスのボリュームゾーンと目される1200 Vクラスでの高性能化、高機能化を目指し、IE-UMOSFETを基本構造としたSBD内蔵タイプのデバイス開発を行った。

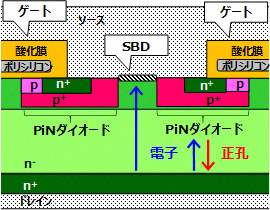

図1にSBD内蔵MOSFETの一般構造を示す。パワーモジュールを構成するSiC-SBDの代わりにSiC-MOSFETに構造的に内包されているPiNダイオードが使えればSBDが不要となり低コスト化できるが、SiCのPiNダイオードには順方向に電圧をかけていると電流が徐々に低下してしまう順方向劣化があり、信頼性に問題があった。これは電流を構成する電子と正孔が、ウエハー内の転位で再結合し消滅する現象である。これに対して、SBD内蔵MOSFETは、SBDの電流が電子だけなのでダイオードの順方向劣化が無いと期待されていた。しかしながら、順方向電圧が上昇し、内蔵PiNダイオードにかかる電圧(VPiN)がある値を超えると、PiNダイオードの動作が始まり順方向劣化を引き起こすので、開発のポイントは如何にしてVPiNを抑えて、PiNダイオードを不活性化するかであった。

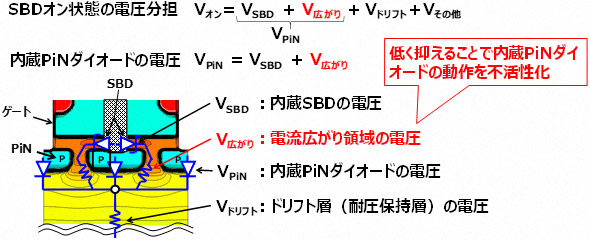

図2に開発したSWITCH-MOS(SBD-Wall Integrated Trench MOS)の構造、及び内蔵ダイオードに順方向電圧をかけたときの電圧分担を示す。耐圧保持領域となるドリフト層の電圧分担(Vドリフト)を大きくすれば、その分VPiNが下げられ効果的であるが、その効果は高い耐圧クラスのデバイスに限られる。今回、Vドリフトが小さい低い耐圧クラスにおいてもVPiNを抑えられるよう、VPiNがSBD部の電圧分担(VSBD)と P型領域周囲の電流広がり領域の電圧分担(V広がり)の和に等しいことに着目し、V広がりの低減を目指した。V広がりを低減させるためには、セルピッチを小さくすれば良いので、開発したSWITCH-MOSはセルピッチの狭い低オン抵抗のトレンチ型MOSFETのIE-UMOSFETを基本構造として、トレンチゲートの電界緩和層の埋め込みp+層上にトレンチを形成し、その側壁にSBD-wallを内蔵した。その結果、SBDを内蔵してもIE-UMOSFET単体と比べて必要なエリアが拡大することなく5 µmのセルピッチが保たれるので、p型領域幅を最小限に抑えてV広がりを低減できた。

|

|

図1 ショットキーバリアダイオード(SBD)内蔵MOSFET(トランジスタ)の一般構造 |

|

|

図2 今回開発したデバイスSWITCH-MOSの内蔵ダイオードがオン状態における電圧分担 |

|

|

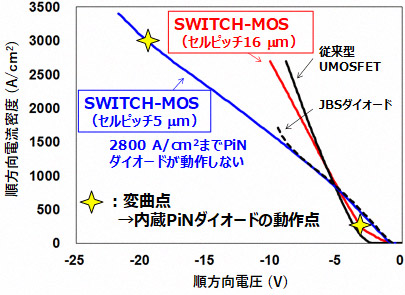

図3 今回開発したデバイスSWITCH-MOSの内蔵ダイオードの順方向電流―電圧特性 |

図3中の変曲点(黄色十字)に示すように、1200 V耐圧クラスのSWITCH-MOSでセルピッチが16 µmと広い場合はPiNダイオードが約300 A/cm2の低い電流密度で動作を開始してしまい、SBDを内蔵しない従来型UMOSFETとほぼ同じ電流-電圧特性を示したが、セルピッチが5 µmと狭いSWITCH-MOSではV広がりが抑制されており、電流密度2800 A/cm2までPiNダイオードの動作を不活性化できた。

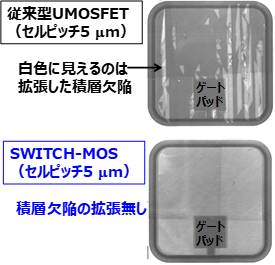

図4は順方向劣化試験後のフォトルミネッセンス像であるが、従来型トランジスタUMOSFETはPiNダイオードが動作して順方向劣化したため積層欠陥が拡がっているのに対し、今回開発した独自デバイスであるセルピッチ5 µmの SWITCH-MOSは、積層欠陥の拡がりがなく順方向劣化していないのが分かる。今回開発したセルピッチ5 µmの SWITCH-MOSでは、これまで問題であった1200 V耐圧クラスのSiC-MOSFETのPiNダイオードの順方向劣化問題が解消され、高い信頼性が実現したと言える。

|

|

図4 今回開発したデバイスSWITCH-MOSの順方向電流ストレス後のフォトルミネッセンス像 |

企業での事業化を念頭に企業連携を更に強化し、デバイス構造多層化などの複雑化や、製造プロセスの高度化を進めると同時に、パッケージング技術などの周辺技術開発も進める。