国立研究開発法人 産業技術総合研究所【理事長 中鉢 良治】(以下「産総研」という)スピントロニクス研究センター【研究センター長 湯浅 新治】金属スピントロニクスチーム 薬師寺 啓 研究チーム長は、次世代のメモリーデバイスであるスピントルク書込型磁気ランダムアクセスメモリー(STT-MRAM)に用いられる垂直磁化トンネル磁気抵抗(TMR)素子の記憶安定性を従来の2倍に向上させた。

垂直磁化TMR素子は、情報記憶を行う「記憶層」と、記憶層情報の判定基準である「参照層」により構成され、記憶層には記憶した情報を失わない強固さ(記憶安定性)が求められる。今回開発した垂直磁化TMR素子では、イリジウム層と極めて薄いコバルト層からなる界面構造を記憶層の一部に用いて、記憶安定性を従来の2倍に向上させた。従来の半導体メモリー(DRAM)を代替するには、20ナノメートル(nm)以下の素子サイズが必要とされるが、今回の成果により、素子サイズ19 nmの超高集積化STT-MRAMの実現が見込まれ、データストレージやモバイルデバイスといった製品化への応用が期待される。

なお、この成果は、近くApplied Physics Expressのオンライン版へ掲載される。

|

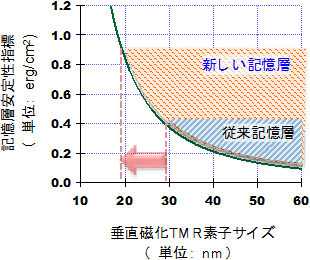

記憶層の安定性と作製可能な垂直磁化TMR素子サイズの相関図

今回開発した新しい記憶層では、記憶層安定性指標を従来比2倍に強めたことで19 nmサイズを可能にした。 |

TMR素子をベースとするSTT-MRAMは、不揮発、高速、高書き換え耐性などの特徴を持ち、特に不揮発性によって記憶維持のための電力が不要になることから、省エネルギー型の新世代ユニバーサルメモリーとして注目を集めている。これまでに垂直磁化TMR素子をベースとしたSTT-MRAMの高いポテンシャルが国内外で広く実証され、現在は、デバイス応用を実現するための技術開発が精力的に進められている。デバイスとしては、不揮発性を活かした、ストレージと組み合わせた周辺メモリーや、従来の半導体メモリー(DRAM)を凌駕する大容量メインメモリーが想定されている。しかし、STT-MRAMでは、素子サイズを小さくするほど記憶安定性を確保することが難しくなる。現在、国内外で主流とされている垂直磁化TMR素子の構造や材料では、30 nmサイズを境に記憶安定性の頭打ちが見られ、DRAM代替に必要な20 nm以下のサイズは困難となっている。

産総研は、大容量STT-MRAMを実現するための中核技術である、高性能垂直磁化TMR素子の研究開発を行っている。2008年に株式会社 東芝らと共同で、垂直磁化TMR素子をベースとしたSTT-MRAMの試作に世界で初めて成功して以来、国内外をリードするSTT-MRAM開発を進めている。現在では、おおよそ30 nmのサイズにまで記憶素子を小さくして、より応用に向けてインパクトの高い、DRAM代替向けSTT-MRAMの開発を精力的に行っている。しかし、現在主流の垂直磁化TMR素子の構造や材料では、30 nmサイズを境に記憶安定性の頭打ちが見られる。そこで、新たな構造や材料によって記憶安定性を向上させる研究開発を進めることとした。

なお、本研究開発は、国立研究開発法人 科学技術振興機構 戦略的創造研究推進事業(さきがけ)「新物質科学と元素戦略」(研究総括:細野 秀雄)研究課題名「単原子層デザインによる希少金属フリー超高磁気異方性薄膜の開発」(研究代表者:薬師寺 啓)の支援を受けて行った。

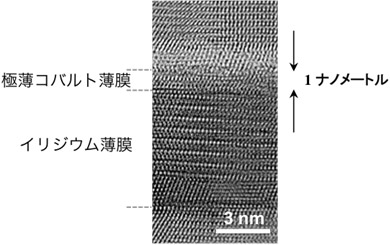

今回、記憶層にイリジウム薄膜と極薄のコバルト薄膜を導入した。これまで、イリジウム薄膜とコバルト薄膜が重なった場合、両者が混ざりやすいことが問題であった。今回、薄膜成膜条件を工夫した成膜技術を開発することにより、原子レベルでの混じり合いを抑制し、極めてシャープな界面を形成した。図1に実際に形成した薄膜構造の電子顕微鏡像を示す。イリジウム薄膜上に形成されたコバルト薄膜の厚さはわずか1 nmである。

|

|

図1 イリジウム薄膜とその上に形成した極薄コバルト薄膜断面の電子顕微鏡像 |

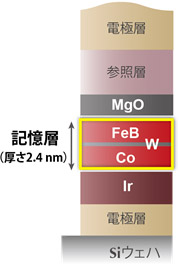

今回開発した垂直磁化TMR素子全体の薄膜構造を図2に示す。シャープな界面をもつイリジウム薄膜と極薄コバルト薄膜を素子の下部に形成し、その上に各薄膜を積層してある。記憶層は、黄色で囲ったコバルト(Co)/タングステン(W)/鉄ボロン(Fe-B)の3層一体で構成され、この一体となった記憶層が最終的にはSTT-MRAMの1つのメモリーとして機能する。今回のイリジウム薄膜と極薄コバルト薄膜のように、これまでの垂直磁化TMR素子に用いられていない材料や構造を採用する場合には、従来の垂直磁化TMR素子が持っているさまざまな特性を失わずに、新しい性能を上乗せすることが求められる。今回の素子でもこの点を重視し、図2に示したようにコバルト薄膜の上にタングステンを挿入して、従来の垂直磁化TMR素子と同等の低い素子抵抗(RA)値と高い磁気抵抗(MR)比を両立させている。記憶安定性は記憶層の「体積」と「異方性エネルギー」の積により決まる。今回の素子では、異方性エネルギーを従来の約2倍に向上させることで、記憶層の体積を変えること無く記憶安定性を2倍に向上させた。この特性は19 nmサイズのSTT-MRAMを実現しうる。また、20 nm以下の素子サイズに求められる低素子抵抗の特性を満たしている。これらにより、大容量STT-MRAMの実用化開発が大きく加速されると期待される。

|

|

図2 今回開発した垂直磁化TMR素子の断面構造模式図 |

今回開発した成膜技術は、他の材料・結晶配向を持つ垂直磁化膜層にも適用でき、幅広い応用の可能性をもつ。今後は、この技術をベースにさらに高い記憶安定性(「記憶層の安定性と作製可能な垂直磁化TMR素子サイズの相関図」の縦軸で大きい数値方向)の実現に努め、大容量STT-MRAMの量産化技術の確立を目指す。