国立研究開発法人 産業技術総合研究所【理事長 中鉢 良治】(以下「産総研」という)ナノエレクトロニクス研究部門【研究部門長 安田 哲二】ナノCMOS集積グループ 大内 真一 主任研究員、柳 永勛 上級主任研究員、松川 貴 研究グループ長、エレクトロインフォマティクスグループ 堀 洋平 主任研究員は、半導体ICチップの偽造を防ぐ「ICの指紋」を低コスト、高信頼性、コンパクトに実現できる素子とそれを用いた回路技術を開発した。

ここでいう「ICの指紋」技術とは、人間の指紋が個人の識別に使えるように、ICチップ作製時に自然に発生するばらつきを利用し、複製できない素子・回路によって、チップに固有の番号を発生させる技術のことである。チップ作製直後にこの固有番号を秘密鍵として安全な場所に保存し、認証に用いれば、不正なリサイクルチップや偽造チップによる事故や不正アクセスを防止できる。今回、多結晶シリコンFinFETを用いて「ICの指紋」を発生させる回路をICチップ自体の中に形成する技術を開発した。通常のIC用トランジスタを用いる場合に比べて3倍以上の動作安定性で固有番号を発生できるため、コンパクトな回路でより確実にチップの真贋判定・認証ができる。また、通常の素子からなるICチップの回路と多結晶シリコン素子の「指紋」発生回路を同時に作れるため、従来よりも低コスト化できる。将来的には、IoTなどで機器の成りすましを防止する技術としても期待される。

なお、この技術の詳細は、12月9日(米国現地時間)に「国際電子デバイス会議」(2015 International Electron Devices Meeting;IEDM、ワシントンD.C.)にて発表される。

|

|

今回開発した多結晶シリコンFinFETを用いた「指紋」素子・回路技術 |

現在、ビジネス向け大型計算機、車載エレクトロニクスデバイスや医療機器など、高い信頼性が求められる電子機器だけではなく、携帯電話や家電まで、あらゆる分野でICチップの信頼性、安全性に対する需要が高まっている。一方で、2013年度の日本国内企業の模造品・模倣品による被害額は、1,100億円以上に上るが、その被害件数の10 %が電子・電気機器であり、特に被害額が10億円以上の案件では、電子・電気機器の被害件数は第2位である(特許庁、2014年度模倣被害調査報告書)。このような模造品・模倣品による被害は、経済的損失だけではなく、不十分な品質による動作不良が引き金となる事故の発生、マルウエアの混入による乗っ取りや成りすましなど、社会生活の安心・安全を脅かす危険性がある。特に、家電など幅広く電子制御が導入されている今日、ICチップの不正なリサイクルや偽造などによる模造品・模倣品が市場に持ち込まれることを防止することが求められている。また、今後IoTが普及してゆくであろうことから、機器の制御を行うICチップの真贋判定は、機器の成りすましや乗っ取りなど悪意ある複製品への対策として、今後ますます重要になると考えられる。

産総研は、電界効果型トランジスタを3次元立体構造にしたFinFET(フィン型FET)を開発してきた。これは、2012年にインテルが実用化して以来、最先端のCMOS技術として、高機能で高価なICチップに用いられている。さらに、多結晶シリコンを用いたFinFET型の素子技術の研究開発に取り組んできた。

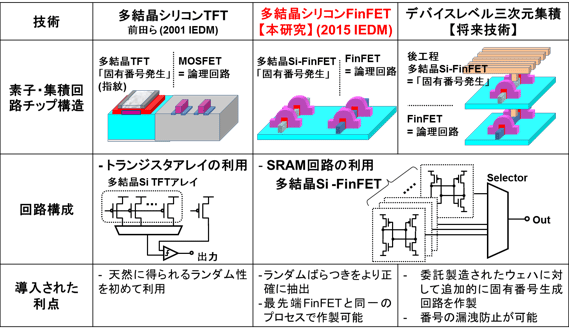

一方、多結晶シリコン素子による「ICの指紋」技術は2001年に初めて提唱されたが、通常型トランジスタとは異なる薄膜トランジスタ構造であったため、製造工程が複雑であり、また工程の不安定性に動作が影響される回路の構成であった。今回、産総研で培われた多結晶シリコン素子技術を発展させ、「ICの指紋」機能を実現するための研究開発に取り組んだ。

今回開発した「指紋」発生回路は、「指紋」となるICチップの固有番号を、多結晶シリコンFinFETで構成したSRAM回路によって発生する。このSRAM回路の起動時の初期値が0になるか1になるかは、製造時の素子性能のばらつきを反映して決まり、起動ごとに同じ値を示す。「指紋」発生回路には複数のSRAM回路が用いられ、SRAM回路数のビット数の番号を発生させることができる。個々のSRAM回路の初期値は製造工程でランダムに決まるため、発生した番号はICチップに固有の番号となる。固有番号ビット数を多くすれば同じ固有番号を持つ確率は小さくなるので、そのICチップを複製や偽造できない。

|

|

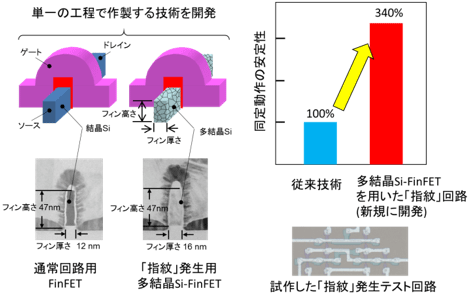

図1 「指紋」発生回路用の多結晶シリコンFinFETの模式図(左上)と断面の電子顕微鏡写真(左中央)、試作した「指紋」発生テスト回路(左下) |

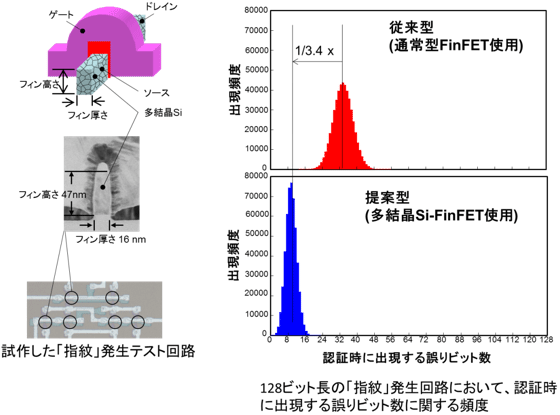

今回、多結晶シリコンFinFETを用いたSRAM回路方式の「指紋」発生テスト回路と、比較のため通常型FinFETで「指紋」発生テスト回路を試作した(図1左)。多結晶シリコンFinFET素子とこれを用いた「指紋」発生テスト回路の実験に基づき、128ビット長の「指紋」発生回路において現れる、本来の固有番号と異なるビット(誤りビット)のビット数を見積もった。その結果、図1右に示すように、平均誤りビット数は、通常型FinFETで作製した回路の3分の1以下に低減することが示唆された。すなわち、多結晶シリコンFinFETを用いた「指紋」発生回路は通常型FinFETの回路の3倍以上の安定性で固有番号を発生でき、高い確度でICチップの認証や同定ができる。通常型FinFETの回路で128ビットの固有番号を同等の安定性で発生させる場合にくらべ、多結晶シリコンFinFETの導入によって、少なくとも約15,000トランジスタ分の回路を省略できると見積もられる。これは、22 nmテクノロジー換算で、約1,100 μm2の面積縮小に相当する。

さらに本技術は、従来の多結晶シリコン薄膜トランジスタ技術とは異なり、低コストで集積回路化が可能である。本技術で「指紋」の発生に用いられる多結晶シリコンFinFETは、作製工程の初期段階にIC基板の一部に多結晶シリコン薄膜を堆積させた後、標準的なFinFET素子と同一の製造工程で同時に形成されるため、工程が短く終了し、低コスト化につながる。また回路構成の観点からは、半導体メモリーの1つであるSRAM回路によって「指紋」を発生させることによって、製造工程の条件が変化した場合でも発生される固有番号に偏りが生じない。

|

|

図2 今回開発した技術と関連技術、将来像の比較 |

今後は、製造工程の後工程で認証用回路のトランジスタを挿入する、デバイスレベル三次元構造への適用を検討していく(図2将来技術)。これにより、トランジスタ製造を外注した際に生ずる、固有番号の第三者への漏洩の危険性を低減できるほか、コストの最適化が期待される。また、今後盛んになるであろうIoTの端末への適用技術を開発していく。