国立研究開発法人 産業技術総合研究所【理事長 中鉢 良治】(以下「産総研」という)フレキシブルエレクトロニクス研究センター【研究センター長 鎌田 俊英】フレキシブル材料基盤チーム 堤 潤也 研究員、同研究センター 長谷川 達生 総括研究主幹らは、有機トランジスタの性能分布を光学イメージとして一括して評価できる新たなデバイス評価技術を開発した。この技術により、電子ペーパーやディスプレイなどの、膨大な数のトランジスタの配置が必須である情報端末機器の製造工程で、各素子の検査に要する時間を大幅に短縮できる。

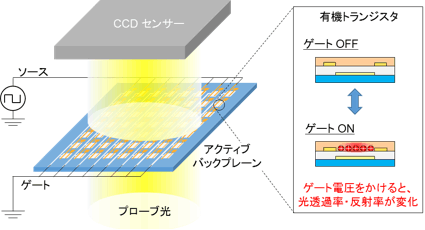

情報化社会の進展とともに、ディスプレイなどの情報端末の各画素のオン/オフを制御するアクティブバックプレーンの製造技術の進化が強く求められている。大面積化・省エネルギー化が可能な印刷技術を用いたデバイス製造技術(プリンテッドエレクトロニクス技術)は、最も有望なソリューションとして期待されるが、膨大な数(通常数百万個以上)のトランジスタがアレイ状に配置されたアクティブバックプレーンを短時間で性能検査することは難しく、これが生産技術として導入される上での大きな障害となっていた。今回、有機トランジスタにゲート電圧をかけた時に生じる半導体の光透過率・反射率の微小な変化をCCDセンサーで撮影して、デバイス性能の分布を光学イメージ化するゲート変調イメージング(Gate Modulation Imaging: GMI)技術を開発した。この技術によりアクティブバックプレーンを構成する膨大な数の有機トランジスタの性能分布を一括して評価できる。

なお、この技術の詳細は、欧州科学誌Organic Electronicsに近く掲載される。

プリンテッドエレクトロニクス技術は、ディスプレイやシート状センサーなどの大面積の電子機器を製造する際に、大規模な真空設備を必要としないこと、ロール・トゥー・ロールプロセスによる高い生産性が期待できることから、今後のエレクトロニクス産業に大きな変革をもたらすと期待されている。

このような全く新しいデバイス製造技術を実用化するには、再現性が良く均一なデバイス特性を得るための技術の高度化が必須である。特に、アクティブバックプレーンの製造工程では、数百万個ものトランジスタの性能分布評価が必要であるため、全素子の性能を高速に一括して評価できる新概念の検査技術が必要とされている。

産総研では、プリンテッドエレクトロニクス技術の実用化を目指した研究開発を幅広く行っている。その一環として、印刷法を用いたアクティブバックプレーンの製造技術の開発と、これに対応できる高速なデバイス性能評価技術の開発を進めてきた。数百万個のトランジスタで構成されるアクティブバックプレーンの検査を行うには、従来の電気測定に基づく検査方法では時間がかかりすぎて、現実的ではない(1素子に1分としても2年かかる)。また、液晶ディスプレイに用いられる一括検査法では、ディスプレイのドット抜けの原因となる欠陥素子は検出できるが、輝度むらや表示速度低下に影響する素子性能(移動度、応答速度)の分布評価までは難しかった。そこで、産総研では、アクティブバックプレーンを高速に一括して性能評価するため、ゲート電圧をかけることにより有機トランジスタに生じる光透過率・反射率の微小変化を可視化する技術の開発を進めてきた。

なお、この研究の一部は、国立研究開発法人 科学技術振興機構の戦略的イノベーション創出推進プログラム(S-イノベ)「新しい高性能ポリマー半導体材料と印刷プロセスによるAM-TFTを基盤とするフレキシブルディスプレイの開発」による支援を受けて行った。

図1に、今回開発したゲート変調イメージング法の概略図を示す。有機トランジスタにゲート電圧を与え、キャリアを蓄積すると、有機半導体層の光透過率・反射率がごくわずか(1万分の1程度)変化する。ゲート変調イメージング法では、アクティブバックプレーンに配置された全てのトランジスタに対して、ゲート電圧をかけた状態とかけてない状態の光学イメージをそれぞれ撮影し、両者の差を画像処理して、微小な変化のイメージ(ゲート変調イメージ)を高感度に得る。ゲート変調イメージには、正常動作するトランジスタだけが現れるため、配線不良や半導体層の欠陥による動作不良個所を一括して特定できる。

|

|

図1 ゲート変調イメージング法の概略図 |

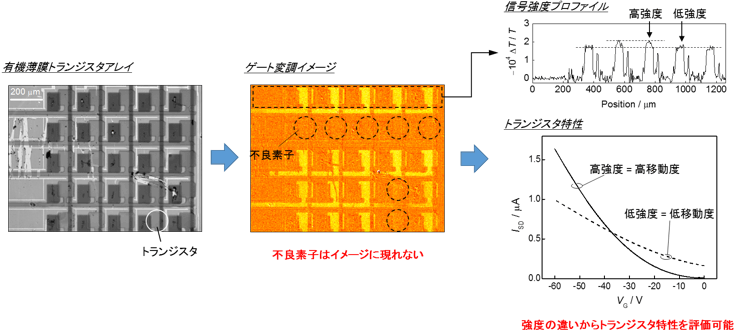

図2に、実際の有機トランジスタアレイのゲート変調イメージを示す。黄色い部分が正常動作するトランジスタに生じた光透過率変化によるもので、黄色に色調が変化していない部分は動作不良のトランジスタに対応する。さらに、ゲート変調イメージの信号強度とトランジスタ特性の間には、明瞭な相関があり、高強度の信号がトランジスタの高移動度に、低強度の信号がトランジスタの低移動度に対応している。すなわち、ゲート変調イメージの信号強度から、ディスプレイの輝度のむらに関わるトランジスタの移動度の分布を一括して調べることができる。

|

|

図2 有機トランジスタアレイのゲート変調イメージング測定結果 |

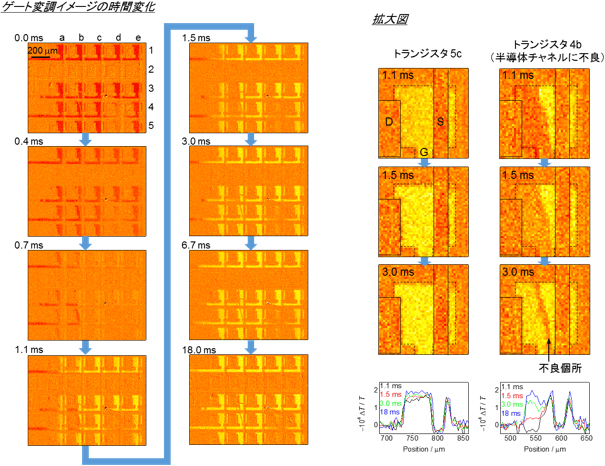

さらに、ゲート電圧をかけてから撮影するまでの時間を変えてゲート変調イメージを測定すると、トランジスタが駆動するまでに要する時間を調べることができる。図3左より、ゲート電圧をかけた後に徐々にトランジスタが駆動状態に移行する様子が分かる。図3右の拡大図より、半導体チャネル内に不良箇所があるトランジスタでは、不良箇所がないものよりもチャネル全体のキャリアの蓄積に時間がかかるので、応答が著しく遅くなる。このようにゲート変調イメージの時間変化から、ディスプレイの表示速度に関わるトランジスタの応答速度の分布を調べることができる。

|

|

図3 ゲート変調イメージの時間変化 |

今回開発したゲート変調イメージング法の特徴は、アクティブバックプレーンなどの多数のトランジスタの性能分布を一括して検査できることにある。一般的な400万画素のCCDセンサーを使って200 ppiのアクティブバックプレーンの検査を行う場合、イメージングの視野を1 cm2とすると、1回の撮影(10分程度)により6200個のトランジスタを一括して検査できる。さらに、より高速なセンサーを多数(例えば400個)配置し、これらを用いた一括検査を行えば、250万個以上のトランジスタが集積したアクティブバックプレーンの全トランジスタの性能を数分以内に非破壊で検査できるようになる。

今後は、ゲート変調イメージング技術の高速・高感度化、検査範囲の大面積化を進め、生産ラインへの実装に向けた実用化研究に取り組む。