独立行政法人 産業技術総合研究所【理事長 中鉢 良治】(以下「産総研」という)ナノエレクトロニクス研究部門【研究部門長 金丸 正剛】連携研究体グリーン・ナノエレクトロニクスセンター【連携研究体長 横山 直樹】臼田 宏治 特定集中研究専門員らは、大規模集積回路(LSI)の3次元積層技術に向けた多結晶ゲルマニウム(Ge)トランジスタのp型動作とn型動作の両方を実現し、多結晶Ge-CMOSが実現可能であることを示した。

多結晶Geは、広く用いられている多結晶シリコン(Si)に比べ、より低温(500 ℃以下)で形成することができる。そのため、集積回路上に熱的ダメージを与えずにCMOS回路を直接積層することが可能であり、3次元LSIの要素技術として有望である。さらに、Ge中の電子と正孔の移動度はSiよりも高いために、高性能化や低電圧動作が期待される。しかし、p型トランジスタの動作は実現していたが、これまでn型トランジスタの動作報告例はなく、CMOS回路の実現性は不明であった。今回、多結晶Geの結晶品質を向上させることで初めてnMOSFETの動作を実現し、多結晶GeのCMOS化が可能であることを示した。さらに、pMOSFETでは、単結晶Si-pMOSFETに匹敵する、従来の3倍近い電流駆動力を達成した。これらの成果から、高性能多結晶Ge-CMOSを積層した3次元LSIの実現と、それによるLSIの大幅な小型化と高機能化、低消費電力化が期待される。

なお、この技術の詳細は、2013年12月11~13日(米国東部時間)に米国メリーランド州Bethesdaで開催される2013 International Semiconductor Device Research Symposiumで発表される。

|

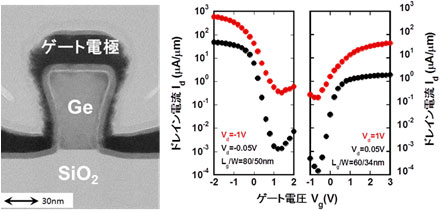

| 作製した多結晶Geトランジスタの断面構造と、pMOSFETおよびnMOSFETの特性 |

携帯情報端末の爆発的な普及やIT機器の高機能化に伴う消費電力の増大により、電子情報機器の消費電力低減が求められている。そのためには、これらに搭載されているLSIを構成する個々のトランジスタに供給する電圧(電源電圧)を低くすることが重要である。従来、LSIの高性能化・低消費電力化はトランジスタの微細化によってもたらされてきた。しかし、近年、微細化の副作用である漏れ電流の増加や細い配線による抵抗の増大、トランジスタ自体の性能の頭打ちなどに対処するために新たなプロセス技術の開発や設備導入が必要となり、技術的、経済的に微細化が困難となってきている。一方、複数のLSIを積層した3次元的な集積回路は、微細化技術によらずに、チップ面積の縮小や高機能化、配線遅延の低減による省電力化などの効果が得られる。現状では別々に作成したLSIチップを薄膜化して積層する手法が開発されているが、コストが高く、配線の密度が十分に高められないといった問題がある。そこで、新たな3次元積層技術として、多層のCMOS集積回路を連続的に形成できる積層CMOS技術が求められている。

連携研究体グリーン・ナノエレクトロニクスセンター(GNC)は、内閣府と独立行政法人 日本学術振興会によって運営される最先端研究開発支援プログラム(FIRST)に採択されたプロジェクトを実施するために平成22年4月に設立された。企業5社(富士通株式会社、株式会社 東芝、株式会社 日立製作所、ルネサスエレクトロニクス株式会社、株式会社 アルバック)からの出向研究者と産総研研究者によって構成されている。GNCでは平成23年度より、LSIの低電圧動作を目指して、高移動度材料であるGeを用いたトランジスタの研究開発を行ってきた。一方で、多結晶Geが低温で絶縁膜上に形成可能であることに着目し、多結晶Geによる積層CMOSの開発を平成24年度より開始した。

今回、多結晶Ge-nMOSFETの動作に初めて成功し、既に動作確認済みのpMOSFETと組み合わせることでCMOS回路の形成が可能であることが実証された。本研究成果は、FIRSTのプロジェクト「グリーン・ナノエレクトロニクスのコア技術開発」(中心研究者:横山 直樹)の助成により得られたものである。

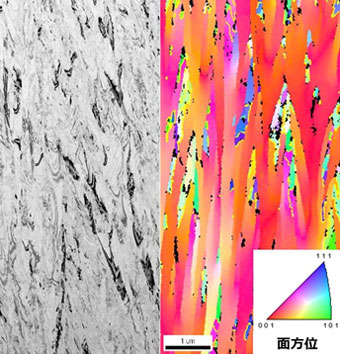

トランジスタを形成する多結晶Ge膜は、Si基板上に熱酸化膜(SiO2)を形成し、その上に、スパッタリング法によって非晶質Ge膜を堆積し、熱処理によって結晶化させて形成した。今回、フラッシュランプ・アニール(FLA)法により熱処理をしたため、従来の加熱炉での長時間熱処理に比べて結晶性を向上させることができた。また、図1に示すように、長軸方向が数µmに及ぶ大きな結晶粒が生成し、200 cm2/Vsという非常に高い正孔移動度が得られた。なお、従来法での多結晶Ge膜の正孔移動度は50 cm2/Vs程度であった。また、従来法で得られた結晶粒の主軸の方位はランダムであるが、FLA法では、結晶粒の6割以上が<001>方位であった。結晶粒のサイズが大きいだけでなく、方位がそろっていることも高い移動度の要因である可能性がある。なお、この多結晶Ge膜は、不純物ドーピングをしていないが、p型伝導を示し、正孔濃度が1018cm-3台であった。Ge結晶中では、結晶欠陥が正孔の発生源として働くことが知られている。今回のGe多結晶膜では、結晶粒界などの結晶欠陥が正孔の発生源となりp型化しているものと考えられる。

|

| 図1 FLA法で作製した多結晶Ge薄膜の平面透過型電子顕微鏡像(左)と、電子線後方散乱回折法により得られた結晶主軸方位の分布図(右) |

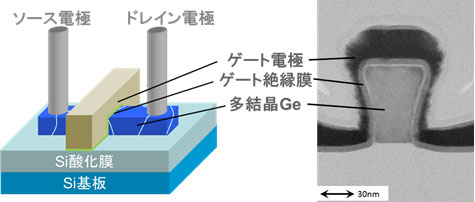

この多結晶Ge膜を用いて、図2に示すフィン型トランジスタを作製した。nMOSFET用には、電流の入り口、出口に相当する電極との接合領域にn型不純物であるリンをイオン注入し、活性化熱処理を行った。一方、pMOSFET用には、p型化のための不純物は導入せず、接合領域にニッケルとゲルマニウムの合金(NiGe合金)を形成した。チャネル部はp型であるため、nMOSFETは反転型、pMOSFETは空乏型の動作となる。FLA処理以降のプロセス温度は最高350 ℃で、これは下地に銅配線を含むCMOSがあっても、それを傷めないで済むプロセス温度である。

|

| 図2 作製したフィン型トランジスタの構造概念図(左)と、断面透過電子顕微鏡像(右) |

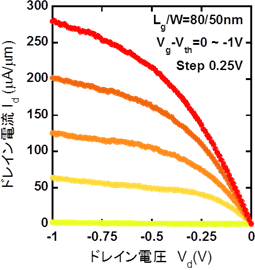

図3に、ゲート長80 nmのpMOSFETの入出力特性(ドレイン電流-ドレイン電圧特性)を示す。電源電圧1 Vでの電流値は約200 µA/µmで、これは同等のゲート長の単結晶Si-pMOSFETに匹敵する値である。これは、今回の多結晶Ge膜の高い正孔移動度と、NiGe合金による低抵抗な接合の効果によると考えられる。このように、絶縁膜上に容易に形成できる多結晶トランジスタで、従来の集積回路で用いられている単結晶Siトランジスタと同等の性能が得られたことは、従来Si基板上に形成されていたトランジスタの設計を、ほぼそのままのサイズで移植すればよいため、大きな設計変更なく積層することができることを意味している。

|

| 図3 多結晶Ge-pMOSFETの入出力特性(ドレイン電流-ドレイン電圧特性) |

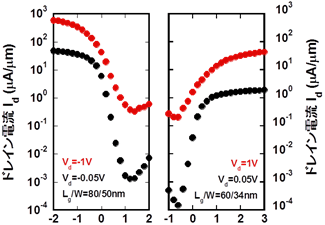

図4に作製したpMOSFETとnMOSFETの伝達特性(ドレイン電流-ゲート電圧特性)を示す。ゲート長がいずれも80 nm以下と短いにもかかわらず、どちらの極性のトランジスタもゲート電圧によってドレイン電流のオン、オフの切り替えができており、正常に動作していた。特に、多結晶Ge-nMOSFETの動作報告は今回が初めてである。両極性の動作が確認されたことから、多結晶GeトランジスタによるCMOS回路が構成可能であることが示された。

|

| 図4 多結晶Ge-pMOSFETとnMOSFETの伝達特性(ドレイン電流-ゲート電圧特性) |

今後は、多結晶GeのpMOSFETとnMOSFETを組み合わせたCMOS回路を絶縁膜上に形成し、回路動作の実証を目指す。さらに、Geの高い移動度を生かして、単結晶Si-CMOS回路を超える性能を目指す。