独立行政法人産業技術総合研究所【理事長 中鉢 良治】(以下「産総研」という)先進パワーエレクトロニクス研究センター【研究センター長 奥村 元】福田 憲司 総括研究主幹、超高耐圧デバイスチーム 米澤 喜幸 研究チーム長らのグループは、炭化ケイ素(SiC)半導体を用いて、16 kVという超高耐電圧特性を持つ独自構造の絶縁ゲートバイポーラ・トランジスタ(IGBT)を開発した。

SiC半導体は、優れた物理的・化学的性質を持ち、シリコン(Si)半導体をしのぐ小型で損失の少ないパワーデバイスの実現が可能とされている。しかし、SiC-IGBT作製に必要なp型基板は、SiC基板としては品質が悪くデバイス作製には問題があった。今回、エピタキシャル成長によってp型基板層を作製するフリップ型の技術を用いるとともに、産総研独自の技術であるSiC基板のカーボン面を利用したIE構造を採用することで、スイッチングトランジスタとして10 kV以上の超高耐電圧と低いオン抵抗の両立を図ることができた。

Siパワー半導体で到達できない10 kV以上の耐電圧と低損失性を持つパワー半導体が開発されたことで、種々の電力ネットワークにおけるスイッチやトランスの半導体化、さらには次世代スマートグリッド構築を通した電力分野での省エネルギー化への道筋が示された。

この成果は、内閣府の最先端研究開発支援プログラム(FIRST)(2010~2014年度)「低炭素社会創成へ向けた炭化ケイ素(SiC)革新パワーエレクトロニクス研究開発【中心研究者 木本 恒暢 京都大学工学研究科教授】」のもとで達成されたものであり、成果の詳細は、2013年12月9~11日(米国時間)に米国ワシントンD.C.で開催されるIEDM 2013 (International Electron Device Meeting)にて発表される。

|

|

試作したSiC-IGBTの特性測定。IGBT動作を示す発光が観測される。 |

現代社会におけるエネルギー消費の増加と電力化率の上昇のもと、エネルギーの有効利用を促進し低炭素社会の実現を目指していくには、電力の変換(直流・交流変換や電圧変換)や制御を担うパワーエレクトロニクス(パワエレ)技術を進展させ、パワエレ電力機器の飛躍的な効率化、小型軽量化、高機能化が求められている。これまでパワエレ電力機器に広く用いられてきたSi 半導体では、IGBTなどのデバイス性能向上によってパワーデバイスとしての低損失化が図られてきたが、そのデバイス性能はSiの材料物性で決まる理論限界に近づきつつあり、今後の大幅な性能向上は望めなくなっている。そこで、次世代半導体材料として、SiC半導体が注目されるようになってきた。SiC半導体は、Si半導体に比べて絶縁破壊を起こす電界強度が10倍、最大の電子走行速度が2倍、熱伝導率が3倍という優れた物性値を持つ。これをパワーデバイスに適用すれば、デバイスの高耐電圧化、高速化が実現できるとともに、熱損失をSiパワーデバイスの10分の1以下に低減できる。さらに、200 ℃以上の高温動作も可能であり、パワーデバイスを搭載した各種の電気機器、システムの大幅な効率向上と小型軽量化が達成できるとされる。

産総研では、1970年代から次世代パワー半導体材料としてのSiC半導体の研究に取り組んできたが、その長年の技術的蓄積と最先端の技術開発成果をもとに、オープンイノベーションの理念に基づく産学官連携の技術開発拠点として構築されたつくばイノベーションアリーナ(TIA-nano)にパワーエレクトロニクス技術領域が設定されている。昨今、電力エネルギーの有効活用の観点からパワー半導体への関心が飛躍的に高まっている中、TIA-nanoパワーエレクトロニクス技術領域では、産総研を中心にしてSiCパワエレ関連の多くの企業との共同研究や大型の国家プロジェクトが進行している。主として民生品を対象とする1 kV領域(第1世代)、インフラ系を対象とする5 kV領域(第2世代)、さらには電力送配電への適用を想定した10 kV以上の超高電圧領域(第3世代)の技術開発が同時並行で進められている。第3世代の技術は、デバイス構造の点で第2世代までのMOSFETとは異なり、高耐電圧化しても低いオン抵抗を実現できるIGBTを前提にしたものであり、SiCパワエレの最先端技術牽引役と位置付けられる。このSiC-超高耐電圧デバイス開発は、内閣府の最先端研究開発支援プログラム(FIRST)「低炭素社会創成へ向けた炭化ケイ素(SiC)革新パワーエレクトロニクス研究開発【中心研究者 木本恒暢京都大学工学研究科教授】」として採択され、産総研は国立大学法人 京都大学、一般財団法人 電力中央研究所と共に企業からのプロジェクト参画研究者も結集した開発拠点となっている。

第3世代技術において、同じデバイス構造を想定した場合、SiCデバイスでは従来のSiデバイスと比べて1桁以上高い耐電圧を得ることができるため、現在のSiパワーデバイスの主流であるIGBT構造を採用することにより、10 kV以上の超高耐電圧パワーデバイスを提供することが可能となる。しかし、1 kV領域のものに比べれば1桁以上厚いエピタキシャル膜が必要となる。

産総研グループはFIRSTプログラムにおいて、これまでn型高品質SiC基板を用いた超高耐電圧大容量PiNダイオードの研究開発を行い、13 kVの耐電圧と20 A動作を確認した。しかし、10 kVを超える領域の電力機器を実現するためには、ダイオードに加えトランジスタとしてp型SiC基板上に作製するSiC-IGBTが必要となる。現在n型SiC基板に関しては、第1世代の技術応用への期待が高まり6インチの大口径高品質基板が市販されるようになっている。しかしp型SiC基板に関しては、n型基板に比べて結晶欠陥密度が高く、厚いエピタキシャル膜およびその上にデバイス作製が可能な高品質のp型基板が欠如していた。

今回産総研グループは、デバイス品質の結晶作製に用いられるエピタキシャル成長によってp型基板を作製するフリップ型の基板作製方法、および過去のSiCパワーデバイスの研究開発において開発したIE構造を採用し、超高耐電圧性と低オン抵抗性を併せ持つSiC-IGBT作製を試みた。

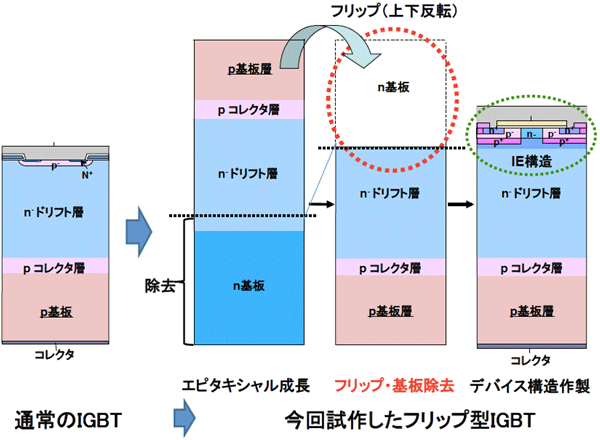

図1に、通常のp型基板上のIGBT構造と今回作製したIGBT構造を示す。高品質p型基板をエピタキシャル成長で得るために、図1に示すようなフリップ型の基板作製を試みた。

(1)高品質のn基板上に、まず超高耐圧性能を実現するのに必要な厚いn型層をエピタキシャル成長させ、その上にp型基板層をエピタキシャル成長させる。

(2)上下逆転(フリップ)させ、n型基板を取り去り、エピタキシャル成長した部分を自立させる。

さらにIGBTの制御電極(ゲート)形成では、移動度の高いカーボン面の特徴を生かせるIE構造をフリップさせたn型層の上部に作製した。IE構造では、ゲート電極直下の部分(チャネル)にエピタキシャル成長した結晶面を用いることで、通常のイオン注入による形成法に比べて高いチャネル移動度を得ることができる。

|

|

図1 従来型IGBTとフリップ型IGBTの構造の違い |

IGBTデバイス構造の試作には、TIA-nanoパワーエレクトロニクス領域のコア施設であるSiCデバイス専用試作ラインを用いた。また、SiC厚膜のエピタキシャル成長には株式会社東京エレクトロンの協力を得た。試作の結果、3 mm角のSiC-IGBTチップで耐電圧16 kV、オン抵抗11.3 mΩcm2と世界最高レベルの超高耐電圧パワーデバイス特性を確認できた。

このようなSiデバイスでは達成できない超高耐電圧スイッチングトランジスタの実現により、送配電系を中心として電力ネットワークにおける機械的スイッチや大容量トランスの半導体化による高信頼化、小型軽量化、そしてそれらのインテリジェント化を次世代スマートグリッド構築に生かすことにより、電力分野での省エネルギー化、高機能化が大きく進展すると期待される。

さらなるp型基板高品質化とデバイス作製プロセス技術の進展によって大面積、大電流の超高耐電圧SiC-IGBTを開発していくとともに、スイッチング電力損失低減を進めていく。また他機関、企業とも連携し、大容量電力変換に必要な大電流、高温対応パッケージング技術などの周辺技術開発を信頼性も含めて加速し、次世代スマートグリッドなどの基幹構成要素である10 kV超級の高機能低損失電力機器の実現を目指していく。