独立行政法人 産業技術総合研究所【理事長 中鉢 良治】(以下「産総研」という)ナノエレクトロニクス研究部門【研究部門長 金丸 正剛】シリコンナノデバイスグループ 森田 行則 主任研究員 兼連携研究体グリーン・ナノエレクトロニクスセンター 連携研究体付らは、新たな構造を採用した合成電界トンネルFETの動作を実証した。

トンネル電界効果トランジスタ(トンネルFET)は、電子のトンネル効果を利用したトランジスタで、原理的に電界効果トランジスタ (MOSFET)の限界を超えた低電圧でオン・オフの切り替えができるため、低消費電力化が期待されている。しかし、MOSFETに比べて流れる電流が小さく、実際に応用する際の課題となっていた。今回の新しい構造のトンネルFETでは、定められたゲート電圧でより強い電界をかけられるような、新たなチャネルと電極構造を用いており、従来のトンネルFETの10~100倍の動作電流が得られた。集積回路(LSI)の消費電力低減に寄与すると期待される。

なお、この技術の詳細は、2013年6月11~13日に京都府京都市で開催される国際会議「VLSI技術シンポジウム」(2013 Symposium on VLSI Technology)で発表される。

|

|

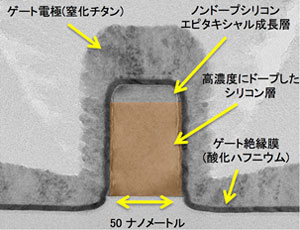

今回開発した新構造トンネルFET断面の透過電子顕微鏡像 |

携帯型情報端末や高性能パソコンなどの電子情報機器の普及や扱われる情報量の増加に伴い、エネルギー消費も増大している。電子情報機器の消費電力低減が社会的に求められているが、現在の電子回路を構成する電界効果トランジスタ (MOSFET)の低消費電力化は原理的な限界に近づいている。

この限界を突破するため、MOSFETとは異なる原理で動作する素子としてトンネルFETが注目されている。トンネルFETはMOSFETの限界を超えた低電圧でのオン・オフの切り替えが原理的に可能であるため、これを用いた電子回路の低消費電力化が期待されている。

連携研究体グリーン・ナノエレクトロニクスセンター(GNC)は、内閣府と独立行政法人 日本学術振興会によって運営される最先端研究開発支援プログラム(FIRST)に採択されたプロジェクトを実施するために平成22年4月に設立された。企業5社(富士通株式会社、株式会社 東芝、株式会社 日立製作所、ルネサスエレクトロニクス 株式会社、株式会社 アルバック)からの出向研究者と産総研研究者によって構成されている。GNCでは平成23年度より、従来のLSIの消費電力を10分の1~100分の1に低減することを目標に、トンネルFETおよび素子動作モデルの開発を進めている。この研究開発は、最先端研究開発支援プログラム(FIRST)のプロジェクト「グリーン・ナノエレクトロニクスのコア技術開発」(中心研究者:横山 直樹)の助成により行われた。

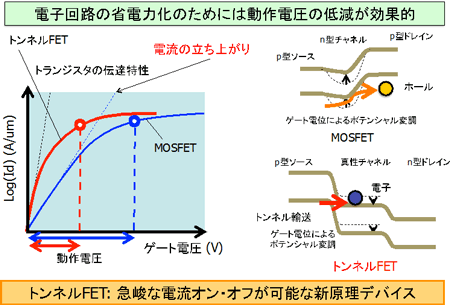

トンネルFETはゲート電極にゲート電圧をかけると、その電界の影響でソースとチャネルを隔てる障壁が薄くなり、トンネル効果により電子が障壁を通り抜けて、トランジスタに電流が流れる。この原理により、従来のMOSFETよりも低い電圧で電流のオン・オフが切り替えられる。すなわち、スイッチングが急峻のため、より低電圧でも動作する低消費電力の電子回路を構築できる (図1)。

|

|

図1 トンネルFETの動作原理と動作電圧低減 |

しかし、トンネルFETはトンネル効果を利用するため、MOSFETよりも流れる電流が小さいという課題がある。大きい電流を効率的に得るには、トンネル接合部により強い電界をかけることが重要である。強い電界をかけるためには大きなゲート電圧が必要であるが、消費電力低減にはより低い電圧での動作が必要とされる。そこで同じゲート電圧で、より強い電界が得られる新たなチャネルと電極の構造を用いることとした。

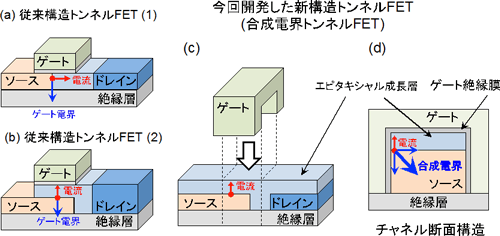

図2(c)と(d)は今回作製した新構造トンネルFETの模式図である。高濃度に不純物を注入したソース上に、極めて薄いノンドープチャネルをエピタキシャル成長させた後、加工して、2層構造のチャネル周囲にゲート電極を配置して立体構造のトランジスタとした。従来のトンネルFETでは、図2 (a)や(b)に示すように、ゲート電極からの電界に対し垂直(a)、または平行(b)な電界のみの効果によって電流をオン・オフする設計となっていた。それに対し今回開発した構造では、立体加工したチャネル側壁面の高濃度ソースとノンドープチャネル層の界面で、縦方向と横方向の電界を重ねることで、従来よりも強い電界をかけることができる。この新構造のトンネルFETを「合成電界トンネルFET (Synthetic electric field tunnel FET: SE-TFET)」と命名した。

|

|

図2 従来構造と新構造トンネルFETの比較 |

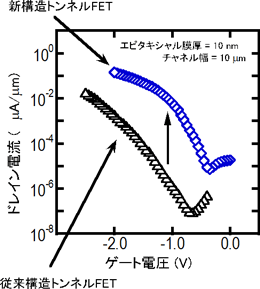

図3に従来のトンネルFETと今回開発した合成電界トンネルFETでの、ゲート電圧と得られるドレイン電流との関係を示す。合成電界トンネルFETでは従来のトンネルFETに比べて10~100倍のドレイン電流が得られた。エピタキシャル成長層の厚さやチャネルの幅を縮小すれば、トンネル接合部にさらに強い電界をかけられるため、デバイスの微細化による性能向上が可能である。さらに、今回の合成電界トンネルFETはシリコン(Si)を用いたが、Siを超える性能のデバイス材料であるゲルマニウムや、インジウムガリウムヒ素などの化合物半導体を用いたトンネルFETでも、今回の構造は効果を発揮できる。将来の微細化や材料の進化により、一層の性能向上が期待できる。

|

|

図3 従来構造と新構造トンネルFETのドレイン電流 |

引き続きプロセスの最適化を進め、低電圧でのCMOS動作を目指す。また、さらなる微細化により、既存のトンネルFETを大きく超える性能と一層の動作電圧低減を目指す。実験とシミュレーション、回路動作モデルとを組み合わせて、CMOS回路に適用した場合の電源電圧低減効果などについても明らかにしていく。