独立行政法人 産業技術総合研究所【理事長 中鉢 良治】(以下「産総研」という)ナノエレクトロニクス研究部門【研究部門長 金丸 正剛】連携研究体グリーン・ナノエレクトロニクスセンター【連携研究体長 横山 直樹】鎌田 善己 特定集中研究専門員らは、大規模集積回路の3次元積層技術に向けた多結晶ゲルマニウム(Ge)トランジスタが5桁を超えるオン・オフ比を示すことを実証した。

液晶ディスプレーなどで用いられている多結晶シリコン(Si)トランジスタに比べ、多結晶Geトランジスタは、より低温で形成することができる。さらに移動度が高いために、高性能化および低電圧動作が期待される。今回、トランジスタ構造を微細なフィン型トランジスタとすることで、実用レベルに迫る5桁を超えるオン・オフ比を実現した。スパッタリング成膜やシンプルな製造工程の採用による低コスト化の可能性がある。TSVやマイクロバンプなどを用いたチップ積層による3次元化技術を代替、あるいは補完する新たな3次元積層技術として期待される。

なお、この技術の詳細は、2013年6月11~13日に京都府京都市で開催される2013 VLSI Technology シンポジウムで発表される。

|

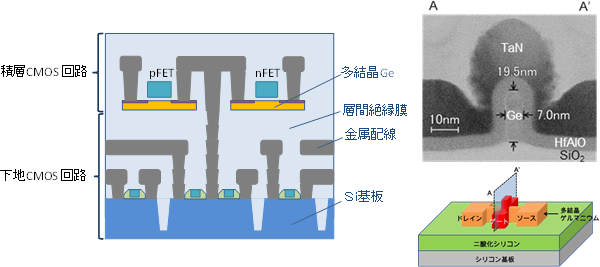

| 積層集積回路の概念図(左)と、試作した素子の断面構造(右) |

携帯情報端末の爆発的な普及や、IT機器の高機能化に伴う消費電力の増大に伴い、電子情報機器の消費電力低減が求められている。そのためには、電子情報機器に搭載されているLSIを構成する個々のトランジスタに供給する電圧(電源電圧)を低減することが重要である。従来、LSIの高性能化・低消費電力化はトランジスタの微細化によってもたらされてきた。しかし、近年、微細化の副作用であるオフリーク電流の増加や配線遅延の増大、電流駆動力の飽和に対処するために新たなプロセス技術の開発や設備導入が必要となり、次第に微細化が困難となってきている。一方、複数のLSIを積層し、上下のLSI間にTSVやマイクロバンプを導入するなど、3次元的な集積回路を形成する研究開発も進められている。微細化技術によらずに、チップ面積の縮小や高機能化、配線遅延の低減による省電力化などの効果が得られる。しかし、TSVやマイクロバンプは、現状では配線ピッチが必ずしも十分でなく、高コストであるといった問題点があるため、新たな3次元積層技術が求められている。これらの問題点を解決するためには、配線を含む集積回路を連続的に多層に形成できる技術(積層CMOS技術)が有望と考えられる。産総研は、多結晶Geが低温で絶縁膜上に形成可能であることに着目し、多結晶Geによる積層CMOSの開発を開始した。

連携研究体グリーン・ナノエレクトロニクスセンター(GNC)は、内閣府と独立行政法人 日本学術振興会によって運営される最先端研究開発支援プログラム(FIRST)に採択されたプロジェクトを実施するために平成22年4月に設立された。企業5社(富士通株式会社、株式会社 東芝、株式会社 日立製作所、ルネサスエレクトロニクス 株式会社、株式会社 アルバック)からの出向研究者と産総研研究者によって構成されている。GNCでは平成23年度より、LSIの低電圧動作を目指して、高移動度材料であるGeを用いたトランジスタの研究開発を行ってきた。平成24年度より、3次元積層技術と融合可能な多結晶Geトランジスタの開発に取り組んだ。

なお、今回ゲート長40 nmのトランジスタで良好なスイッチング特性が得られた。本研究成果は、FIRSTのプロジェクト「グリーン・ナノエレクトロニクスのコア技術開発」(中心研究者:横山 直樹)の助成により得られたものである。

Siトランジスタを積層する場合、下層のCMOS回路への熱影響の問題点がある。多結晶Geは、絶縁膜上に下層のCMOS回路に影響のない低温で形成できるため、順次CMOS回路を積層して、3次元積層集積回路を形成するためのデバイス材料に適している。

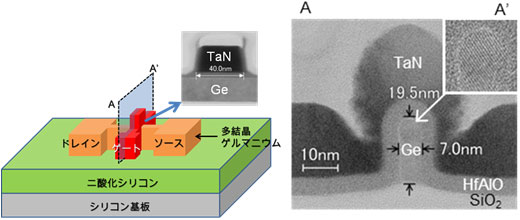

Si酸化膜上に非晶質Geをスパッタリング成膜した後、熱処理して多結晶Geを作成し、それを用いてフィン型トランジスタを試作した(図1)。通常のMOSFETと異なり、無接合トランジスタと呼ばれる構成とした。すなわち、チャネルとソースドレイン全体が同一濃度のp型であり、pn接合が存在しない。従って、通常のMOSFETで必要なソースドレイン形成工程を省略でき、低コストで形成できる特長がある。一方では十分な制御特性を得るためには、チャネルの幅を空乏層厚さ以下にする必要がある。そのため、透過電子顕微鏡像に示すように、フィン幅を7 nmまで縮小した。

|

| 図1 試作したGeトランジスタの概念図(左)と断面の透過電子顕微鏡像 (右) |

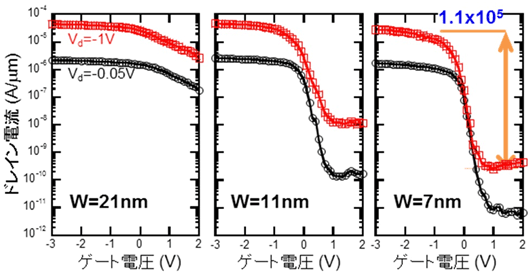

図2に、ゲート長が40 nmの多結晶Geトランジスタの制御特性(ドレイン電流-ゲート電圧特性)を示す。フィン幅が狭くなるにつれて制御特性が向上していることが分かる。フィン幅7 nmのトランジスタにおけるドレイン電流の最小値(0.3 nA/µm)は、単結晶Geのこれまでに報告されている最小値に迫る値である。この値は、低消費電力版のSiトランジスタで要求されるオフリーク電流値(5 nA/µm)を下回っており、実用化レベルの値といえる。また、ドレイン電圧1 Vで5桁を超えるオン・オフ比が得られている。このような短チャネルトランジスタで問題となるドレイン電圧の違いによるしきい値電圧変動も十分抑制されている。

|

図2 試作したゲート長40 nmのトランジスタの伝達特性(ドレイン電流-ゲート電圧特性)

Wはフィン幅を示す。 |

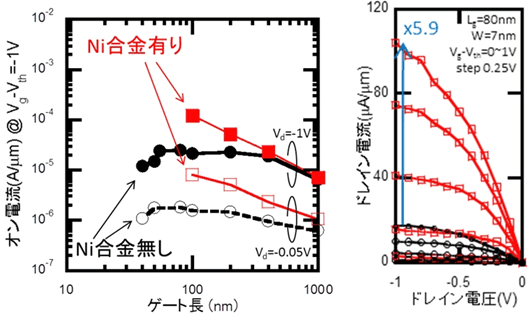

一方、このように狭いフィン構造を用いると、ソースドレイン部の電気抵抗が増え、電流値が十分には得られないという問題が生じる。この問題を回避するため、Si工程で用いられているサリサイドと同様な工程で、ソースドレインをニッケル(Ni)合金化することで、ソースドレイン部の抵抗を下げることができた。その結果を図3に示す。合金化の有無によるオン電流の差は、ゲート長が短くなり、ソースドレイン部の抵抗成分の寄与が顕著になるほど大きくなっていることが分かる。ゲート長80 nmのトランジスタにおいては、この工程により電流値が6倍近くに増大し、多結晶トランジスタとしては非常に高い100 µA/µmが1 V相当の電源電圧で得られた。これは、同じゲート長の単結晶Si-pMOSFET半分程度の電流駆動力に相当する。

|

| (a) |

(b) |

図3 オン電流のNi合金化の有無による違い。ゲート長依存性(a)と、ゲート長80 nmのトランジスタのドレイン電流-ドレイン電圧特性の比較(b)。

赤線が合金化ありの場合、黒線が合金化なしの場合。 |

今回作製した多結晶Geの移動度は、文献で報告されている多結晶Geに対する最大値の3分の1程度の値であるため、まだ改善の余地がある。今後、工程の改善により移動度を向上することができれば、結晶Siトランジスタと同等以上の性能の多結晶Geトランジスタを、低コストで層間膜上に積層していくことが可能になると期待される。

今回はp型トランジスタに関する動作検証であったが、今後はn型トランジスタについてもプロセスを確立し、CMOS回路動作を目指す。さらに、Geの高移動度特性を生かして、結晶Siトランジスタを超える性能を目指す。