独立行政法人 産業技術総合研究所【理事長 中鉢 良治】(以下「産総研」という)ナノエレクトロニクス研究部門【研究部門長 金丸 正剛】連携研究体グリーン・ナノエレクトロニクスセンター【連携研究体長 横山 直樹】入沢 寿史 特定集中研究専門員らは、住友化学株式会社【代表取締役社長 十倉 雅和】(以下、「住友化学」という)と共同で、大規模集積回路の消費電力低減に有効な、ゲルマニウム(Ge)p型MOSFET(pMOSFET)とインジウムガリウムヒ素(InGaAs)n型MOSFET(nMOFSET)によって構成されるCMOSインバーターを試作し、その動作を初めて実証した。

InGaAsなどのIII-V族化合物半導体のnMOSFETは、従来のLSIで用いられているシリコン(Si) n MOSFETに比べ、より低電圧で多くの電流を流すことができる。一方、GeのpMOSFETは、Si- pMOSFETに対し、より低電圧で多くの電流を流すことができる。これらを組み合わせたCMOS回路でLSIを構成すれば、Siでは実現不可能な、大幅な消費電力低減ができることは予測されていたが、これまで、このようなCMOS回路の動作は実現できていなかった。今回、Ge-pMOSFETと、InGaAs-nMOSFETを、絶縁膜を介して上下に積層してCMOSインバーターを試作し、その動作を確認した。GeとInGaAsの層を分けたため、それぞれの層の作製工程を個別に最適化することが容易となり、適切なしきい値電圧を保ちつつ移動度を最大化することができた。また、Ge-pMOSFETの直上にInGaAs-nMOSFETを形成するので、p型とn型のMOSFETを横に並べる一般的な方式に比べて回路面積を縮小できた。今回のCMOS回路動作実証により、超低消費電力LSIの実現への貢献が期待される。

なお、この技術の詳細は、2013年6月11~13日に京都府京都市で開催される2013 VLSI Technology シンポジウムで発表される。

|

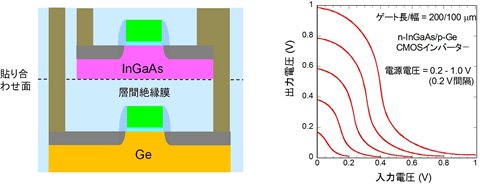

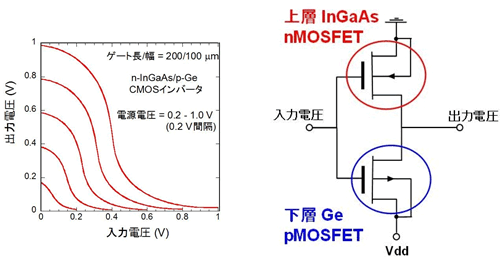

| 試作したGeとInGaAsを用いたCMOSインバーターの構成概念図(左)と伝達特性(右) |

携帯情報端末の爆発的な普及や、IT機器の高機能化に伴う消費電力の増大に伴い、電子情報機器の消費電力低減が求められている。そのためには、電子情報機器に搭載されているLSIを構成する個々のトランジスタに供給する電圧(電源電圧)を低減することが重要である。従来、トランジスタの微細化によって電源電圧を低減してきたが、近年、電源電圧1 V程度で低減のペースが鈍ってきている。これは、電源電圧を下げるとトランジスタ動作に必要な電流値が得られないとか、オフリーク電流を抑えきれないといった、現在の主流であるSiのMOSFETの本質的な問題に起因している。そこで、Siより電子や正孔の移動度が高い新材料を導入してLSIの消費電力を低減することが求められるようになり、研究開発が活発化している。

連携研究体グリーン・ナノエレクトロニクスセンター(GNC)は、内閣府と独立行政法人 日本学術振興会によって運営される最先端研究開発支援プログラム(FIRST)に採択されたプロジェクトを実施するために平成22年4月に設立された。企業5社(富士通株式会社、株式会社 東芝、株式会社 日立製作所、ルネサスエレクトロニクス 株式会社、株式会社 アルバック)からの出向研究者と産総研研究者によって構成されている。GNCでは設立以来、LSIの低電圧動作を目指して、高移動度材料であるGeやInGaAs を用いたMOFSETの高性能化に関する研究開発を行ってきた。今回、これらの成果を融合することによって、Ge/InGaAs CMOS動作の世界初実証に成功した。

なお、本研究成果は、FIRSTのプロジェクト「グリーン・ナノエレクトロニクスのコア技術開発」(中心研究者:横山 直樹)の助成により得られたものである。また、InGaAsエピタキシャル層の開発、作製は住友化学との共同研究により行った。

pMOSFETには、正孔移動度が高いGeが、nMOSFETには、電子移動度が高いInGaAsなどのIII-V族化合物半導体が適している。これらの個別のトランジスタの性能向上に関して多数の報告例があり、同一基板上に異なるチャネルを形成した例もある。しかし、これらの異なるMOSFETを用いたデュアルチャネルCMOS回路の動作例は報告されていない。

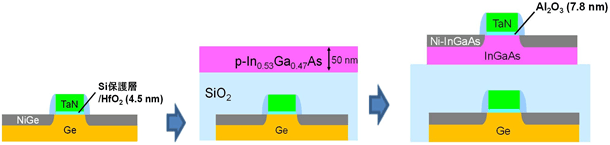

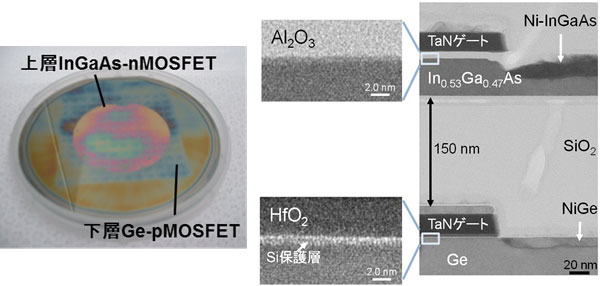

図1に、今回試作したGeとInGaAsを用いたデュアルチャネルCMOSインバーター(Ge/InGaAs-CMOSインバーター)の作製法を示す。まず、Ge基板上にpMOSFETを作製し、その上部に層間絶縁膜を形成して、これを研磨して平坦にする。次に、リン化インジウム(InP)基板上にエピタキシャル成長させたInGaAs薄膜の表面側を、層間絶縁膜表面に室温で貼り合わせる。InP基板を酸で溶解して除去することにより、Ge-pMOSFET上にInGaAs薄膜が形成される。このInGaAs薄膜上にnMOSFETを構成した後、上下のMOSFETを接続する配線工程によりインバーター回路を構成した。回路を試作した基板の外観と、断面図を図2に示す。上下のMOSFETは30 nm程度の良好な精度で位置合わせができていた。なお、p型とn型のMOSFETを積層することによって、回路面積の大幅な縮小も期待できる。

|

| pMOSFET作製 |

InGaAs薄膜貼り合わせ |

nMOSFET作製 |

| 図1 今回開発したGe/InGaAs-CMOSインバーターの作製法 |

|

| (a) |

(b) |

| 図2 CMOSを試作した基板(4インチGe基板と2インチのInGaAs薄膜の貼り合わせ)の外観(a)と、MOSFET積層部の断面構造の透過電子顕微鏡像(b)

|

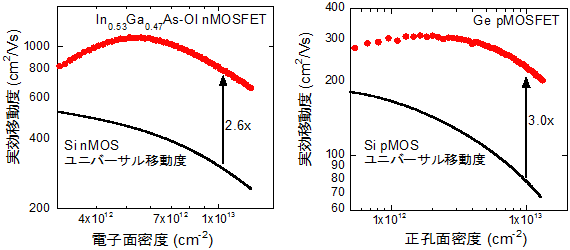

図3に、上層のInGaAs-nMOSFETの電子移動度と下層のGe-pMOSFETの正孔移動度を示す。いずれも、MOSFET単独で作製した場合と同等の高い移動度が得られた。また、各MOSFETの電流電圧特性にも積層による特段の劣化はみられない。これは、InGaAsを積層する際に、問題となるような大きな力が加わっていない事や、上部nMOSFET形成時の最高温度を350 ℃という低温に抑えられた事によると考えられる。

|

| 図3 InGaAs-nMOSFETの電子移動度(左)およびGe-pMOSFETの正孔移動度(右) |

回路を正常に動作させるには、上下のMOSFETのしきい値電圧を適切に設定することが重要である。従来の同一平面内に異なる材料からなるp型とn型のMOSFETを並べる方式では、通常、それぞれのしきい値電圧を個別に調整するために複雑な工程が必要となる。一方、今回開発した積層構造では、上層、下層のMOSFETごとに順次最適な工程を施すことで、p型、n型の各MOSFETの移動度を最大化できる

ゲートスタック構造を用いつつ、それぞれのしきい値電圧を適切に設定することができた。図4に、作製したGe/InGaAs-CMOSインバーターの伝達特性を示す。電源電圧1 Vの場合はもとより、0.2 Vという低電圧でも動作する。これは、積層工程を経ても、インバーターを構成する各p型とn型のMOSFETそれぞれのしきい値電圧が、適切に設定されていることを示している。

|

| 図4 作製したGe/InGaAsデュアルチャネルCMOSインバーターの入出力特性(左)と、その構成を示す回路図(右) |

このように、Ge-pMOSFET上にInGaAs-nMOSFETを積層する工程によって、GeとIII-V族化合物半導体で構成されるデュアルチャネルCMOSインバーター回路を作製し、その動作を実証した。積層に伴う各MOSFETの特性劣化やしきい値電圧変動もなく、積層によって回路面積が縮小できるので、デュアルチャネルCMOSの基本構成として有望である。

今後は、より実用的なサイズのトランジスタ(短チャネルMOSFET)を用いた回路での動作実証と、動作速度に関するメリットの検証を行っていきたい。