独立行政法人 産業技術総合研究所【理事長 野間口 有】(以下「産総研」という)ナノエレクトロニクス研究部門【研究部門長 金丸 正剛】連携研究体グリーン・ナノエレクトロニクスセンター【連携研究体長 横山 直樹】福田 浩一 研究員らは、トンネル電界効果トランジスタ(トンネルFET)の回路動作を予測する回路シミュレーションのための素子動作モデルを開発した。

この素子動作モデルはトンネルFET内部の電界分布を予測し、トンネル電流を見積もることで、電流電圧特性をシミュレーションする。このモデルはVerilog-A言語で記述できるので既存の主要回路シミュレーターに組み込むことが可能である。超低消費電力回路の実現を目指しているトンネルFETの回路設計への貢献が期待される。

この技術の詳細は、2012年9月25~27日に京都市で開催される2012年国際固体素子・材料コンファレンス(SSDM 2012)で発表される。

|

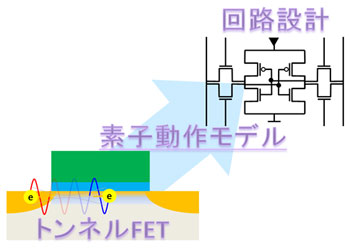

低電圧動作トンネルFETを用いた大規模集積回路 (LSI) 回路設計までの流れ

開発した素子の特性を、本素子動作モデルで表現し、回路設計を行うことができる。 |

近年、携帯情報端末の普及やIT機器の高機能化に伴う消費電力の増大が懸念され、電子情報機器の消費電力低減に関する社会的要求が高まっている。しかし、従来の金属-酸化物-半導体で構成される電界効果トランジスタ (MOSFET)による低消費電力化は限界に近づいており、低炭素社会の実現にはこれまでの壁を破る画期的な消費電力LSIが必要とされている。

最近、LSIの超低消費電力化を実現するために、これまでのMOSFETにかわる素子として、低電圧で急峻なオン・オフの切り替えができるトンネルFETが注目され、これを用いたLSI回路の低消費電力化が期待されている。LSI回路の設計には、設計した回路が性能を満たすかどうかをあらかじめ検証するためのシミュレーションが欠かせないが、トンネルFETではトンネル効果を取り入れた電流電圧特性の予測が難しいといった問題があり、回路シミュレーションに必要な素子動作モデルは存在しなかった。

産総研 ナノエレクトロニクス研究部門 連携研究体グリーン・ナノエレクトロニクスセンター(GNC)は、2010年4月に設立され、メンバーは産総研研究者と企業5社(富士通株式会社、株式会社 東芝、株式会社 日立製作所、ルネサスエレクトロニクス 株式会社、株式会社 アルバック)からの出向研究者によって構成されている。GNCでは2011年度より、従来のLSIの消費電力を10分の1~100分の1に低減することを目標に、トンネルFETの開発を進めている。さらに、LSIの回路シミュレーションに必要なトンネルFETの素子動作モデルの開発にも取り組んできた。

なお、この研究開発は、総合科学技術会議により制度設計された、独立行政法人 日本学術振興会の最先端研究開発支援プログラム(FIRST)の助成を受けて行われた。

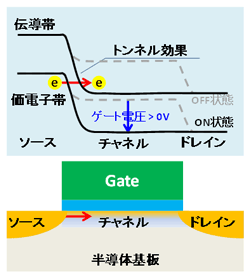

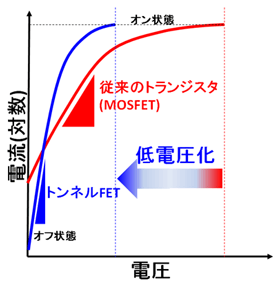

トンネルFETは、従来のLSIで用いられてきたMOSFETと異なり、ゲート電圧によりトンネル現象を引き起こすことでオン・オフを制御するトランジスタである。図1にトンネルFETの概念図を示す。ゲート電圧を制御してチャネルの価電子帯や伝導帯のエネルギーレベルを急激に変化させる。これによってソースの価電子帯とチャネルの伝導帯のエネルギーレベルが近づくとソースとチャネルの間にトンネル現象が生じて、トランジスタに電流が流れる。この原理によるトンネルFETでは、従来のMOSFETよりも少ない電圧で電流のオン・オフが切り替わり、急峻なスイッチングができる。図2に示すように、スイッチングが急峻であれば、従来のMOSFETよりも低電圧での動作ができるようになる。この結果、トンネルFETを用いたLSI回路は、従来のMOSFETを用いたLSI回路よりも低電圧で動作できるようになる。

|

図1 トンネルFETの構造と動作原理

灰色はオフ状態を示す |

|

|

図2 トンネルFETの急峻なスイッチング特性 |

今回開発したトンネルFETの素子動作モデルは、トンネルFETで生じるトンネル電流をソース、ドレイン、ゲートの各端子電圧から予測できる。このモデルは、まずトンネルFET素子内部でトンネル電流が発生する箇所の電界分布を予測する。その電界分布からトンネル距離を求められるので、トンネル電流の発生量を見積もることができる。本モデルが個々の素子の電気特性を予測可能とするため、本モデルを用いた回路シミュレーターは多数の素子を接続した回路の性能を高速に予測できる。これによりトンネルFETを用いたLSIの回路設計が可能となる。また、このモデルはVerilog-A言語で記述できるので、さまざまな回路シミュレーターに組み込んでシミュレーションすることができる。

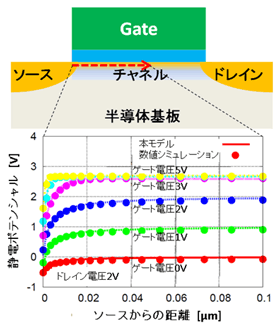

回路シミュレーションにおいては同時に多数の素子を扱うため、このモデルは瞬時に計算可能な解析式で表されている。このモデルの妥当性は素子構造を小領域の集まりに分割して方程式を解く数値解析手法(有限要素法)などの数値シミュレーションと比較して検証した。図3に開発した素子動作モデルで予測した静電ポテンシャル分布と、数値シミュレーションによる計算結果の、各端子電圧での比較を示す。トンネルFETの断面構造に対し、ゲート誘電膜に沿った分布を示している。このモデルで予測した静電ポテンシャル分布は、ひとつの素子で10分~1時間の計算時間が必要な数値シミュレーションと比較してもよく一致しており、これを使ってトンネル距離を得ることができ、正確なトンネル電流量を高速に求めることができる。

|

図3 素子動作モデルの静電ポテンシャル分布の予測と、数値シミュレーション結果の比較

各ゲート電圧(Vgs)における矢印に沿った界面の静電ポテンシャル分布 |

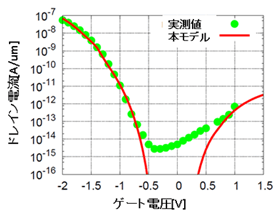

図4に、今回開発した素子動作モデルによって得られたトンネルFETの電流電圧特性と、実測値との比較を示す。ここではゲート電圧が負でオン状態になるトンネルFETについて比較した。このモデルによって精度よくトンネルFETの動作特性をシミュレーションできることがわかる。このモデルを回路シミュレーターに組み込むことで、トンネルFETを用いたLSI回路のシミュレーションができ、LSI回路の設計や、さらには低消費電力化への貢献が期待される。

|

|

図4 トンネルFETの電流電圧特性のシミュレーション結果と実測値との比較

注) ゲート電圧0 V付近の差異は、実測で見られたゲート誘電膜を介したリーク電流によるもので、トンネルFET本来の特性ではなく、素子設計で抑制できるため、この計算では無視した。 |

今回開発した素子動作モデルとして低消費電力回路を研究者に提供することにより、トンネルFETを用いた低消費電力LSI回路の実現を加速させる。