独立行政法人 産業技術総合研究所【理事長 野間口 有】(以下「産総研」という)ナノエレクトロニクス研究部門【研究部門長 金丸 正剛】連携研究体グリーン・ナノエレクトロニクスセンター【連携研究体長 横山 直樹】池田 圭司 特定集中研究専門員らは、集積回路(LSI)の消費電力低減に有効な、高性能ひずみゲルマニウム(Ge)ナノワイヤトランジスタを開発した。

このトランジスタは、非常に大きな圧縮ひずみをもつGeナノワイヤを電流の通り道として用い、電流の出入り口である電極は、ニッケル(Ni)とGeの合金を用いたメタルソースドレインとなっている。圧縮ひずみの効果で、Geナノワイヤトランジスタの正孔移動度が、従来のシリコン(Si)トランジスタの8倍程度に増大し、さらに、Ni合金とGeとの接触抵抗を十分下げることができた。その結果、Geナノワイヤトランジスタとして世界最高レベルの高い電流駆動力が得られた。このトランジスタは不純物ドーピングを行わないプロセスで作製されるため、不純物に起因する特性ばらつきの抑制も期待される。これらの相乗効果により、今回試作したGeナノワイヤトランジスタは低電圧動作が可能となり、LSIの大幅な消費電力低減に寄与すると期待される。

なお、この技術の詳細は、2012年6月12~14日に米国ホノルルで開催される2012 VLSI Technologyシンポジウムで発表される。

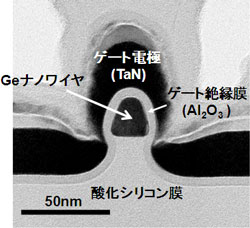

|

| 試作したGeナノワイヤトランジスタ断面の透過電子顕微鏡像 |

近年、電子情報機器の消費電力低減に関する社会的要求が高まっている。特に、携帯情報端末の爆発的な普及や、IT機器の高機能化に伴う消費電力の増大が懸念されている。LSIの消費電力低減の試みは、このような社会的要求に後押しされ急速な進展を見せている。これまでに大きな効果をあげているのは回路構成の改良によるものが主であった。しかし、LSIの消費電力低減のための、より本質的でかつ波及効果の高い解決策は回路を構成する個々のトランジスタに供給する電圧(電源電圧)を低減することと考えられる。そのために、従来はトランジスタの微細化によって電源電圧を低減してきたが、近年においては電源電圧1 V程度で低減のペースが鈍ってきている。これは、電源電圧を下げるとトランジスタの動作に必要な電流値が得られない、あるいは、オフリーク電流を抑えきれないといった本質的な問題に起因している。現在の主流である、Siを用いた平面型のチャネル構造を用いる限り改善は困難である。そこで、立体的なチャネル構成の導入や、Siより電子・正孔の移動度の高いGeなどの導入といった研究開発が活発化している。両者の特徴を融合した高移動度立体チャネルトランジスタの開発例もあるが、これまで十分な性能は得られていなかった。

連携研究体グリーン・ナノエレクトロニクスセンター(GNC)は、内閣府と独立行政法人 日本学術振興会によって運営される最先端研究開発支援プログラム(FIRST)に採択されたプロジェクトを実施するために平成22年4月に設立された。企業5社(富士通株式会社、株式会社 東芝、株式会社 日立製作所、ルネサスエレクトロニクス 株式会社、株式会社 アルバック)からの出向研究者と産総研研究者によって構成されている。GNCでは平成23年度より、LSIの低電圧動作を目指して、Ge立体チャネル構造トランジスタの高性能化に関する研究開発を行ってきた。本研究成果は、FIRSTのプロジェクト「グリーン・ナノエレクトロニクスのコア技術開発」の助成により得られたものである。なお、Geナノワイヤの格子ひずみの計測は、学校法人 明治大学 理工学部 電気電子生命学科 小椋 厚志 教授らとの共同研究により行った。

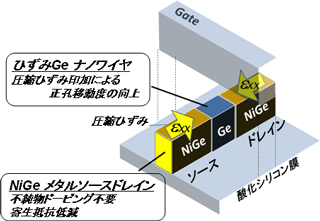

今回試作したトランジスタは、図1に示す2つの特徴的な要素技術により実現した。極めて大きな圧縮ひずみをもつGeナノワイヤの形成技術と、不純物をドーピングせずに電極と半導体との電気的接触を得る技術(メタルソースドレイン)である。

|

| 図1 ひずみGeナノワイヤトランジスタの構成と、主たる要素技術 |

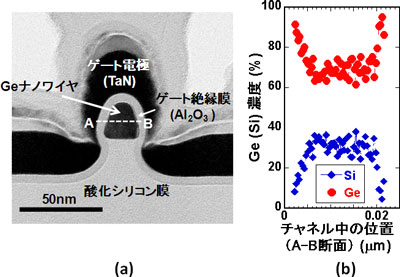

大きな圧縮ひずみをもつGeナノワイヤは、酸化濃縮法と反応性イオンエッチングによる細線加工を組み合わせることにより形成した。酸化濃縮プロセスの酸化時間や酸化温度を最適化して、図2に示すような幅20 nm程度のGeナノワイヤチャネルに大きな圧縮ひずみを導入することができた。

|

| 図2 試作したGeナノワイヤトランジスタ断面の透過電子顕微鏡像(a)と、チャネル断面のGe濃度プロファイル(b)

|

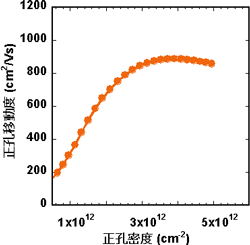

一般に、ひずみが加わると格子欠陥の発生が懸念されるが、今回試作したトランジスタでは、格子欠陥は発生していなかった。現在実用化されている最先端のSiトランジスタには、ひずみ技術が適用されているものもあるが、ひずみは1 %~2 %である。これらに比べ、今回得られたひずみは3.8 %と極めて大きく、上記の独自手法により初めて可能となったものである。この大きなひずみによる効果で、Siトランジスタの約8倍、ひずみSiトランジスタと比べても約4倍の正孔移動度が得られた(図3)。

|

| 図3 試作したGeナノワイヤトランジスタの正孔移動度 |

通常、ゲート電極下部の電流経路部分やソースドレイン部、その近くには高濃度の不純物がドーピングされる。平面型のトランジスタに正常なスイッチング動作をさせるためである。しかし、チャネル中の不純物原子の密度や位置のばらつきによって、トランジスタ特性のばらつきが生じることが知られている。回路中のトランジスタに1つでも特性の悪いものが混じると、回路全体の性能が悪化するため、特性ばらつきは極力抑える必要がある。今回、ばらつき低減のために、不純物ドーピングを行わない製造方法を開発した。通常、不純物濃度が低い半導体と金属との接触抵抗は非常に大きく、実用に堪えないが、今回、ひずみGeと、NiGe合金の接合では接触抵抗が十分低くなり実用的な接触抵抗値が得られることを見いだした。p型Geと金属の接触抵抗が比較的低いことは知られていたが、今回得られた接触抵抗値は、ひずみの無いGeとNiGe合金の接触抵抗より一桁程度低かった。これは、Ge中のひずみの効果による電気的特性の変化によるものと考えられる。

実際には、ゲート電極を形成した後、不純物をドーピングしていないGeナノワイヤにNiを堆積し、熱処理によって電流の出入り口であるソースドレイン部のGeとNiを反応させ、NiGe合金を生成させてソースドレインとした。イオン注入やそれに付随するプロセスが省けるためコストも抑えられる。

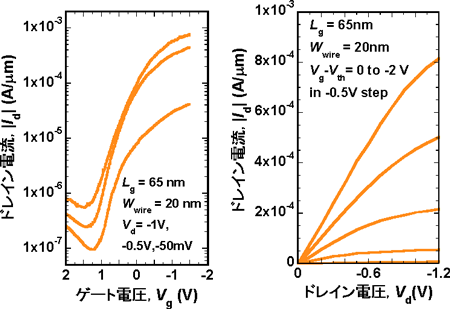

これらの2つの技術によってゲート長65 nmのp型Geナノワイヤトランジスタを試作した。図4に示すように800 µA/µm近い電流駆動力が得られた。これは、Geナノワイヤトランジスタとしては世界最高レベルの値である。

|

| 図4 試作したゲート長65 nmのひずみGeナノワイヤトランジスタの電流電圧特性 |

デバイス構造、プロセスの最適化を進め、最先端のSiトランジスタのスペックを大幅に上回る電流駆動力を目指す。さらに今後は実験とシミュレーションを組み合わせて、CMOS回路に適用した場合の電源電圧低減効果などについて明らかにしていく。