独立行政法人 産業技術総合研究所【理事長 野間口 有】(以下「産総研」という)ナノエレクトロニクス研究部門【研究部門長 金丸 正剛】強誘電体メモリグループ 酒井 滋樹 研究グループ長らは、国立大学法人 東京大学(以下「東大」という)大学院 工学系研究科 竹内 健 准教授と共同で、強誘電体ゲート電界効果トランジスタ(FeFET)をメモリーセルとして用いる強誘電体NANDフラッシュメモリー(Fe-NANDフラッシュメモリー)の64キロビット(kb)メモリーアレイを開発した。

今回、FeFETの集積化技術の開発により初めて全ビット測定が可能な64kb Fe-NANDフラッシュメモリーアレイの作製に成功し、かつ、2日間の測定によりブロックレベル(2kb)で良好なデータ保持特性を実証した。Fe-NANDフラッシュメモリーは、従来型のNANDフラッシュメモリーと同等以上の高集積性を持ちながら、消費電力は約7分の1、書き換え可能回数は約1万倍になると見込まれるため、高密度大容量、高書き換え耐性、低消費電力の次世代半導体不揮発メモリーとして期待される。

なお、この技術の詳細は、最先端のデバイス技術が報告される “2011 International Conference on Solid State Devices and Materials”(SSDM 2011)(2011年9月28日~30日、名古屋) で発表される。

|

|

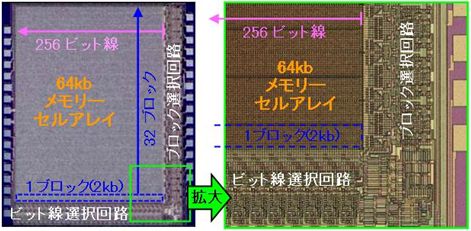

チップの全体写真(左)とチップの右下隅を拡大した光学顕微鏡写真(右) |

パソコンやサーバーのハードディスクドライブ(HDD)に代わる大容量データ記憶装置として、より小型軽量で低消費電力のソリッドステートドライブ(SSD)が注目されている。特にデータセンターでは、近年情報処理量の急増に伴う消費電力の増大と発熱が大きな問題となっており、サーバーへのSSD導入の期待は大きい。しかしSSDの基本部品である半導体不揮発メモリーのNANDフラッシュメモリーは、書き換え可能回数が約1万回と少なく、情報処理量の多いデータセンターのサーバーに用いるには書き換え可能回数がより多いことが望ましい。また、集積度を高めるために今後もNANDフラッシュメモリーセルの寸法を縮小し続ければ、書き換え可能回数はさらに減少してデータの信頼性に不安が生じるといわれている。このため、書き換え耐性がより高く、かつ、メモリーセルの寸法縮小も可能な、次世代半導体不揮発メモリーの開発が必要とされている。

産総研では、不揮発メモリーにもなるトランジスタとしてFeFETの研究を進めてきた。2002年にPt/SrBi2Ta2O9/Hf-Al-O/Siの積層ゲート構造を用いてFeFETのデータ保持時間を長くすることに初めて成功し(2002年10月24日産総研プレス発表)、2004年には自己整合ゲート技術を用いてFeFETの寸法縮小が可能であることを実証した(2004年12月15日産総研プレス発表)。2008年には東大の竹内 准教授とともにFeFETをメモリーセルとするFe-NANDフラッシュメモリーの開発に着手し、FeFETが従来比で書き換え可能回数が約1万倍、書き込み電圧が約3分の1の寸法縮小可能な高性能NANDフラッシュメモリーセルになることを実証した(2008年5月19日産総研プレス発表)。今回、FeFETの集積化技術により初めて全ビット測定が可能な64kb Fe-NANDフラッシュメモリーアレイの作製に成功し、かつ、2日間の測定によりブロックレベル(2kb)で良好なデータ保持特性を実証した。

なお、本研究は、独立行政法人 新エネルギー・産業技術総合開発機構(NEDO)の「省エネルギー革新技術開発事業/強誘電体フラッシュメモリ基盤技術の研究開発(平成21~23年度)」により実施した。

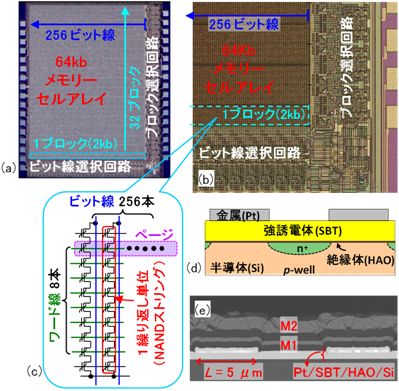

図1に今回作製した64kb Fe-NANDフラッシュメモリーアレイを示す。Fe-NANDフラッシュメモリーアレイ回路として働くように設計したSi半導体基板の上に大面積パルスレーザー蒸着法によって高誘電体Hf-Al-O薄膜を約7ナノメートル(nm)、強誘電体SrBi2Ta2O9(SBT)薄膜を約500nm製膜した後、Ptを約220nm製膜した。フォトリソグラフィーによりゲート電極とコンタクトホールを形成し、層間絶縁膜を挟んだ2層の金属配線層(M1、M2)を用いて回路を構成した。メモリーセルはPt/SBT/Hf-Al-O/Siの金属-強誘電体-絶縁体-半導体ゲート積層構造を持つnチャネル型のFeFETで、ゲート長(L)およびゲート幅(W)はともに5マイクロメートル(µm)である。これを縦256×横256の64k個集積してメモリーセルアレイを構成した。64kbメモリーセルアレイの2辺に接続したブロック選択回路とビット線選択回路も、nチャネル型およびpチャネル型のFeFETによるCMOS型回路でできている。選択回路を含めると合計で84k個のFeFETからなる。ブロック選択回路により32ブロックのうちの1ブロックを、ビット線選択回路により256本のビット線のうち隣接する2本を、それぞれ選択することができる。今回試作したテストチップでは、ワード線電圧とビット線電圧は外部パッドから与えた。読み出しはビット線電流を直接測定して行った。パルス発生機器、直流電流・電圧源、半導体パラメータアナライザなどを組み合わせて測定系を構築し、パソコンで制御することで自動計測した。

|

図1 今回作製した64kb Fe-NANDフラッシュメモリーアレイ

(a)チップの全体写真(b)チップの右下隅を拡大した光学顕微鏡写真

(c)1ブロック内の回路の概略図(d)メモリーセルアレイ断面の概略図

(e)メモリーセルアレイ断面の走査型電子顕微鏡写真 |

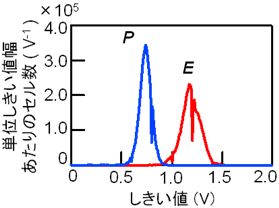

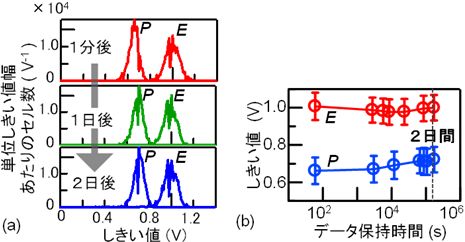

この64kb Fe-NANDフラッシュメモリーアレイを用いて、ブロック消去、ページ書き込み、データ非破壊読み出しを行った。64kbの全てのメモリーセルにアクセスできることを確認した。全ビット消去と全ビット書き込み、市松模様状書き込みの3通りのパターンを書き込み、これらの読み出しに成功した。64kbの全ビット消去後、および、全ビット書き込み後に読み出しを行った結果を図2に示す。また、ブロックレベル(2kb)で2日間の測定による良好なデータ保持特性(図3)のほか、セルレベルでは1億回書き換え可能であることも確認した。

なお、64kbの測定結果は29.6%の不良ビットを除き、2kbの測定結果は19%の不良ビットを除いてある。ブロックもしくはビット線を共有していたことによる選択回路の作製プロセスの不具合が不良ビット発生の原因と考えられる。

|

図2 64kb Fe-NANDフラッシュメモリーアレイの全ビット測定によるしきい値分布

E :ブロック消去後、P :全ビット書き込み後 |

|

|

|

図3 ある1ブロックにおける1分後、1日後、2日後の

しきい値分布(a)と2日間の測定によるデータ保持特性(b)

E :ブロック消去後、P :全ビット書き込み後 |

将来的には、Fe-NANDフラッシュメモリーのデータ書き込み時のビット線電圧は1 V、ワード線電圧は6 Vまで下げることができ、従来型NANDフラッシュメモリーと比べて消費電力は約7分の1になると見込まれる。

Fe-NANDフラッシュメモリーセルの微細化を進め、シリコンデバイスにおける目安のサイズの一つであるゲート長0.18µmを達成し、その後、さらに小さいゲート長0.05µmでFe-NANDフラッシュメモリーの実用化を数年以内に目指す。低消費電力で1億回の書き換え可能回数を持つ特性を生かし、データセンター向けSSDを最初の実用化のターゲットとしたい。