高い移動度を有するIII-V族化合物半導体とゲルマニウム (Ge) をチャネルに採用した次世代高性能III-V/Ge CMOSトランジスタを世界で初めて実現しました。従来のシリコン (Si) トランジスタでは性能向上に限界があり、200%以上の性能向上は困難でしたが、今回のIII-V/Ge CMOSトランジスタの実現により、従来の200%の限界を超越した次世代高性能III-V/Ge CMOSトランジスタの実用化が期待されます。

国立大学法人 東京大学 【総長 濱田 純一】 (以下、「東京大学」という)、独立行政法人 産業技術総合研究所 【理事長 野間口 有】 (以下、「産総研」という)、住友化学株式会社 【代表取締役社長 十倉 雅和】 (以下、「住友化学」という)、独立行政法人 物質・材料研究機構 【理事長 潮田 資勝】 (以下、「物材機構」という) は、シリコンプラットフォーム上III-V族半導体チャネルトランジスタ技術の開発に関する共同研究を行っています。

今回、東京大学の基板作製技術とデバイス作製技術、産総研のプロセス開発技術、住友化学の結晶成長技術というそれぞれの強みを生かし、次世代高性能III-V/Ge CMOSトランジスタの実用化に向けた基本技術となる、(1) III-VチャネルのGe基板上への集積化技術とIII-V/Ge CMOSトランジスタの自己整合型同時作製技術、(2) 極薄チャネル III-V-OI MOSFETの高性能化技術、(3) III-V/Ge CMOSプロセスの簡略化技術、の開発に成功しました。

これらの成果の詳細は、最先端のデバイス技術が報告される "2011 Symposia on VLSI Technolog" (VLSI symposia 2011) (2011年6月13日~16日、京都) において、3件の論文として発表します。

本研究は、平成19年度から開始された 独立行政法人 新エネルギー・産業技術総合開発機構 (NEDO) プロジェクト「ナノエレクトロニクス半導体新材料・新構造ナノ電子デバイス技術開発」 (シリコンプラットフォーム上III-V族半導体チャネルトランジスタ技術の研究開発) の委託により行われています。

■ ポイント ■

従来のシリコントランジスタでは性能向上に限界があり、200%以上の性能向上は困難でした。今回、III-V/Ge CMOSの開発を実現することで、その限界を突破することが可能になります。そして、今回開発した基本技術を応用することで、高い電子移動度を有するIII-V nMOSFETと高い正孔移動度を有するGe pMOSFETを集積した、次世代高性能III-V/Ge CMOSトランジスタの実用化が期待されます。

ポイント1: 世界初の次世代高性能 III-V/Ge CMOSトランジスタの実現

-

次世代高性能III-V/Ge CMOSトランジスタを世界で初めて実現しました。基板貼り合わせ技術を利用して、インジウムガリウムヒ素 (InGaAs) チャネルをGe基板上に集積することで、高い電子移動度を有するIII-Vチャネルと高い正孔移動度を有するGeチャネルを有するIII-V-OI-on-Ge (InGaAs-OI-on-Ge) 基板の作製に世界で初めて成功しました。さらに、ニッケル (Ni) とIII-VチャネルあるいはGeチャネルとの合金化反応を利用して、III-V nMOSFETとGe pMOSFETのメタルS/D接合を有する同時作製可能な自己整合型プロセスを開発し、III-V nMOSFETとGe pMOSFETの同一基板上への集積を実現したIII-V/Ge CMOSトランジスタの開発に世界で初めて成功しました。これにより、次世代高性能III-V/Ge CMOSトランジスタの実用化が期待されます。

ポイント2: 高電子移動度極薄チャネル III-V-OI nMOSFETの高性能化

-

次世代高性能III-V/Ge CMOSトランジスタに集積可能な膜厚10 nm以下の極薄チャネルIII-V MOSFETの高性能化に向けて、InGaAsコンポジットチャネルを有する極薄チャネルInGaAs-OI nMOSFETを開発し、Si MOSFETの4倍以上の高い電子移動度を実現しました。高電子移動度を保持したまま、極薄チャネル III-V-OI nMOSFETのスケーリングを実現することが期待されます。

ポイント3: メタル S/Dとメタルゲートを共通化した微細III-V/Ge CMOSプロセス技術の開発

-

次世代高性能III-V/Ge CMOSトランジスタの作製に向けて、共通メタルを用いたメタルS/Dとメタルゲート形成技術を開発し、III-V/Ge CMOSプロセスの大幅な簡略化と、ゲート長100 nm 以下の微細 III-V/Ge CMOSトランジスタの動作実証に成功しました。

研究成果1: 次世代高性能 III-V/Ge CMOSトランジスタを世界で初めて実現

~III-VチャネルとGeチャネルを同一基板上へ集積する技術の開発、およびNi合金をベースとした自己整合型プロセスによるIII-V/Ge メタルS/D CMOSトランジスタの同時作製技術の開発~

次世代高性能III-V/Ge CMOSトランジスタの実現を可能にする、高い電子移動度を有するInGaAsチャネルと高い正孔移動度を有するGeチャネルを同一基板上に集積したInGaAs-OI-on-Ge基板を世界で初めて開発しました。さらに、Ni合金をベースとした自己整合型プロセスによるIII-V/Ge メタルS/D CMOSトランジスタの同時作製技術を開発しました。これらにより、III-V nMOSFETとGe pMOSFETを同一基板上に作製したIII-V/Ge CMOSトランジスタを世界で初めて実現し、高移動度材料を集積することによりSiトランジスタを超える性能を有するIII-V/Ge CMOSトランジスタが実現可能であることを世界で初めて実証しました。

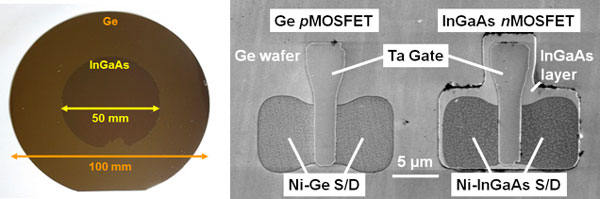

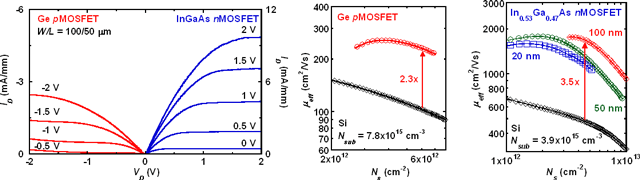

今回、基板貼り合わせ技術を用いることで、埋め込み酸化膜 (BOX) 層にAl2O3を材料として用いたInGaAs-OI-on-Ge基板の開発に世界で初めて成功しました (図1-1)。さらに、Ni とIII-VチャネルあるいはGeチャネルとの合金化反応を利用して、III-V nMOSFETとGe pMOSFETのS/D接合を同時に自己整合型で形成できるプロセスを開発しました (図1-1)。同一基板上に同時に作製したIII-V nMOSFETとGe pMOSFET の動作実証に世界で初めて成功し (図1-2)、III-V/GeメタルS/D CMOSトランジスタの開発に世界で初めて成功しました。InGaAs-OI-on-Ge基板を用いることで、同一基板上に作製されたIII-V nMOSFETおよびGe pMOSFETにおいて、それぞれ高い電子移動度 約1800 cm2/Vs と高い正孔移動度 約260 cm2/Vs を実現しました。ここで、InGaAs nMOSFETおよびGe pMOSFET は、それぞれ、Si n/pMOSFETに比べて、最大で約3.5倍および約2.3倍の性能向上を実現しています (図1-2)。

|

|

図1-1 III-V-OI-on-Ge基板の写真 (左図)。自己整合型プロセスにより、同一基板上に作製されたInGaAs nMOSFETとGe pMOSFETの写真 (右図)。

|

|

|

図1-2 III-V-OI-on-Ge基板上に作製されたInGaAs nMOSFETとGe pMOSFETのトランジスタ特性。III-V/Ge メタルS/D CMOSトランジスタの電流電圧特性 (左図)。良好なトランジスタ動作に成功していることがわかる。InGaAs-OI nMOSFETおよびGe pMOSFET は、それぞれ、Si トランジスタの約3.5倍の高い電子移動度 (右図) と約2.3倍の高い正孔移動度 (中央図) を実現した。

|

研究成果2: 高電子移動度極薄チャネルIII-V-OI MOSFETの開発

~実効チャネル膜厚1 nmのInGaAsコンポジットチャネルから成るIII-V-OI MOSFETの開発~

MOSFETの微細化に伴う漏れ電流の増大の解決策として、極薄チャネルの利用が期待されています。今回、全体のチャネル膜厚が10 nm以下のInGaAsコンポジットチャネルを有するIII-V-OI MOSFETを開発し、その動作実証に世界で初めて成功しました。

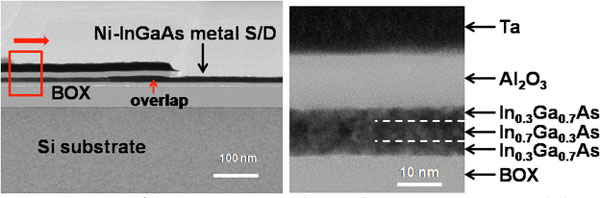

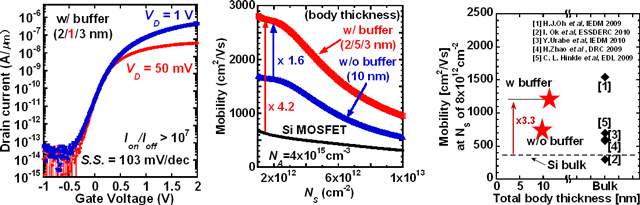

InGaAsコンポジットチャネルは、インジウム (In) 組成の高いInGaAs層をIn組成の低いInGaAs層で挟み込むことで、実際に電流が流れるIn組成の高いInGaAsチャネル層 (実効チャネル層) をゲート絶縁膜から遠ざけることができ、チャネル全体の膜厚が10 nm程度の極薄チャネル層においても電子の散乱を抑え、電流を流れやすくすることが可能です。住友化学の優れたエピタキシャル成長技術により作製された全体のチャネル膜厚10 nm以下の良質なInGaAsコンポジットチャネルを利用して、極薄チャネル III-V-OI MOSFETを作製しました。InGaAsコンポジットチャネルの透過型電子顕微鏡による断面観察の結果を図2-1に示します。良質なチャネルの形成が確認できます。図2-2にInGaAsコンポジットチャネルの動作特性を示します。ここで、実効チャネル膜厚を1 nmまで薄層化することに成功し、フロントゲート動作のみで、107を超えるオン電流/オフ電流比を実現しました。また、実効チャネル膜厚が5 nmの構造において、バルクのIII-V nMOSFETと同等の高い電子移動度、Si nMOSFETの約4.2倍の高い電子移動度を実現しました。これにより、高い移動度を保持したまま極薄チャネル III-V-OI MOSFETのスケーリングが実現されると期待されます。

|

|

図2-1 InGaAsコンポジットチャネルの断面写真。In組成の異なるInGaAs層により全体のチャネル膜厚10 nm以下のInGaAsコンポジットチャネルが形成されています。電流は中央のIn組成の高いInGaAs層 (実効チャネル層) を流れます。

|

|

|

図2-2 InGaAsコンポジットチャネルを有するIII-V-OI nMOSFETの性能評価。実効チャネル膜厚1 nmのInGaAsコンポジットチャネルを実現 (左図)。実効チャネル膜厚5 nmのInGaAsコンポジットチャネルを有するIII-V-OI nMOSFETにおいて、膜厚10 nmのInGaAs単層のIII-V-OI nMOSFETに対して約1.6倍、Si nMOSFETに対して約4.2倍の高い電子移動度を実現しました (中央図)。10 nm程度の極薄チャネル III-V-OI MOSFETで、バルクのIII-V MOSFET と同程度の高い電子移動度を実現しました (右図)。

|

研究成果3: メタル S/Dとメタルゲートを共通化した微細III-V/Ge CMOSプロセス技術の開発

高移動度チャネルIII-V/Ge CMOSのプロセスでは、チャネル材料が異なるため、集積化にはこれまで以上のプロセス複雑化が懸念されます。今回、微細III-V/Ge CMOSの実現に向け、異種チャネル材料に適した共通プロセス・材料を開発し、ゲート長100 nm 以下の微細III-V/Ge CMOSトランジスタの動作実証に世界で初めて成功しました。

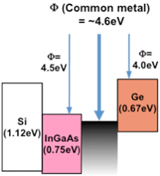

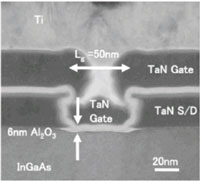

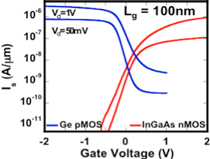

InGaAsとGeのバンドラインアップから (図3-1)、InGaAsの伝導帯端とGeの価電子帯端が極めて近いところに位置していることがわかります。このことから、n/pMOSFETの閾値制御の点で、ゲート電極材料の共通化が可能です。また、この共通メタル電極は微細化に適したショットキーバリアS/DトランジスタのメタルS/D材料としても有用です。つまり、異種チャネル材料にもかかわらず、ゲートおよびS/D電極を単一の材料で実現することが可能となります。このようなコンセプトのもと、共通メタル材料として窒化タンタル (TaN) を採用し、ゲート長100 nm以下の微細化が可能なゲートラスト法を用いて、InGaAs nMOSFETとGe pMOSFETを試作しました (図3-2)。図3-3は作製されたInGaAs MOSFETとGe pMOSFETの動作特性です。InGaAsチャネルとGeチャネルを使って対照的、かつ良好なトランジスタ特性を同時に得ることに成功しました。また、ゲート長100 nm以下における高いスケーリング耐性も示され、メタル材料の共通化により、III-V/Ge異種チャネル CMOSプロセスの集積化と微細化に成功するだけでなくCMOSプロセスの大幅な簡略化も同時に実現しました。

図3-1 InGaAsおよびGeのバンドラインアップ

|

|

図3-2 ゲート長50 nm のInGaAs nMOSFETの断面写真

|

|

図3-3 同一プロセスにより作製されたゲート長100 nmのInGaAs nMOSFETおよび Ge pMOSFETの電流電圧特性

|

このように、論理LSIのSiチャネルを、高い電子移動度を有するInGaAsなどのIII-Vチャネル、および高い正孔移動度を有するGeチャネルで置き換えた次世代高性能III-V/Ge CMOSトランジスタを実現しました。さらに、その高性能化に向けて、極薄チャネル III-V-OI MOSFETの性能向上とスケーリングに対応したIII-V/Ge CMOSトランジスタのプロセス技術の確立に成功しました。これらを実用化した次世代高性能CMOSトランジスタにより、コンピューター、サーバー、デジタル家電などの高性能化や低消費電力化が期待されます。

東京大学、産総研、住友化学、物材機構は共同研究により、シリコンプラットフォーム上III-V 族半導体チャネルトランジスタ技術の開発に関する共同研究を行っています。この共同研究成果はNEDOプロジェクト「ナノエレクトロニクス半導体新材料・新構造ナノ電子デバイス技術開発」 (シリコンプラットフォーム上III-V族半導体チャネルトランジスタ技術の研究開発) 【テーマリーダー 高木 信一】の委託を受けて行ったものです。2007年から2011年までの5年間、既存のトランジスタの性能を飛躍的に向上させる新しいトランジスタ構造や材料を開発しています。

この研究テーマでは、16ナノ世代以降のLSI用トランジスタに向けた材料選択肢を検討するための新たなエンジニアリング手法を提案し、将来の極微細トランジスタの構造として期待されているIII-V-OI構造トランジスタを、Si基板上で実現することを目指しています。III-VチャネルはSiよりも大きな電子移動度を持つため、高い電流駆動力を持つことが期待されています。一方で、実用化に向けては、既存のSi LSI製造技術でトランジスタが作製可能であることが重要です。そのため、III-VチャネルをSi基板上に集積する必要があります。しかし、従来の結晶成長を用いた方法では、III-VチャネルのSi基板上への集積はとても困難でした。そこで、本研究においては、基板直接貼り合わせ技術を利用してIII-V-OI構造を作製することを提案しています。これまで、直接基板貼り合わせ手法を用いて、Si基板上にSiO2やAl2O3をBOX層として、膜厚が3.2 – 100 nmのIII-Vチャネルの集積に成功し、高い電子移動度有するIII-V-OI MOSFETの開発を世界に先駆けて行ってきました。これまでにも、その成果を、2009 Symposia on VLSI Technologyや2010 Symposia on VLSI Technology、2010 International Electron Device Meetingなどにおいて報告してきました。今回、高い電子移動度を有するIII-Vチャネルと高い正孔移動度を有するGeチャネルとの集積に成功し、III-V/Ge CMOSトランジスタを世界で初めて実現したので、これを2011 Symposia on VLSI Technologyにおいて報告します。