III-V族化合物半導体の高い移動度を利用した次世代CMOSトランジスタを実用化するための3つの基本技術である極薄チャネルの形成、メタルソース/ドレイン(S/D)接合の形成、および電子移動度の向上に世界で初めて成功しました。これにより、従来のシリコン(Si)トランジスタの限界を超える高移動度CMOSトランジスタの実現が期待されます。

国立大学法人 東京大学【総長 濱田 純一】(以下、「東京大学」という)、独立行政法人 産業技術総合研究所【理事長 野間口 有】(以下、「産総研」という)、住友化学株式会社【代表取締役社長 廣瀨 博】(以下、「住友化学」という)、独立行政法人 物質・材料研究機構【理事長 潮田 資勝】(以下、「物材機構」という)は、シリコンプラットフォーム上III-V 族半導体チャネルトランジスタ技術の開発に関する共同研究を行っています。今回、東京大学のデバイス作製技術、産総研の絶縁膜形成技術、住友化学の結晶成長技術というそれぞれの強みを生かし、III-V MOSFET実用化に向けた3つの基本技術、極薄チャネル形成技術、メタルS/D形成技術、高移動度界面制御技術を開発しました。

この成果の詳細は、最先端のデバイス技術が報告される”2010 International Electron Device Meeting” (IEDM 2010) (2010年12月6日~8日、San Francisco)において、3件の論文として発表され、中でも、極薄チャネルIII-V MOSFETの開発に関する論文は、当該会議のハイライトペーパーの中の1件に選出されました。

本研究は、平成19年度から開始された、独立行政法人 新エネルギー・産業技術総合開発機構(NEDO)プロジェクト「ナノエレクトロニクス半導体新材料・新構造ナノ電子デバイス技術開発」 (シリコンプラットフォーム上III-V族半導体チャネルトランジスタ技術の研究開発) の委託を受けて行ったものです。

■ ポイント ■

ポイント1-3の基本技術を応用することで、III-Vチャネル高移動度CMOSトランジスタが実現可能となります。

ポイント1:極めて薄いチャネルを形成する技術の開発

-

3.5 nmの極めて薄いIII-VチャネルをもつIII-V MOSFET、さらに薄膜埋め込み酸化膜(BOX)を組み合わせたダブルゲートIII-V MOSFETを開発し、その動作実証に世界で初めて成功しました。

ポイント2:自己整合型プロセスによるメタルS/D MOSFETの開発

ポイント3: III-V MOSFET高移動度化技術と移動度決定要因の解明

■ 成果の要約 ■

研究の成果1: 極薄チャネル形成技術の開発 ~厚さ約3.5 nmの極薄インジウムガリウムヒ素(InGaAs)チャネル、厚さ10 nm程度の薄膜酸化アルミニウム(Al2O3)BOX層をもつダブルゲートIII-V MOSFETの開発~

MOSFETの微細化に伴い漏れ電流が増大する問題を解決する構造として、極めて薄いチャネル構造が期待されています。我々は、基板貼り合わせ技術を利用して、極薄チャネル

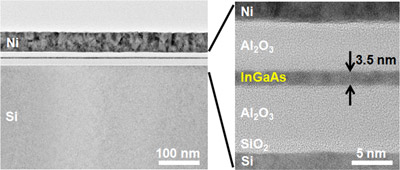

III-V-On-Insulator (III-V-OI)基板を開発しました。作製した極薄チャネル構造の透過型電子顕微鏡による断面観察の結果を図1-1に示します。3.5 nmの極めて薄い厚さにもかかわらず、高品質なIII-Vチャネルが一様に形成されていることがわかります。この極薄チャネル構造は、InGaAsを

エピタキシャル成長したIII-V層を良好な結晶構造を保ったままSi基板上に積層することで作製しました。この基板を利用して、極薄チャネルIII-V MOSトランジスタを作製し、フロントゲートにより良好なトランジスタ動作を実現することに成功しました。

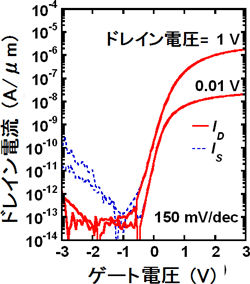

極薄チャネルの下部にあるBOX層を薄くすると、フロントゲートとバックゲートを同時に利用するダブルゲート動作が可能です。そこで、今回、Al2O3 を材料として用いて10 nm程度の薄膜BOX層を実現し(図1-1)、ダブルゲート動作を実証しました。その結果、III-Vチャネルとしては良好な電流電圧特性、10の7乗程度の高いオン電流/オフ電流比を得ることに成功しました(図1-2)。この技術は、絶縁層を介して基板を貼り合わせ方法であるため、III-Vチャネル以外の各種高移動度チャネル材料への応用も期待できます。

|

図1-1 極薄チャネルの断面写真。Si基板の上に自然酸化膜(SiO2)を介して10nmのAl2O3 BOX層と3.5nmのInGaAs極薄チャネルを積層してIII-V-OI構造を形成した。InGaAsの上のAl2O3とNiは、トランジスタのゲート絶縁膜および電極である。

|

|

図1-2 極薄チャネルを用いたダブルゲートMOSFETのドレイン電流-ゲート電圧特性。電圧を加えることにより、電流がオフ状態からオン状態へ約7桁変化している。

|

研究の成果2: Ni-InGaAs反応層を用いた自己整合型メタルS/D III-V MOSFETの開発

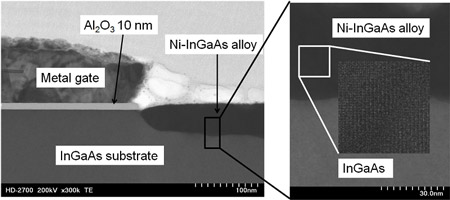

高移動度チャネル材料として期待されているIII-V族化合物半導体ですが、伝導度を制御するために添加する不純物の固溶限がSiに比べて1~2桁低いため、従来法であるイオン注入によるS/D形成では、S/D領域の抵抗を低減することが極めて困難です。今回、NiとIII-Vチャネルとの反応により、低抵抗のS/Dが形成できることを、世界で初めて見い出しました。本方法で形成されるS/Dのシート抵抗は、従来法のイオン注入に比べて約1/3まで低減されています。III-VチャネルとしてInGaAsを用い、自己整合型プロセスにより作製したMOSFETの断面観察結果を図2-1に示します。メタルとIII-Vチャネル界面において、欠陥のない非常に急峻な界面の形成が確認できます。この自己整合型メタルS/D III-V MOSFETが良好な電気特性を示すことも確認しています。

さらに、III-Vチャネル層に含まれるIn組成を高めてショットキーバリアの高さを下げることで、S/Dの抵抗をさらに低減することにも成功しました。このS/D形成技術は、Ni膜厚を制御することで極浅接合の形成が可能であるため、微細化に伴う漏れ電流の増加を抑えるためにも有効であると期待されます。

|

|

図2-1 メタルS/D接合をもつIII-V MOSFETの断面写真。Ni-InGaAs合金の部分がメタルS/Dであり、これがIII-Vチャネルに対して低抵抗な接合を形成している。

|

研究の成果3: III-V MOSFET高移動度化技術と移動度決定要因の解明

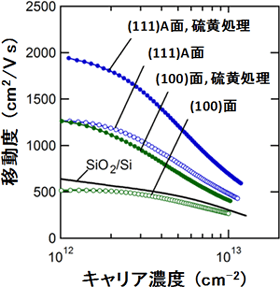

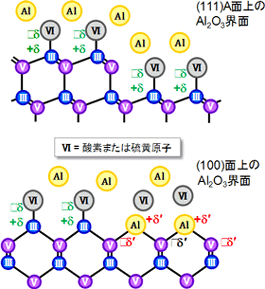

MOSFETを作製する際には、通常は(100)面と呼ばれる結晶面を用います。我々は、InあるいはGaから構成される(111)Aと呼ばれる面の上で良質なIII-V結晶を成長する技術を確立した上で、この面を用いてMOSFETを作製することにより、電子移動度が向上することを見い出しました。これに加えて、III-V表面を硫化アンモニウム溶液に浸すという簡便な方法を用いて表面を硫黄原子で終端することにより、移動度がさらに向上することが明らかになりました(図3-1)。III-VチャネルとしてInGaAsを用いた場合 (111)A面を硫黄で終端した上に作製したMOSFETは、電流を担うキャリア電子の濃度が平方センチメートルあたり10の13乗個という高い濃度条件においても、シリコンの2倍以上の移動度を示します。このことから、この高移動度化技術はCMOSの電流駆動力を高めるための有望な手法であると言えます。

MOSFETの高移動度化には、半導体とゲート絶縁膜との界面近傍を走行する電子の散乱を抑制することが必要であることが知られています。我々は、デバイス特性の詳細な解析の結果、III-V MOSFETにおいては、界面に発生する電気双極子のゆらぎが散乱の原因になることを突き止めました。電気双極子による散乱は、従来のシリコンMOSFETでは移動度への影響は小さいとされており、III-Vチャネル特有の移動度決定機構と考えられます。この新たな知見は、移動度をさらに向上していくための界面設計の指針を与えるものです。

|

|

|

|

図3-1 様々なInGaAs表面上で作製したMOSFETの移動度。(100)面に比べて(111)A面上で移動度が大きく向上している。また、いずれの面でも、硫黄処理を施すことで移動度が向上する。

|

|

図3-2 III-VチャネルとAl2O3ゲート絶縁膜と界面に発生する電気双極子のモデル。(111)A面上では電気双極子の正負の方向が揃って移動度が向上する。(100)面上では電気双極子の正負の方向が揃わず、移動度が低下する。

|

このように、極薄チャネルIII-V MOSFETを開発し、世界で初めてSi基板上においてそのトランジスタ動作を実証し、メタルS/D形成技術を導入してIII-V MOSFETの動作実証を行いました。そして、高移動度技術を開発するとともに、さらなる高移動度化のための指針となる移動度決定機構を明らかにしました。これらの成果により、論理LSIのSiチャネルをInGaAsなどのIII-Vチャネルで置き換えるための3つの基本技術である、極薄チャネル形成技術、メタルS/D形成技術、及び、高移動度界面技術が確立されました。これらを実用化した次世代超高速CMOSトランジスタにより、コンピューター、サーバー、デジタル家電などの高性能化や低消費電力化が可能になると期待されます。

東京大学、産総研、住友化学、物材機構は共同研究により、極薄チャネル形成技術、メタルS/D形成技術、界面制御技術を開発しました。なお、この共同研究成果はNEDOプロジェクト「ナノエレクトロニクス半導体新材料・新構造ナノ電子デバイス技術開発」 (シリコンプラットフォーム上III-V族半導体チャネルトランジスタ技術の研究開発) 【テーマリーダー 高木 信一】の委託を受けて行ったものです。2007~2011年までの5年間、既存のトランジスタの性能を飛躍的に向上させる新しいトランジスタ構造や材料を開発しています。 この研究テーマでは、22ナノ世代LSI用トランジスタに向けた材料選択肢を検討するための新たなエンジニアリング手法を提案し、将来の極微細トランジスタの構造として期待されているIII-V-OI構造トランジスタを、Si基板上で実現することを目指しています。

このプロジェクトでは、トランジスタのチャネル部に用いる材料を、SiからIII-V族化合物半導体に置き換えることを提案しています。III-VチャネルはSiよりも大きな電子移動度をもつため、高い電流駆動力を持つことが期待されています。実用化に向けては、既存のSi LSI製造技術でトランジスタが作製可能であることが重要です。そのため、III-VチャネルをSi基板上に集積する必要があります。しかし、従来の結晶成長を用いた方法では、III-VチャネルのSi基板上への集積はとても困難でした。そこで、本研究においては、基板直接貼り合わせ技術を利用してIII-V-OI構造を作製することを提案しています。これまで、III-Vチャネル膜厚が100 nm程度と比較的厚いIII-V MOSFETの作製に適した直接基板貼り合わせ技術を用いて、Si基板上に埋め込み酸化膜層を介して積層したIII-V MOSFETを開発し世界で初めてその動作実証に成功し、その結果を2009 Symposia on VLSI Technologyや同2010などにおいて報告してきました。