独立行政法人 産業技術総合研究所【理事長 野間口 有】(以下「産総研」という)ナノ電子デバイス研究センター【研究センター長 金山 敏彦】秋永 広幸 副研究センター長、先進ナノ界面デバイス研究チーム 島 久 研究員は、シャープ 株式会社【代表取締役社長 片山 幹雄】(以下「シャープ」という)、株式会社 アルバック【代表取締役社長 諏訪 秀則】(以下「アルバック」という)半導体電子技術研究所【所長 鄒 弘綱】、国立大学法人 金沢大学【学長 中村 信一】(以下「金沢大学」という)大学院 自然科学研究科【研究科長 福森 義宏】北川 章夫 准教授、中山 和也 准教授と共同で、低消費電力、高速動作の性能を兼ね備えた不揮発性の抵抗変化メモリー素子を128 Kbitのメモリーチップに集積化するプロセスを開発し、8インチウエハー上にチップアレイを作製することに成功した。なお、このメモリーは、抵抗変化メモリー(Resistance Random Access Memory : RRAM)と呼ばれる。

このRRAMチップアレイは既存の半導体製造プロセスを用いて作製されており、貴金属電極など高価な部材や、特殊な取り扱いを必要とする原料も用いていない。そのため、ビットコスト競争力に優れているだけでなく、省資源・省エネルギーを実現するメモリーである。

今回の開発により、大容量の情報を高速にやり取りする機能を持つ素子の重要性がますます高まってきている情報・エレクトロニクス分野において、省エネルギーの鍵となるRRAMの動作性能・信頼性評価をチップレベル・ウエハーレベルで実施するための評価プラットホームが構築できた。今後は、この新規メモリーの早期の実用化・事業化を目指す。

なお、本成果は、2010年5月16~19日に、韓国ソウル市で開かれる第2回国際メモリーワークショップにおいて、5月18日に発表される。

|

|

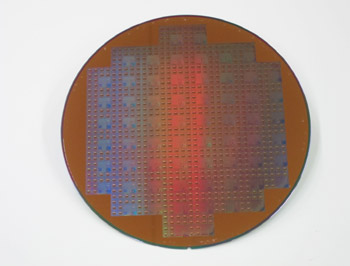

写真1 8インチウエハー上に作製した128 Kbit RRAMチップアレイ

|

近年、社会の高度情報化にともないPCをはじめとしたIT機器は産業活動や生活に欠かせないものとなり、急速に普及してきている。それにともなって、IT機器に関連した電力消費も急速に増大し、わが国の総電力消費量に占める割合はもはや無視できないほどとなってきた。一方でIT機器自体の高性能化もとどまることを知らないが、機能の高度化により必要なメモリーの容量も増大し続けてきた。そのためIT機器の省エネルギー化にはメモリーによる消費電力を減少させることが有効と考えられるようになっている。すなわち、現在主流のDRAMと同等以上の高速動作が可能であり、しかも低消費電力のメモリー、特に、データの書き込み読み出し時にだけ電力を消費しデータの保持には電力を消費しない不揮発性メモリーが望まれている。

RRAMは遷移金属酸化膜を金属電極で挟んだ構造で、酸化膜の電気抵抗変化を記憶情報とするメモリー素子である。低消費電力であり、高速書き換えに優れるため、RRAMは高度情報化社会を支える次世代不揮発性メモリーの有力候補として、その実用化が期待されている。

産総研では、抵抗スイッチ現象の起源解明と応用研究を行い、この現象を利用した抵抗変化メモリーの研究開発に取り組んできた。2006年に、RRAM素子の動作の高速化に成功した。その後、低電流動作と高速動作の両立やRRAM動作の定量的な制御を実現するべく研究開発を行い、2008年には超低消費電力、高速書き換えに優れたRRAM素子の開発に成功した。

これにより、素子単体の性能は飛躍的に向上したが、実用化のためには、メモリー素子を集積化した際に顕在化する問題点を解決し、統計的な信頼性データに基づいて、総合的なパフォーマンスを保証すること、そして、ウエハーレベルでのメモリーの量産プロセス技術を開発することが必要である。そのため、集積化回路とメモリーアレイをウエハーレベルで作製するプロセス開発と、メモリーアレイの信頼性テストを実施するための評価プラットホームを構築することとした。

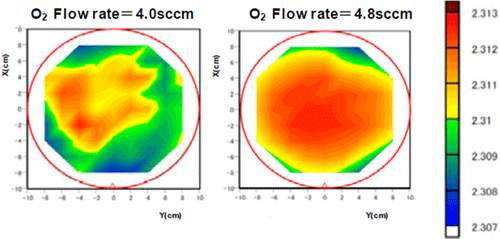

従来、ポストフラッシュメモリーの候補といわれる不揮発性メモリーの多くは、既存のSi製造ラインでは使用しない特殊な材料を用いるため、周辺要素技術の開発や追加の設備投資の必要性が生じてしまい、個別の性能ではフラッシュメモリーより優りながら、フラッシュメモリーの微細化のスピードに追いつかず、実用化ヘ向けた大きな障壁となっていた。これに対して、シャープとアルバックは、2008年に開発した超低電流動作と高速動作を両立可能なRRAM素子構造を8インチウエハー上に均一かつ高い信頼性を持って製造するための成膜・加工プロセス技術を開発し、128 Kbitのメモリーチップに集積化した。写真1に今回開発したRRAMチップアレイを示す。8インチウエハー上に約100個のRRAMチップが形成されている。RRAMのメモリー素子を構成する材料は現在のCMOSプロセスになじみのある材料である。このため、RRAMとCMOSプロセスは親和性が良く、RRAMのチップアレイを現行の半導体微細加工技術で集積化することができた。この特長により、新たな設備投資を必要最小限にすることができるため、RRAM素子はビットコスト競争力に優れたメモリー素子となる。8インチウエハー上へメモリーアレイを作製する上で重要な、酸化物薄膜の膜質の均一性について、薄膜のウエハー面内での屈折率を測定して評価した(写真2)。図中の色の違いは屈折率の違いをあらわし、膜質に対応している。成膜中に使用する酸素ガスの量をコントロールすることで、8インチウエハー面内に均一な薄膜を作製することができた(写真2右)。

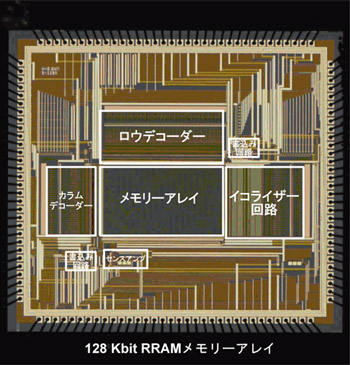

写真3はRRAMメモリーアレイチップの拡大写真である。チップのサイズはおおよそ5 mm角であり、チップ上に形成されたメモリーアレイに加えて、アドレスデコーダー、イコライザー、センスアンプ、書き込み回路が搭載されている。アドレスデコーダーや書き込み回路を用いて情報の書き込みを行い、センスアンプを用いて読み出しを行う。

また、このRRAMメモリーアレイチップは金沢大学が設計した評価用回路を用いているのでメモリーアレイの信頼性評価もできる。チップ上には、2 Kbit~128 Kbitまでのメモリーアレイを持つ16種類のテストエレメントグループが形成されている。メモリーアレイの動作電流制御にはチップ上に組み込まれたトランジスタを使用しており、1T-1R(1トランジスタ-1 RRAM)構造での信頼性評価が可能である。メモリー素子を低電流動作させることができれば、このトランジスタも微細化することができ、チップの量産やメモリーアレイの大容量化につながる。

写真4は今回開発した128 Kbit RRAMメモリーアレイのセンシング動作例である。メモリーアレイ中には、集積化された多数のメモリー素子がある。写真4のRAS、CAS、CSの3つの制御信号により、情報の書き込みまたは読み出しを行う場所(アドレス)の指定が行われる。その後、SE制御信号により、RRAM素子に記録された抵抗値を電圧の高低に変換して指定されたアドレスに記録されているデータをVoutに出力する。写真4には、データ1が書き込まれた状態(erase)と、データ0が書き込まれた状態(program)の2つのメモリーセルのデータ読み出し結果が並べて表示されている。データの読み出しに要する時間はわずか8.5 nsである。この回路によって、メモリーアレイの動作検証、動作アルゴリズムの開発や、統計的信頼性評価を実施することが可能である。

今回の開発により、チップレベル、ウエハーレベルでメモリーの動作検証、信頼性評価を実施するためのプラットホームが構築できた。チップ上には多様な信頼性評価内容に柔軟に対応するために複数種類のメモリーアレイを作製できる。ウエハーレベルでのチップ作製技術の確立によって、RRAMの早期実用化に向けた研究開発が加速されると期待できる。

|

|

写真2 8インチウエハー面内の屈折率分布の成膜条件依存性

|

|

|

写真3 128 Kbit RRAMメモリーアレイチップ

|

|

|

写真4 開発したメモリーアレイのセンシング動作例

|

今後は、開発した評価プラットホーム上でRRAM素子のアレイレベル、チップレベルでの信頼性評価を実施して、製品化に向けた課題の抽出と解決を行い、RRAM素子の早期の実用化・事業化を目指す。