独立行政法人 産業技術総合研究所【理事長 吉川 弘之】(以下「産総研」という)ナノテクノロジー研究部門【研究部門長 南 信次】分子ナノ物性グループ【研究グループ長 水谷 亘】清水 哲夫 主任研究員と内藤 泰久 研究員は、株式会社 船井電機新応用技術研究所【代表取締役社長 小野 雅敏】(以下「船井電機研究所」という)と共同で、ナノギャップ間隔の変化により抵抗値が大きく変化するナノギャップ不揮発性メモリー技術を発展させ、集積化可能な縦型構造の開発に成功した。

これは産総研のシーズ技術であるナノギャップ不揮発性メモリー素子を発展させたものである。今回、不揮発性メモリー素子の性能として、10ナノ秒のパルス電圧での書き込み・消去可能な高速スイッチング動作及び、10万回以上の繰り返し動作や長時間の保持特性といった高い安定性を確認した。さらに、トンネル抵抗を多段階に制御することにより、一つの素子に

多値(4値)記憶できることを実証した。本メモリー素子は、メモリー部が単一金属でも実現可能であり、添加物を必要としないため、組成むらなどを気にせず究極的に微細化できる可能性を秘めており、将来の超高密度不揮発性メモリー実現への貢献が期待できる。

本技術の詳細は、2008年12月3日~5日に幕張メッセで開催される展示会セミコン・ジャパン2008(SEMICON JAPAN 2008)において、発表する予定である。

|

|

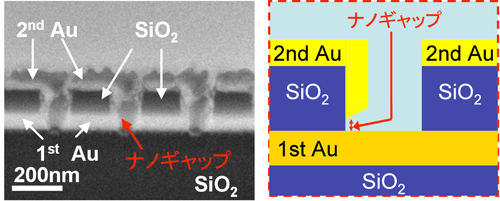

図1 今回の縦型ナノギャップ不揮発性素子のSEM像及び断面図 |

ノートパソコンの高性能・高機能化やデジタルカメラの高画質化などにより、小形で大容量のカード型メモリーデバイスが、日常的に多く使用されている。またハードディスクドライブの代わりにフラッシュメモリーを搭載した大容量不揮発性メモリー(SSD(Solid State Drive)など)を利用したパソコンも増えてきている。しかし、フラッシュメモリーは動作速度が遅く、ストレージデバイスとしての利用が主であるのが現状である。そのため、フラッシュメモリーと同等な高集積性と、揮発性メモリーに迫る高速性を持った不揮発性メモリーができれば、より広い用途が期待できる。高集積性と高速性の両立を目指し、特に抵抗変化を利用した抵抗変化メモリーや相変化メモリーなどが精力的に研究されている。

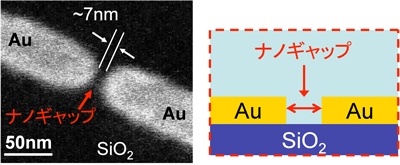

産総研では、対向した2つの金属電極の間にナノメートルスケールの間隙を持つナノギャップ構造(図2)が、特異な電流電圧特性を示し、不揮発性メモリー素子に応用できる可能性を見いだした。

|

|

図2 従来の平面型ナノギャップ不揮発性素子のSEM像及び断面図 |

このメモリー素子は、対向した金属電極のみからなる単純な構造で、さらに既存のプロセスとも整合性よく、金属電極に各種単一金属・合金・シリコンなど幅広い材料が使用できるため、新規不揮発性メモリーを実現できる可能性を持っていることが判明した。(主な研究成果-2007年6月19日)

その後、産総研は、新規不揮発性メモリー技術について船井電機研究所と共同研究を行い、さらに昨年度から京都大学を加えて連携をはかり、このメモリーのメカニズム解明の研究、集積化デバイス作製・評価の技術開発に取り組んできた。しかし、これまでの素子構造(図2)は、メモリー部となるナノギャップ部が絶縁体基板上に平面で配置した構造であったため、配線を含めた素子のサイズが大きくなり集積化には不向きであった。そのため集積化に適した構造の開発が求められてきた。

なお、本研究開発の一部は、経済産業省の委託事業「ナノエレクトロニクス半導体新材料・新構造技術開発-うち新材料・新構造ナノ電子デバイス<超稠密金属ナノギャップ不揮発性メモリの研究開発>」による支援を受けて行ったものである。

産総研は、これまでにシリコン基板上に作製した10nm程度の微小間隙を持つ金属電極に電圧を加えると、不揮発メモリーとして使える抵抗変化が発生することを見いだした。この抵抗変化は、外部パルス電圧刺激により金属間の間隙幅が変化することによる、トンネル抵抗の変化(図3)を反映したものである。しかし、従来型の平面構造(図2)では配線構造を含めた素子のサイズが大きく、集積化には向いていなかった。

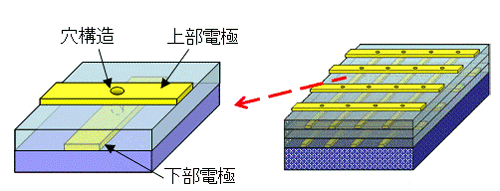

このため、今回新たに、酸化シリコン層にエッチングで穴構造を作製し、その穴の壁面にナノギャップ構造を作りこむ縦型構造の開発に成功した(図1)。この構造は図4のように配線構造の交差点のみに素子を作製できるため、平面型と比べ集積化に非常に適した構造である。また、ナノギャップ部も金属でできているため、同時に配線構造も作製できるメリットもある。実際に、このナノギャップ不揮発性メモリーがこの穴の中だけで作りこまれていることを確認し、良好なメモリー動作を確認した。

|

図4 縦型ナノギャップ不揮発性素子の集積化構造のイメージ図

|

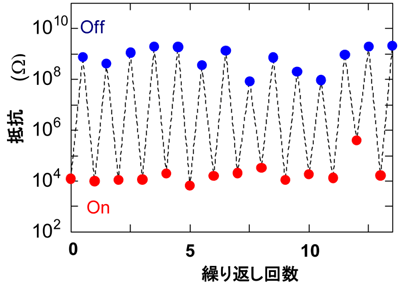

また、本ナノギャップ不揮発性メモリー素子の抵抗変化のOn・Off比は、104-107にも達し、10万回以上の状態変化が可能であった。また、10ナノ秒という短いパルスの電圧でも抵抗値を切り替えられることを確認した(図5)。記憶状態の保持期間も半年を越えてもほぼ変化していなかったことから、長時間の保持時間を有していることが確認された。これらの結果から、基本的特性としてナノギャップ構造を用いた素子は、次世代不揮発性メモリーとして期待できる。

|

図5 10ナノ秒パルス電圧印可による抵抗スイッチ効果

|

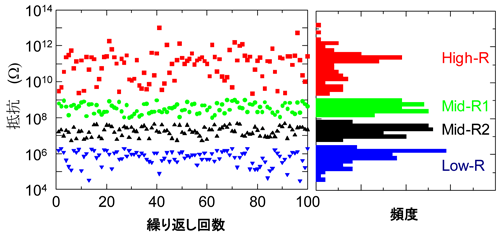

さらに本素子は印加パルス電圧によってトンネル抵抗を制御できるため、一つのメモリー素子で、複数個の記憶状態を持つ多値記憶が安定して可能であることがわかった。図6の結果は、印加電圧値の制御により、一つの素子に4つの状態(2bit)を作りだせることを示しており、縦型構造の実現とともにこのナノギャップを用いた不揮発性メモリー素子が高集積可能であることを示している。

|

図6 4つの抵抗変化状態間の繰り返し測定結果(左図)およびその抵抗分布(右図)

|

実用化を目指して、シリコン基板上にさらなる集積化テストデバイスを作製し、個々の素子のバラツキ評価を行う予定である。バラツキ評価結果とともに、メモリー特性の改善を進め早期に次世代不揮発性メモリーの実現につなげたい。