独立行政法人 産業技術総合研究所【理事長 吉川 弘之】(以下「産総研」という)パワーエレクトロニクス研究センター【センター長 荒井 和雄】は、炭化ケイ素(SiC)半導体のカーボン面にIEMOS(Implantation and Epitaxial MOSFET)と呼ばれる素子を形成する技術を開発した。

SiCは大電力を制御できるので次世代の省エネルギーパワー素子として期待されている。産総研は以前IEMOSの開発に成功し当時世界最小の電気抵抗4.3 mΩcm2を実現していたが、今回SiC結晶のカーボン面にIEMOSを形成することによってさらに世界最小の抵抗値1.8mΩcm2を達成した。この値は現在使われているシリコン(Si)パワー素子と比較して約1/10以下なので、動作時の電力損失も約1/10と非常に小さい。

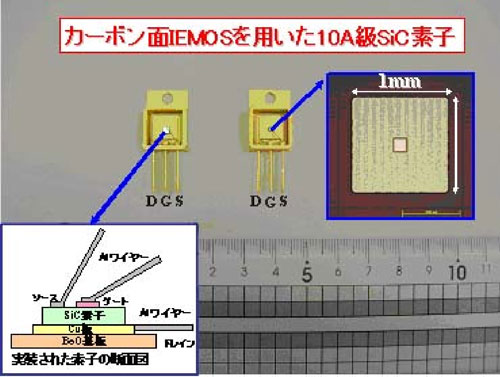

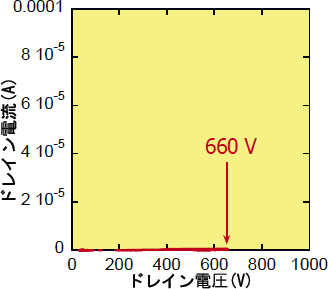

また、電流容量も家庭用電化機器に要求される10A級素子を作製した(図1参照)。今後この素子は、IHヒーター、エアコン、パソコンサーバー等の家庭用電化機器に適用することで使用電力を大幅に削減できる。

|

|

図1 カーボン面IEMOSを用いた10A級SiC素子

|

本成果の詳細は、12/11~12/13にサンフランシスコで開催される2006年IEDM(International Electron Device Meeting)において発表する予定である。

パソコンなどに使われているシリコン(Si)半導体は大電力を制御するには不向きである。不向きではあるがダイオード整流器やエアコンのインバーター制御などに広く使われている。しかしこれはかなりの電力損出をしながら無理して使っているのであって、耐熱性や耐電圧性に優れた炭化ケイ素(SiC)半導体を使うと、はるかに少ない電力ロスで、しかももっと大きな電力を制御できるようになる。

SiC素子は、理論的には通電状態での抵抗値(オン抵抗値)をSi素子よりも2桁下げることができる。IHヒーター、エアコンやパソコンサーバー等の家庭用電化製品や、車載用半導体素子、配電系の大電力変換素子にSiCが使用されると電力損失を大幅に削減できると期待されている。SiC素子の実用化によりパワーエレクトロニクス関連のインバーター化が加速されれば、2030年には原油換算で4466kl/年もの削減効果が上がると試算されている。

すでにSiC基板は、日本、ヨーロッパ、アメリカの企業が販売しており、最近4インチ基板の販売も開始され、SiC素子産業の下地はできつつある。また、SiC素子は、SBDがヨーロッパ、アメリカの企業が販売を開始しており、実用化が加速している。

スイッチング素子SiCパワーMOSFETは、動作時の抵抗(オン抵抗という)が小さくスイッチング速度が速いために期待が大きいが、オン抵抗がSiのそれを下回ったものの、理論的限界値よりはかなり大きく、エアコンやIHヒーターで使用された場合に十分な性能を発揮できない。

従来、SiCパワーMOSFETは、DIMOS(Double-Implanted MOSFET)と呼ばれる構造で作製される。この構造では、ゲート酸化膜と接しているPウエルと呼ばれるSiC領域(図2・3参照)は、アルミニウムをイオン注入した後に、1600℃以上の高温で熱処理をして形成される。この時に、熱処理前は平坦であるSiC表面から、Siが蒸発することにより、表面が荒れて、凹凸が大きくなる(図3)。ここを流れる電子が凹凸部分に衝突して散乱されることにより、電子が流れにくくなるので、チャネル移動度が低くなり、全体の抵抗値も高くなる。

これに対して、産総研ではこれまでに、独自にIEMOS(Implantation and Epitaxial MOSFET)と呼ばれる構造を開発した(図4・5参照)。IEMOSでは、Pウエルの表面は、エピタキシャル層で形成しているため、1600℃以上の高温での熱処理が必要なく、平坦であり(図5)、電子の流れが良くなり、高いチャネル移動度が得られるので、全体の抵抗値が低くなる。また、Pウエルの底部は、高濃度のイオン注入で形成されると同時に、Pウエル間のN型領域の構造を耐圧がでるように設計することにより高耐圧が得やすい特徴を有している。これによって当時世界最小の電気抵抗4.3 mΩcm2を実現していた。

産総研は、経済産業省からの運営交付金や委託研究費をベースに、独立行政法人 新エネルギー・産業技術総合開発機構(NEDO)との委託契約に基づき実施するプロジェクトで開発を進めてきた。SiC素子化の基盤技術を「超低損失電力素子技術開発」プロジェクト(H10年~H14年)において、SiC素子の開発を「エネルギー使用合理化技術戦略的開発」課題(H15年~H17年)で行い、今回、これらのプロジェクトの成果を踏まえてNEDO「パワーエレクトロニクスインバーター基盤技術開発」プロジェクトを平成18年の7月から3年計画で実施している。

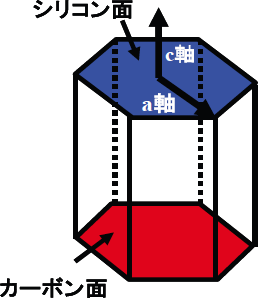

今回の発表は、以前に産総研の開発したIEMOSをSiC結晶のカーボン面に作製する技術を開発した内容である。SiC結晶には、様々な面方位がある(図6参照)。従来、SiC素子は、代表的な面方位であるシリコン面上に形成されてきた。この理由の一つは、SiC素子は、SiC基板上に濃度を制御したエピタキシャル層を有するSiCエピタキシャル基板上に作製されるが、これまで、カーボン面上へのP型のエピタキシャル層の形成は困難とされ、SiC結晶シリコン面上にエピタキシャル層が形成されてきた背景がある。今回パワーエレクトロニクス研究センターは、世界で最初に独自技術によりカーボン面上へのP型のエピタキシャル層の形成に成功した。

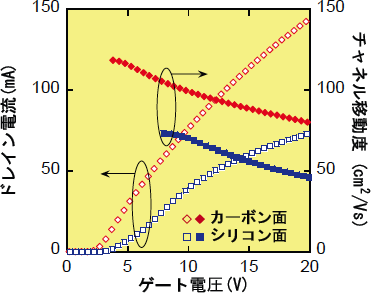

もう一つの改良は、ゲート酸化膜の形成方法である。これまで、カーボン面とゲート酸化膜の間の界面の欠陥密度は、シリコン面とゲート酸化膜界面のそれよりも多いとされてきたが、ゲート酸化膜を水蒸気と酸素の混合ガスで形成し、その後に水素でアニールすることにより、シリコン面よりも界面の欠陥密度を下げて、チャネル領域の移動度をシリコン面の約6割増加することによりチャネル抵抗を大幅に下げることに成功した(図7参照)。

図6 SiC の結晶構造

|

|

図7 カーボン面とシリコン面の比較

|

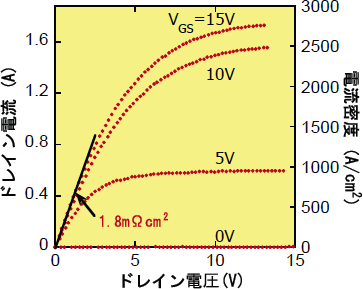

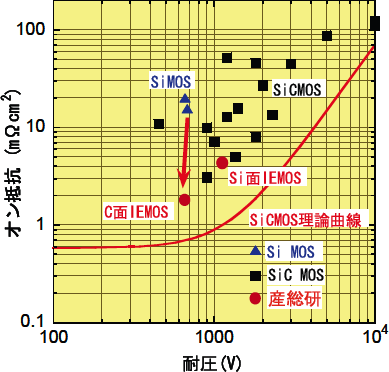

スイッチング素子SiCパワーMOSFETのオン抵抗の大部分をチャネル抵抗が占めるので、チャネル抵抗が下がるとオン抵抗も大幅に下がり、世界最小値の1.8mΩcm2を達成した(図8,10参照)。

面積が1mm2の素子を作製したところ、電気容量は、10Aとなった。また、絶縁破壊耐圧は、660Vとなり(図9参照)、IHヒーター、エアコン、パソコンサーバー等の家庭用電化機器に要求される仕様を満たしている。さらに、この素子はゲート電圧が印加されていない時は電流が流れないノーマリーオフ型であるので、インバーターに応用する場合にゲート制御が容易である。

現在、シリコン(Si)パワー素子で最もオン抵抗が低い素子は約20mΩcm2である。今回のIEMOSのオン抵抗は、1.8mΩcm2であり、Siパワー素子の1/10以下である。将来、炭化ケイ素(SiC)パワー素子が家庭用電化機器においてシリコン(Si)パワー素子にとって替わることにより、省エネルギー化が加速すると期待される。

図8 開発したカーボン面上IEMOS の電流-電圧特性

|

|

図9 開発したIEMOS の逆方向特性

660Vまでは、電流が流れないが、それ以上では大電流が流れ、素子が破壊する。

|

|

|

図10 MOSFET のオン抵抗と耐圧の関係

|

今回、世界で初めて、ユニポーラ型素子で660Vもの高耐圧で、オン抵抗1.8mΩcm2以下を達成し、10A級素子の試作にも成功した。今後はNEDO「パワーエレクトロニクスインバーター基盤技術開発」プロジェクトにおいて、10A以上の容量の素子を活用してSiCインバーターの極限的性能を明らかにする。実際にインバーターを試作し、実際の使用における条件を明らかにすることにより、エアコンやIHヒーター等の家庭用電化製品や、車載用半導体素子、配電系の大電力変換素子へのSiC素子の適用性を明確にし、普及・実用化を加速したい。また、パワーエレクトロニクスメーカーへのSiC素子のサンプル供給も視野にいれている。

エピタキシャル成長技術は、平成18年産総研研究者が財団法人電力中央研究所研究者、昭和電工株式会社と設立したベンチャー事業体である有限責任事業組合エシキャット・ジャパンへの移転が行なわれており、すでにSiCエピタキシャルウエハの市販が開始されている。