独立行政法人 産業技術総合研究所【理事長 吉川 弘之】(以下「産総研」という)次世代半導体研究センター【センター長 廣瀬 全孝】と技術研究組合 超先端電子技術開発機構【理事長 西田 厚聰】(以下「ASET」という)は、独立行政法人 新エネルギー・産業技術総合開発機構の委託事業である半導体MIRAIプロジェクト(次世代半導体材料・プロセス基盤(MIRAI)プロジェクト)【プロジェクトリーダー 渡辺 久恒】において、共同で、特定の方向にのみ、ひずみを有する立体型のn型トランジスタ作製技術を開発し、究極的な高性能化を実現しました。

2013年に量産開始が目標とされている32nm(ナノメートル)の微細LSIは、構造が超微細化するため現在のトランジスタの構造では電流駆動力が向上せず情報処理速度が頭打ちになり、また、リーク電流によるスイッチング特性の低下などで消費電力が増加すると考えられています。

これを解決するため、新しい構造のトランジスタの実現が切望されています。今回、シリコンの(110)結晶面に引張りひずみを加え、その方向に電流を流すと、電子の移動度を大幅に向上できることを見出しました。この知見に基づき実際に立体構造マルチゲート型のn型トランジスタを作製し、性能向上を実証しました。

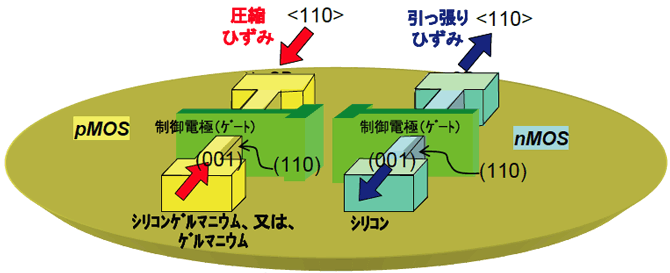

実際のLSIを構成するには、n型とp型と2種類のMOSトランジスタが必要ですが、すでに、半導体MIRAIプロジェクトでは、一軸性圧縮ひずみを加えたシリコンゲルマニウム(SiGe)結晶の(110)結晶面を用いた高性能p型トランジスタを実現しており、今回のひずみ構造n型トランジスタの実現により、本格的な32ナノ世代LSI用のマルチゲートCMOSが実現可能になりました。

今回開発した技術は既存の製造装置と製造工程をそのまま利用でき、実用化を図る上で極めて有利であると考えています。

|

|

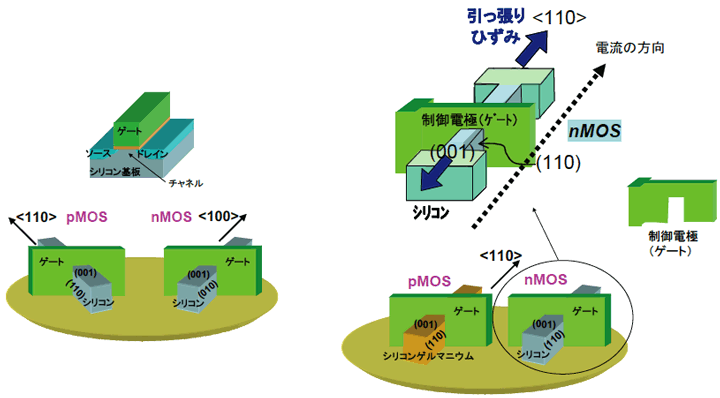

図1 上左:従来型の平面構造のMOSトランジスタ、上右:今回開発の立体型ひずみn型トランジスタ(nMOS)。

下左:従来設計の立体構造CMOSトランジスタ、下右:今回開発により可能となった立体構造CMOSトランジスタ。

|

この成果の詳細は、2006年12月12日に、米国サンフランシスコで開催される“2006 International Electron Device Meeting”(IEDM2006)において発表いたします。

LSIに用いられるMOSトランジスタは、寸法の微細化が回路性能の向上につながるため、より微細な素子の実現を目指して、激しい開発競争が続いている。微細化に伴う課題も顕在化してきており、このままではトランジスタの性能を上げると同時に消費電力も下げるという、従来の技術進歩のトレンドを維持することが困難であることが指摘されている。特に、2013年に量産が開始される32ナノ技術世代以降では、従来のシリコン(Si)をチャネルとするMOSトランジスタを用いる限りは物理的な性能限界に突き当たる。その解決には、新しいチャネル材料やチャネル構造を採用し、チャネル中を走行するキャリアの速度を増加させることが必須である。また、研究開発期間の短縮と製造コストの低減のために、既存の製造装置と製造工程を利用できることが必要である。

半導体MIRAIプロジェクトでは、将来の高性能低消費電力LSIを実現するためには、移動度増大技術とマルチゲート構造の適切な融合が必須であると考え、平面型トランジスタにおけるさまざまな材料検討に加えて、マルチゲート構造にひずみを印加し、移動度を向上させる研究開発をしてきた。

2005年度には、世界に先駆けて、高性能ひずみSiGe-on-Insurator(SGOI)マルチゲートpMOSトランジスタの動作実証に初めて成功している。

今回は、マルチゲートCMOS構造を提供するべく、n型ひずみSi-on-Insurator(SOI)マルチゲートMOSトランジスタの開発を行った。

LSIの高性能化は、主に基本構成素子であるMOSトランジスタの微細化により達成されてきたが、近年、従来の平面型トランジスタ構造では微細化に伴う短チャネル効果(電流のオン/オフ制御が困難になる現象)の抑制が困難となり、オフ電流の増大が深刻となってきた。そこで、チャネルを立体構造とし、ゲートの静電的な制御能力を増大させることにより短チャネル効果を抑制する、いわゆるマルチゲート構造が活発に研究されている。しかし、 (001)結晶面のシリコンウェーハを用いる従来通りの設計では、立体チャネルの側面は電子移動度が低いシリコン結晶の(110)面となってしまうため、n型MOSトランジスタの電流駆動能力が低下してしまうという問題があった。これを解決するには、n型MOSトランジスタとp型MOSトランジスタの方向を、45°傾ける必要があると考えられていた(図1左下)。

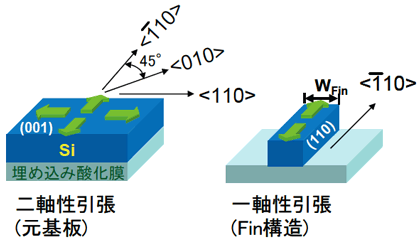

MIRAIプロジェクトでは、シリコン結晶面の(110)面の方向に一軸性引張りひずみ加え、この方向に電流を流すと電子の有効質量が小さくなり移動度が大幅に向上することを見いだした(詳細は用語説明を見てください)。この効果により、一軸性引張りひずみを(110)面を側面に持つ立体構造のチャネルに印加することにより、チャネルの側面部と上面部の移動度を共に最大化することができ、極めて電子駆動能力の高いマルチゲートn型MOSトランジスタが実現できた。一軸性引張りひずみは、図2に示すように元々面内に二軸性引張りひずみを有するSOI層を薄板短冊状(Fin状)に加工することにより導入した。Fin形状のような細い構造に加工することで、短手方向のひずみが緩和し、Fin形状の側面(110)面および上面(001)面に長手方向への一軸性引張りひずみのみを残存させることができる。このひずみの効果により側面となる(110)面で高い移動度が期待できる。さらに、上面である(100)面においても、ひずみの効果で移動度が向上することが知られており、結果として、図2の立体構造により、チャネルとなるすべての面において高い移動度が実現できる。

|

|

図2 横方向ひずみ緩和を利用して形成する一軸性引張りひずみSOI Fin構造、Fin構造にすると短軸方向のひずみが緩和される |

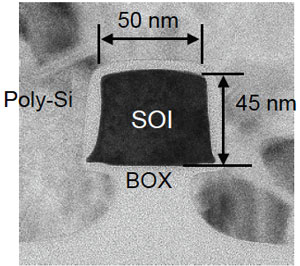

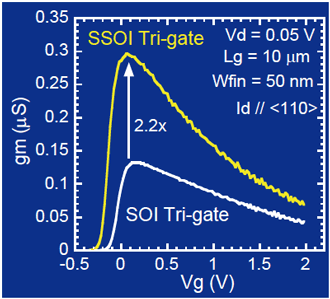

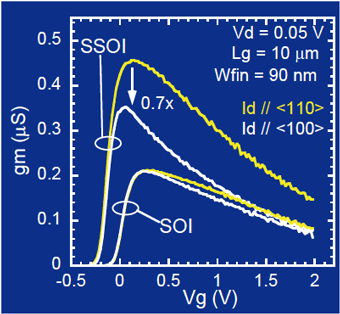

図3は、試作した一軸ひずみマルチゲート型MOSトランジスタ断面の透過電子顕微鏡(TEM)写真である。今回試作した素子の最小Fin幅は50nm、Fin高さは45nmである。図4は一軸ひずみマルチゲート型MOSトランジスタの増幅率(相互コンダクタンスgm)を無ひずみのマルチゲート型トランジスタと比較した結果で、ピーク値で2倍を超える高い増大が確認された。この結果は、上記の一軸性引張りひずみの有用性を明瞭に示している。

図3 一軸性引張りひずみマルチゲート型MOSトランジスタの断面TEM像。Poly-Si(多結晶シリコン)ゲートがシリコンSOIを取り囲んでいる

|

|

図4 一軸性引張りひずみマルチゲート型MOSトランジスタの無ひずみマルチゲート型素子との相互コンダクタンスgmの比較

|

一方、一軸ひずみマルチゲート型MOSトランジスタにおいて、Finの方向を45°回転し、立体チャネル構造の側面を(110)面から(100)面にすると、図5のようにgmが30%程度低下する。これは、(110)面での一軸ひずみによる移動度向上が極めて有効に働いていることを示している。

|

図5 マルチゲート型MOSトランジスタにおける相互コンダクタンスgmのFin(電流)方向依存性 |

最適マルチゲートCMOS構造の実証

従来、立体構造のマルチゲート型CMOSの駆動力を最大にするには、Fin構造の側面をn型MOSトランジスタは(100)面、p型MOSトランジスタは(110)面と45°傾ける必要があると考えられていた(図1左下)。これは、電子移動度は(100)面の方が(110)面より大きく、逆に正孔移動度は (110)面の方が大きいためであるが、これでは集積化する際の面積効率が悪く、またn型とp型トランジスタの方向をそろえて形成する従来の設計手法を大幅に変更しなければならないという問題点があった。しかしながら、今回、適切なひずみを印加することで、(110)面MOSトランジスタの電子状態(サブバンド構造)を、最適な状態に制御し、(110)面の電子移動度を大幅に向上させられることを初めて見出し、n型とp型トランジスタのFinの方向を揃えて、キャリアの移動度を、ひいては電流駆動力を共に最大化できることが明らかとなった。

図6は、マルチゲートCMOSの最適構造の模式図である。n型トランジスタには今回開発した一軸性引張りひずみSOIを用い、p型トランジスタには以前にMIRAIプロジェクトで開発した(昨年のIEDMで発表)一軸性圧縮ひずみSGOIを用いる。この一軸性圧縮ひずみマルチゲートSGOI p型トランジスタは、一軸性圧縮ひずみと、SiGeチャネル材料、および(110)面方位の全てが正孔の移動度増大に寄与するため、p型トランジスタにとっての理想的な構造であることが分かっている。本CMOS構造の作製には、これまでにMIRAIプロジェクトで開発した局所酸化濃縮法を用いることができる。すなわち、p型トランジスタ領域のみにSiGeを選択的に堆積し、高温酸化処理を行うことでひずみSGOI層を形成できる。

|

|

図6 一軸ひずみマルチゲートCMOSの最適構造 |

MIRAIプロジェクトでは、一軸性引っ張りひずみSOI n型、および一軸性圧縮ひずみp型SGOIトランジスタの性能をさらに向上させ、微細トランジスタの理論限界性能を追究するとともに、この2つのトランジスタを実際に集積することにより、CMOSの究極的な高性能動作の実証をめざす。