独立行政法人 産業技術総合研究所【理事長 吉川 弘之】(以下「産総研」という)次世代半導体研究センター【センター長 廣瀬 全孝】高橋 栄一 主任研究員、樋口 哲也 主幹研究員(兼 研究チーム長)は、書き換え可能なハードウェア(FPGA)を用いた高速なウイルスチェックシステムの開発に成功しました。

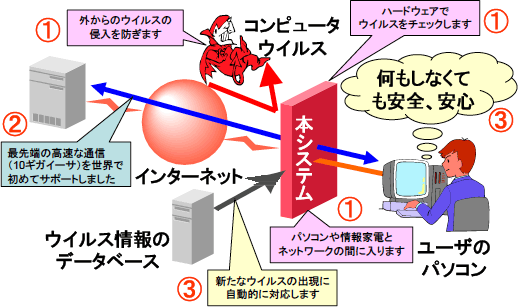

本システムは、3つの特長を持っています。(1)パソコンや情報家電とネットワークとの間に挿入して使います。これにより、パソコンや情報家電にコンピュータウイルスが侵入する前に除去することができます。(2)ハードウェアでウイルスをチェックします。これにより、ウイルスチェックが従来のものより10倍高速になります。(3)新たに出現したウイルスに対する対応は全て自動で行われます。これにより、ユーザによる操作不要でいつでも安心・安全なインターネット環境が実現できます。

今回開発したウイルスチェックシステムは、コンピュータのセキュリティ向上や情報家電などに対する新たなセキュリティ対策への貢献が期待されます。

本技術の詳細は、2006年11月28日(火)~30日(木)に北九州国際会議場で開催されるデザインガイアで発表されます。

職場で使うビジネス用パソコンはもちろんのこと、家庭における一般のパソコンでも常時接続が普通になってきました。こうした状況の中、コンピュータウイルスによる被害は増加の一途をたどっており、ビジネス用、家庭用を問わずパソコンにはウイルス対策ソフトをインストールして使うのが当たり前になっています。

ところが、ウイルス対策ソフトをインストールするとパソコンの動作が遅くなったり、ウェブの表示が遅くなったりします。それを理由にウイルス対策ソフトを使わないユーザもいるでしょう。また、ネットワークが速くなるに連れ、より多くのデータがネットワークを介してやりとりされるようになり、そうしたデータのウイルスチェックにより多くの時間がかかるようになってきました。加えて、ウイルス対策ソフトによるウイルスチェックでは、ネットワークから入ってきたデータを一旦パソコン内に取り込んでからウイルスが含まれているかどうかをチェックするため、チェックが済む前に感染してしまう可能性が残ります。

さらに、情報家電と呼ばれるようなネットワークにつないで使う家電製品については、こうしたウイルス対策ソフトをインストールして使うことはできず、何らかの対策が必要です。

そこで、こうした問題点に対する解決策の一つとして、本システムを提案し、研究開発を進めてきました。

産総研は、書き換え可能なハードウェアであるFPGAを用いたウイルスチェックシステムの開発に取り組んできました。これまで産総研では、セキュリティ技術に関する研究開発、組み込みシステムに関する研究開発、さらにFPGAを用いた動的再構成技術に関する研究開発などを行っており、セキュリティシステム分野においては世界的に見ても高いポテンシャルを持っています。

なお、本研究開発は、文部科学省の都市エリア産学官連携促進事業の一環として、株式会社つくば研究支援センターからの委託を受けて進めています。

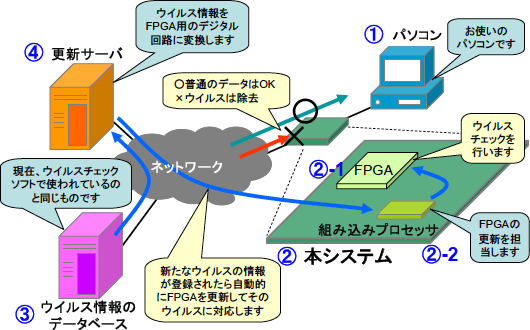

本研究で提案しているウイルスチェックシステムのコンセプトを図1に、具体的な構成を図2に示します。本システムの3つの特長は次の通りです。

(1) 現在、一般に用いられているウイルス対策ソフトウェアは、守るべき対象であるパソコン上でそのソフトウェアを動かしてウイルスの被害を防ぐ仕組みになっています。ユーザが使うパソコン上でウイルス対策ソフトウェアを動かしますので、背景で説明したような問題点が発生します。これに対して、本システムでは図1の1のようにパソコンとネットワークの間に挿入して使いますので、ユーザが使っているパソコンが遅くなることはありません。また、本システムはハードウェアでウイルスのチェックをしますので、ネットワークの通信が遅くなることもありません。さらに、送られてくるウイルスがユーザのパソコンに侵入する前に除去しますので、パソコンは全く安全です。

|

|

図1 本システムのコンセプト |

(2) 本システムでは、ハードウェアの高速性を活かして、現在、一般に普及しているネットワークの規格で最も高速な10ギガビットイーサネット(通信性能が最大10Gbps)の通信データをリアルタイムでチェックします(図1の2)。

(3) 一般にハードウェアは製造後に機能を変えることができませんので、ハードウェアでウイルスチェックを行った場合には、新種のウイルスに対応するにはシステム全部を交換する必要があります。しかし、本システムではいつでも機能を変えることができるFPGAというLSIを採用することで、新種のウイルスに対応します(図1の3)。

しかも、ウイルスの情報を集めたデータベースを監視して、新種のウイルス情報が登録されたら、それを元にFPGA用のデジタル回路を生成して、ウイルスチェックを行っているFPGAチップの機能を変更するまでを自動で行います。

提案した方法が正しく機能することを示すための実証システムを開発しました。その写真を図3に示します。

この実証システムを用いて、疑似ウイルスを含むデータのみを除去することと、ウイルス情報のデータベースの更新に合わせてFPGAの更新までが自動で行われることを確認しました。

本システムでは市販の高速なFPGAを使用しており、その上で機能するウイルスチェック回路は10Gbps以上の処理性能を持っていることを確認しています。これは、10ギガビットイーサネットを流れるデータをリアルタイムにチェックできる性能です。現在の実証システムは10ギガビットイーサネットを接続することができないため、実際の性能を測ることができませんが、産総研情報技術研究部門が開発済みのFPGA基板を使うことで10ギガビットイーサネットに接続することが可能になります。この基板への移行作業は平成18年度末の完了を予定しています。

|

|

図2 本システムの構成 |

|

|

図3 開発した実証システム (写真) |

平成19年度末まで、本システムの研究開発作業を進めて完成度を高め、3年から5年以内の実用化を目指します。本研究成果の実用化によって、パソコンやインターネットのセキュリティ向上に貢献し、今までは守る手段がなかった情報家電や携帯電話、電子手帳などの機器に対しても有効なセキュリティ対策として機能することが期待されます。