独立行政法人 産業技術総合研究所【理事長 吉川 弘之】(以下「産総研」という)次世代半導体研究センター【センター長 廣瀬 全孝】の 村川 正宏 研究員らは、半導体MIRAIプロジェクトにおいて、国立大学法人 広島大学【学長 牟田 泰三】(以下「広島大」という) 大学院先端物質科学研究科の 三浦 道子 教授と共同で、最先端半導体製造プロセスの開発で回路シミュレーションに用いる、次世代トランジスタモデル HiSIM(Hiroshima-university STARC IGFET Model)の、遺伝的アルゴリズムを応用した高精度自動合わせ込み技術の開発に成功した。

トランジスタモデルとは、回路シミュレーションにおいて、トランジスタの回路特性の予測に用いるモデルであり、LSI開発において最も重要で基本となる技術である。メモリーやSoC(System on a Chip)の設計開発用のライブラリやアナログ回路は全てこのトランジスタモデルを用いて設計されている。半導体デバイスは、現在、90nm(1ナノメートル:10億分の1メートル)プロセス時代を迎え、トランジスタモデルにおいても極微細トランジスタの動作記述が極めて複雑になり、従来のトランジスタモデルではモデルパラメータ数が約400個にも達している。このため実際のトランジスタの電気特性をモデルパラメータで合わせ込む作業に多大な時間が必要となり、設計技術者から新しいトランジスタモデルの出現が強く望まれていた。

広島大および株式会社半導体理工学研究センター【代表取締役社長 下東 勝博】(以下「STARC」という)が現在共同で開発を行っているトランジスタモデルHiSIMは、現行のスタンダードであるBSIM3とは異なって、表面ポテンシャルに基づいたトランジスタモデルである。HiSIMの特徴は、モデルパラメータの数が少ないこと(BSIM3のおよそ1/3)、SOI(Silicon On Insulator)など構造が複雑なトランジスタのモデル化も柔軟に対応できること、高周波領域でのシミュレーションが容易であること、などであり次世代のトランジスタモデルとして期待されている。

しかしながら、HiSIMによるシミュレーション結果が正確であるためには、複数のモデルパラメータを、あらかじめ計測したトランジスタの電気特性と一致するように調整する必要がある。この工程は「合わせ込み」と呼ばれ、合わせ込みが十分にできていないと計算精度が低下し、回路シミュレーションで正確な予測をすることができない。HiSIMはモデルパラメータの数が70個程度と、BSIM3と比較してかなり少ないが、原理的にすべてのモデルパラメータを一括して合わせ込むことが必要であり、従来のBSIM3における合わせ込みのノウハウが使えないことからも、合わせ込み工程の効率化がHiSIM普及の鍵を握っていた。

本研究開発では、人工知能の遺伝的アルゴリズムを応用することで、HiSIMの合わせ込み工程を、おおよそ数時間程度で自動化することに成功した。最先端製造プロセス(90nmルール)で試作したトランジスタの実測値(STARC提供)によりその有効性を検証した結果、本技術により合わせ込んだHiSIMのシミュレーション結果と実測値との誤差は平均で2.5%以内で一致した。これにより、極微細トランジスタの性能予測、回路シミュレーションが短時間で可能となり、HiSIMの普及が加速し、最先端半導体製造プロセスの開発コスト削減に貢献できると期待される。

今後は、産総研認定ベンチャー企業である 株式会社進化システム総合研究所【代表取締役社長 吉井 健】(以下「ERI」という)を通じ、実用化を進める予定である。なお本研究開発の技術的な詳細は、2005年1月18~21日の間、上海で開催される、Asia and South Pacific Design Automation Conference 2005 (ASP-DAC 05)で発表予定である。

○最先端の半導体製造プロセス開発の現状

最先端の半導体製造プロセスは年々微細化し、プロセス世代が進むごとに開発に長い期間と大きな投資が必要となっており、プロセス世代ごとに増大する開発コストを低減し、開発期間を短縮することは、半導体メーカーの解決すべき課題の1つとなっている。その解決策のひとつとして、半導体製造プロセス開発工程の初期段階で、現在ではTCADによるシミュレーション技術が駆使されている。また開発工程終盤では、トランジスタを設計、試作し(TEG)、そのTEGの性能評価を行い、試作を繰り返すことで目標のデバイス性能を獲得するという手法がとられている【図1(デバイス製造)参照】。デバイスの電気特性はトランジスタモデルで表現され、このトランジスタモデルを使用して、回路シミュレーションを行いその製造プロセス専用のライブラリ設計などが行われる。これらのシミュレーション技術により、ロット試作等に要する費用や工数を削減し、半導体製造プロセスの開発コスト低減を図ることが行われている。

○トランジスタモデルとは

トランジスタモデルとは、回路シミュレーションを用いて回路特性を予測する際に用いられるモデルであり、トランジスタ【図2参照】がどのような電気特性を示すかを、近似式で記述している。例えば、ドレイン電流とドレイン電圧の関係や、ドレイン電流とゲート電圧の関係などが、数式で表現される。集積回路は、このトランジスタが多数組み合わさって構成されており、集積回路を設計する際には、集積回路の構成要素となるライブラリやアナログ回路などがトランジスタモデルを使用して設計されている【図1(回路設計)参照】。またトランジスタモデルは、回路設計側からみると、デバイス製造側とのインターフェースとなっている。トランジスタモデルには複数のモデルパラメータが存在し、それぞれがトランジスタの物理的サイズ、基本特性値、物理現象の係数などを定める定数である。このモデルパラメータの数値が実際にデバイスを製造する工場などから提供され、そのパラメータ値を用いて回路設計が行われる。

|

|

MOSFET:3端子(入力端子、出力端子、制御端子)からなる素子

入力端子と出力端子間の電圧:ドレイン電圧

出力端子から出力される電流:ドレイン電流

制御端子に印加される電圧:ゲート電圧

ゲート電圧の大小で、ドレイン電流を制御できる |

|

図2 MOSFETの構造図

|

○従来のトランジスタモデルの問題点

しかしプロセスの極微細化に伴い、従来のトランジスタモデルでは、極微細トランジスタや複雑な構造をもつトランジスタのシミュレーション精度が不十分との指摘が多くなってきた。これは、現行のスタンダードモデルであるBSIM3では、ドリフト近似に基づいたトランジスタのモデル化を行っており、トランジスタの極微細化に伴い、それまで無視できていた物理現象の影響が大きくなり、この近似が正確でなくなるためである。その結果トランジスタ内の様々な現象を表現するためにモデル式がさらに複雑になり、BSIM3の次期バージョンであるBSIM4ではモデルパラメータの数が約400個になっている。

ここでこれらのモデルパラメータは、デバイス製造側から回路設計側に提供する必要があるが、TEGの物理的計測をすることで直接決められるモデルパラメータはごく一部であり、残りのほとんどのモデルパラメータは、計測したトランジスタの電気特性から間接的に推定しなくてはならない。この推定作業を、合わせ込み、もしくはパラメータ抽出と呼んでいる【トランジスタモデルの合わせ込み作業のイメージ参照】。従来モデルでは、モデルパラメータの数が膨大(約400個)であるために、この合わせ込み作業には熟練者でも1週間かかることもあった。この合わせ込み作業は、製造プロセスにおける工程変更、トランジスタの構造変更、製造条件の変更などのたびに必要であることから、合わせ込みに要する工数が増加し、タイムリーで高精度なシミュレーションに多大の労力がかかるという問題が生じている。これは開発コストの増大につながることから重要な問題となっている。多数のモデルパラメータを合わせ込むためにモデルパラメータ群をいくつかのグループに分割し、グループごとにモデルパラメータを合わせ込み、それらモデルパラメータを統合した後に全体を再度合わせ込む、などの工夫が行われているものの、それらの理論的な分割方法は確立されておらず、熟練者が持つノウハウや職人技に頼っているところが大きいのが実状である。

|

●トランジスタモデルの合わせ込み作業のイメージ

合わせ込み作業のイメージを、図Aを例に説明する。ここでは、加速中の飛行機の速度をモデル化するという例を考える。上空を航行中の飛行機の速度を何秒おきかに計測しそれをプロットする。プロット結果から、この飛行機が等加速度で航行しているとモデル化する。このモデルは時間と速度の関係が図Aに示すような数式(直線)で表現でき、二つの定数(初速度V0、加速度a)が存在する。この定数がモデルパラメータである。そこでこのモデルパラメータを調整して、モデル式(直線)と計測した速度(複数点)がなるべく一致するようにする。この調整が合わせ込み作業である。ひとたびこの合わせ込み作業が完了すれば、未来の時刻(t=tf)における速度(V=Vf)を予測することが可能になる。この例とトランジスタモデルの合わせ込みのアナロジーは、飛行機の速度⇔トランジスタの電気特性、速度の計測⇔TEG計測、モデル式(直線)⇔BSIMやHiSIM、二つの定数⇔多数のモデルパラメータ、未来の速度予測⇔回路シミュレーション、となる。 |

|

|

|

図A モデルの合わせ込み作業のイメージ:飛行機の速度のモデル化を例に

|

○次世代トランジスタモデルHiSIM

これらの問題を解決するために、広島大およびSTARCでは、次世代トランジスタモデルとしてHiSIMの共同開発を進めている。HiSIMでは、表面ポテンシャルに基づいたMOSFETのモデル化を行いトランジスタの物理原理を可能な限り忠実に解析した結果、全体としてはモデル記述がかえって簡単になり、モデルパラメータの数が70個程度にまで削減された。また、SOIなど構造が複雑なトランジスタのモデル化も柔軟に対応でき、高周波領域での特性シミュレーションが容易であるなどの特徴がある。しかしながら、HiSIMの合わせ込み工程においては、原理的にすべてのモデルパラメータを一括して合わせ込むことが必要であり、従来モデルの合わせ込みにおけるノウハウを活用することができなかった。この理由としては、HiSIMのモデルパラメータは、大別すると、表面ポテンシャルを決定するのに必要なパラメータ群と、物理量を決定するのに必要なパラメータ群に分けられ、これらふたつのパラメータ群は、相互に依存して電気特性に影響を及ぼすので、独立に合わせ込むことができないことによる。そのため、HiSIMが次世代のトランジスタモデルとして普及するためには、合わせ込み工程の自動化、高精度化がひとつの鍵であるといわれていた。

産総研では、平成13年度から遺伝的アルゴリズムを用いた合わせ込み技術の基礎研究を行っており、この研究成果をもとに、平成14年度から半導体MIRAIプロジェクトと株式会社半導体先端テクノロジーズ【代表取締役社長 森野 明彦】(以下「Selete」という)が、共同でイオン打ち込みモデルにおける自動合わせ込み技術の研究開発を行い、144個のモデルパラメータを数分程度で自動的に合わせ込むことに成功している。この研究開発成果は、ERIがソフトウェア化し、Seleteの3次元TCADシステム「ENEXSS」に搭載され、すでに実用に供されている。

一方、HiSIMの研究開発は広島大とSTARCにより、平成10年にプロジェクトが開始され、平成12年にHiSIM :Hiroshima-university STARC IGFET Modelと正式に命名された。平成14年1月には、Webによる一般公開が行われ、平成14年春からは、高周波デバイス用HiSIM2の開発を行う新たなプロジェクトが始まっている。

平成16年度より、HiSIMの高精度自動合わせ込みを目標とする、産総研と広島大の共同研究が半導体MIRAIプロジェクトの一環として開始された。STARCに最先端プロセスで試作したトランジスタ実測値の提供を受け、本技術の有効性を検証している。

産総研と広島大が開発したHiSIMの自動合わせ込み技術では、人手によるパラメータ群の分割統合作業を行わずに、人工知能の遺伝的アルゴリズムを応用し、多数のパラメータを一括して自動的に合わせ込む【図3参照】。遺伝的アルゴリズムには、最適解を求める探索の過程において探索が局所最適解に陥りにくいという特徴があり、多数のパラメータを効率良く最適化できる。

遺伝的アルゴリズムにおいては、HiSIMの複数のモデルパラメータをすべて連結し、01のビット列で表現する。そしてそれをあたかもひとつの染色体のようにみなす【図4(手順1)参照】。その染色体を複数個ランダムに用意して、その染色体が示すモデルパラメータ値を用いて実際にHiSIMによりトランジスタ特性をシミュレーションする。シミュレーション結果の特性値と実測値とを比較して、誤差が小さい染色体ほど適応度が大きくなるように定める【図4(手順2)参照】。そして、比較的適応度が高かった染色体をかけあわせ(交叉、突然変異)、新たな染色体を作成し適応度を求める。つぎに、最もパワー値の低い染色体が淘汰され、新たな染色体が探索点に加わる【図4(手順3)参照】。この一連の適応度評価、かけあわせ、淘汰を「世代」とよび、世代を繰り返すことにより徐々に適応度の高い染色体が(つまり実測値との誤差が小さくなるモデルパラメータ値が一括して)発見される。

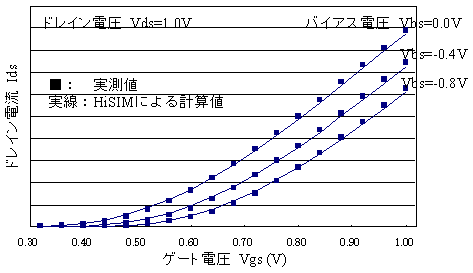

実験では、HiSIMの主要なモデルパラメータ32個*を、トランジスタの電流特性値群に一致するように合わせ込みを行った。この電流特性値は、90nmルールで試作したトランジスタにおける実測値(トランジスタの寸法が異なるものを8種類:チャンネル長が100nm~10µm(1マイクロメートル:100万分の1メートル)、チャンネル幅は2µm)を、STARCより提供を受けたものである。この実測値と、HiSIMのシミュレーション値との誤差が0の状態が理想的であり、なるべく誤差が小さくなるようにパラメータ値を調整する。実験の結果、実測値とHiSIMによるシミュレーション値を比較すると、チャンネル長が100nmのトランジスタのドレイン電流-ドレイン電圧特性【図5参照】、チャンネル長が100nmのトランジスタのドレイン電流-ゲート電圧特性【図6参照】とも、非常によくパラメータが合わせ込まれていることがわかる。チャンネル長100nmを含む8種類すべてのトランジスタサイズにおいて、電流特性はRMS誤差2.5%以下で一致した【表1参照】。これにより、各種のトランジスタサイズのMOSFETを使用して設計する複雑なシステムLSIに対しても、正確な回路シミュレーションが可能となる。合わせ込みに要した時間は、1台のPCを使用しておよそ23時間程度、8台のPCを使用したPCクラスタではおよそ3時間程度であったことから、従来熟練者でも数日から1週間程度かかっていた合わせ込み工数を、大幅に短縮、自動化することができる。

|

|

|

図5 Lg(チャンネル長)0.10µm、Wg(チャンネル幅)2.0µmのMOSFETにおけるドレイン電流-ドレイン電圧特性の合わせ込み結果

|

|

|

図6 Lg(チャンネル長)0.10µm、Wg(チャンネル幅)2.0µmのMOSFETにおけるドレイン電流-ゲート電圧特性の合わせ込み結果

|

|

チャンネル長(µm)

|

RMS(%)

|

|

0.10

|

1.40

|

|

0.11

|

1.23

|

|

0.13

|

2.04

|

|

0.20

|

2.24

|

|

0.30

|

2.33

|

|

1.00

|

2.21

|

|

5.00

|

1.22

|

|

10.0

|

1.52

|

表1 各チャンネル長における合わせ込み誤差

今後は、より多くの実測データでの合わせ込み実験を重ね、HiSIMの自動合わせ込み技術の信頼性を検証するとともに、産総研認定ベンチャー企業であるERIを通じて事業化を進める予定である。さらに、高周波領域での高精度の合わせ込み実験を行い、HiSIMの自動合わせ込み技術のさらなる有効性を検証する予定である。

また次世代トランジスタモデルに関しては、標準化を推進する民間組織CMC(Compact Model Council)において、現在標準化活動が行われている。HiSIMは、アジアからの唯一の標準モデル候補として現在検討されており、本研究開発成果がHiSIMの標準化を推進することが期待される。