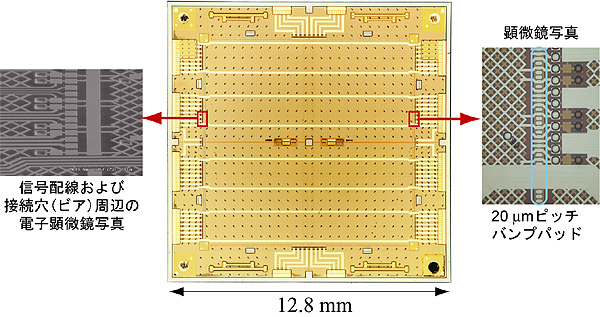

独立行政法人 産業技術総合研究所【理事長 吉川 弘之】(以下「産総研」という)エレクトロニクス研究部門【部門長 伊藤 順司】高密度SIグループ【グループ長 青柳 昌宏】は、技術研究組合 超先端電子技術開発機構【理事長 佐々木 元】(以下「ASET」という)と共同で、超高速伝送・超高密度実装を実現するLSIチップ接続用高密度微細配線インターポーザの開発に成功した(図1参照)。

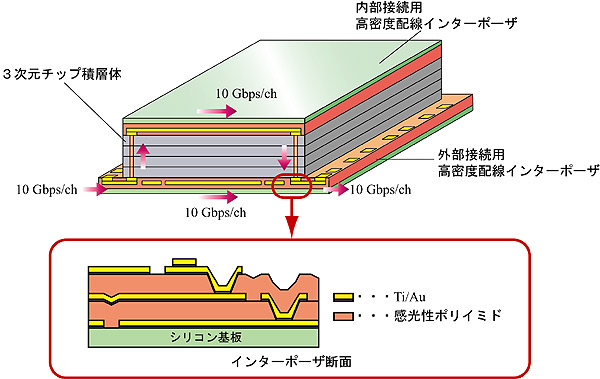

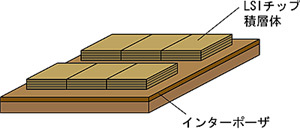

LSIチップの性能は、CPUチップのクロック周波数が3GHzを越えてきているように、年々飛躍的に進歩を遂げてきている。しかし、CPUチップからメモリ等への外部バスの信号伝送クロック周波数は500MHz程度であり、CPUチップの速度と数倍から数十倍の開きがあるため、増大する情報量に対して、システム全体の速度上昇が頭打ちとなっている。このためLSIチップ間接続に用いる伝送クロック周波数もLSIチップのクロック周波数と同程度の性能が求められていた。この要求に応える技術として、複数のLSIチップを接続してあたかもひとつのLSIチップであるように動作させる高密度システム集積技術(システムインパッケージ:SiP)があるが、本研究開発では、LSIチップを立体的に重ね合わせて接続するための高密度微細配線インターポーザの開発に世界で初めて成功した。(図2参照)。

今回開発した高密度微細配線インターポーザは、光電気高速伝送モジュールに適した10Gbpsの伝送速度と既存周辺デバイスとの整合性を図ることが可能な50Ω特性インピーダンスを有する高性能信号配線構造(ストリップライン構造)をもつ。この実現のため、金属配線間の絶縁層に低誘電率有機絶縁材料である感光性ポリイミド(比誘電率3)を使用した。このため従来のプリント基板技術を用いた最小線幅50µm(1マイクロメートル:10-6メートル)程度の配線から、最小線幅7.5µmの配線への微細化が実現した。LSIチップとの接続に関しては、20µmピッチの微細バンプを用いて、LSIチップ直接接続(フリップチップ接続)形成工程に対応した設計となっている。また、高密度微細配線インターポーザの作製プロセスにおいては、高解像感光性ポリイミド絶縁層の利用により、微細な層間配線接続(ビア接続)に必要な配線間接続穴(ビアホール)形成を光転写技術(リソグラフィ)工程のみで実現し、大幅な工程の簡略化を実現している。これにより、実用化の際に製造プロセスの低コスト化が可能である。

本研究成果の詳細は、2003年9月16~18日に東京(京王プラザホテル)において開催される“2003年国際固体素子・材料コンファレンス(SSDM2003)”において発表する予定である。

本研究は、新エネルギー産業技術総合開発機構(NEDO)【理事長 牧野 力】(以下「NEDO」という)の次世代半導体デバイスプロセス等基盤技術プログラム「超高密度電子システムインテグレーション(SI)技術」の一環として、実施された。

また、本研究に関連した特許を3件出願中である。

|

|

|

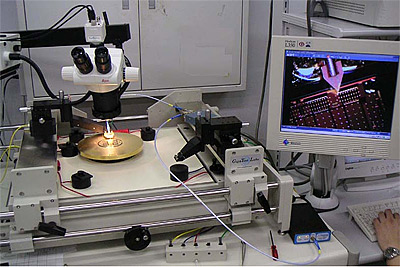

図1 開発した高密度配線インターポーザの写真

|

|

|

図2 高密度配線インターポーザ断面図

|

IT革命の中心にあるPCの性能は、CPUチップのクロック周波数が3GHzを越えてきているように、年々飛躍的に進歩を遂げてきている。しかし、CPUチップからメモリ等への外部バスの信号伝送クロック周波数は500MHz程度であり、CPUチップの速度と数倍から数十倍の開きがあるため、増大する情報量に対して、システム全体の速度上昇が頭打ちとなっている。このためLSIチップ間接続に用いる伝送クロックもLSIチップのクロックと同程度の性能が必要になってきている。また、近年のユビキタス情報社会の実現に向けた情報携帯端末等の小型電子機器に対する高機能化の要求も高まる一方であり、その要求に答えるためには高性能かつ高密度システム集積技術の確立が急務となってきている。

これらの問題に対して、世界中で様々な企業、大学、研究機関などが技術開発への取り組みを強化しており、日本でも企業、大学、学会(特にエレクトロニクス実装学会)を中心にして、研究技術開発が活発化してきているところである。

平成11年度からスタートしたNEDOの次世代半導体デバイスプロセス等基盤技術プログラム「超高密度電子システムインテグレーション(SI)技術」において、3次元LSIチップ積層実装技術、光・電気複合実装技術、最適配線設計技術の3テーマについて、ASETと産総研が連携共同研究体を組織して、電子実装分野の研究開発を進めてきている。特に、3次元LSIチップ積層実装技術に関しては、ASETと産総研の緊密な連携により実験設備、機材の相互利用、共同実験、情報交換などを通じて、具体的成果を着実に上げてきたところである。

また、産総研では、同時に民間企業(主として、中小企業)との共同研究により、感光性ポリイミド材料による絶縁層形成、同軸配線プリント基板、高周波誘電特性測定評価、電磁界解析手法による線路設計、高周波微細プローブなどの基礎技術の開発を進めてきた。

なお、高密度微細配線インターポーザの設計については、ASET筑波研究センターと共同で行い、感光性ポリイミド絶縁材料については、3年前より共同研究を実施しているピーアイ技術研究所【代表取締役社長 早川 博】から提供されたブロック共重合ポリイミド材料を用いた。

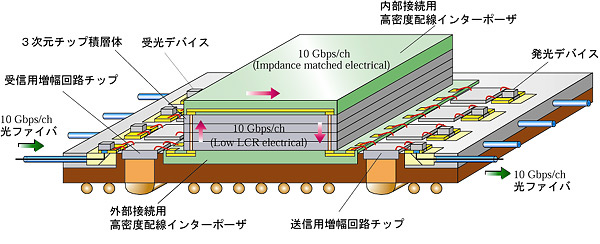

本研究は、3次元LSIチップ積層実装技術と光・電気複合実装技術の成果を統合した光電気複合実装3次元モジュールの開発の一環として、進められた(図3参照)。開発した高密度配線インターポーザは、3次元チップ積層構造と光電気高速伝送モジュールを電気的に接続するための重要パーツであり、既存の技術であるセラミックス基板技術やガラス、エポキシ系のプリント回路基板技術では、誘電率が高いことや基板表面の粗さの問題などがあり、実現が困難な非常に高度な仕様となっている。例えば、配線幅7.5µmは、どちらの技術でも達成不可能である。

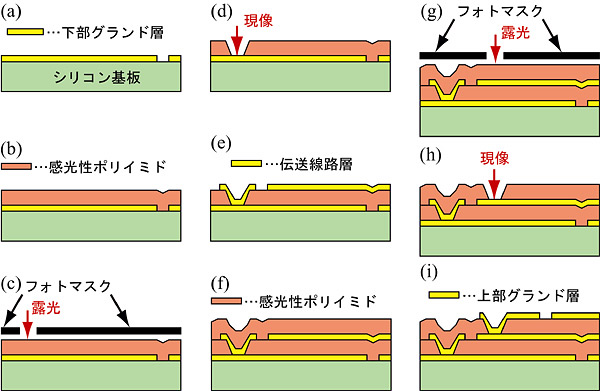

高密度配線インターポーザの作製は、3層金属配線層のストリップライン線路構造を実現するため、低誘電率を特長とする感光性ポリイミド絶縁層のスピン塗布形成、紫外線を用いたリソグラフィ工程によるビアホール形成、真空蒸着法とリフトオフプロセスによる微細金属(Au)配線形成など一連のプロセスを繰り返して実施することにより、達成された。特に、ポリイミドとAuとの密着力が弱いため、別の金属層を導入して、密着力の改善を行った。感光性ポリイミドを多層化する際に下の層から溶媒が蒸発して、気泡を形成されるのを防ぐため、下層の熱処理乾燥プロセスの最適化を行った。また、ポリイミド上のリフトオフ用感光性レジストについて、露光条件の最適化を行った。

作製プロセスの開発では、感光性ポリイミドの露光特性最適化、感光性ポリイミド絶縁層の多層化、微細金属配線形成などを新規に研究を進め、高密度配線インターポーザの試作に成功した。作製プロセスの特徴は、高い解像度をもつ感光性ポリイミド絶縁層の利用により、微細ビア接続に必要なビアホール形成をリソグラフィ工程のみで実現した。つまり感光性ポリイミドを塗布し、エッチング工程無しのリソグラフィ工程のみで絶縁層が形成できるため、大幅な作製プロセスの簡略化を実現している。これにより、実用化の際に作製コストの低減が可能である。なお、高密度微細配線インターポーザ作製プロセスの開発は、感光性ポリイミドの最適化、感光性ポリイミド絶縁層の多層化、金属配線の微細化などの要素技術について、基礎検討を進め、最終的に作製プロセス全体としての最適化を図った(図4参照)。

本高密度微細配線インターポーザの特徴は、50Ω特性インピーダンスを有する信号配線を有しており、線幅7.5µmから17.5µmまでの微細配線を実現している。さらに、LSIデバイスとの接続に関しては、20µmの微細バンプを用いて、プロセス温度250℃のフリップチップ接合形成プロセスに対応した設計とした。微細バンプ接続によるチップ積層実験は、10月以降に予定している。

特性の評価は、超高速な時間領域における信号反射率を測定する技術(TDR計測技術)により信号配線の特性インピーダンスを評価した。測定評価の結果、微細配線について、50Ωの特性インピーダンスと10Gbpsの信号伝送に対応していることを確認した(図5参照)。ベクトルネットワークアナライザによるSパラメータ評価も併せて実施しているところである。

|

|

|

図3 光電気複合実装3次元モジュールの概念図

|

|

|

図4 作製プロセス

|

|

|

図5 電気特性評価実験の様子

|

今回開発した高密度微細配線インターポーザ技術は、高密度配線形成技術として幅広く適用できる基本的技術なので、本技術に関心のある民間企業、大学などとの連携共同開発により、高性能コンピュータ、携帯電子機器、知能ロボット、情報家電などへの実用レベルの応用技術開発を進めていく予定である(図6参照)。

|

|

|

図6 高密度微細配線インターポーザを用いた高密度システム集積応用イメージ

|