独立行政法人 産業技術総合研究所【理事長 吉川 弘之】(以下「産総研」という)エレクトロニクス研究部門【部門長 伊藤 順司】は、従来のCMOS作製技術に、新開発のイオン照射減速エッチング(特許出願済)プロセスを付加することにより、ナノスケールでの優れた加工性能を得て、スケーリングが容易で、かつ、超低消費電力化を可能にする新しい縦型ダブルゲートMOSFET(その断面形状から「IMOSFET」とも呼ぶ)の開発に成功し、同時に優れた素子特性を実証した。

○究極のMOSFETの実用化に向けて大きく前進

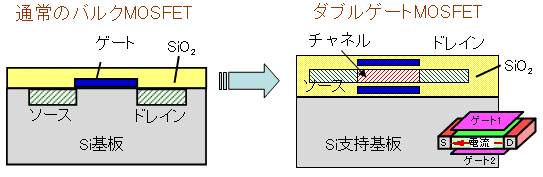

現在の情報通信機器のハードウェアを支えるSi型ULSI(シリコン型超大規模集積回路)による高機能・高集積化は、MOSFETの微細化により驚異的な発展を遂げてきた。しかしながら、更なる微細化および低消費電力化の観点から見ると、今後、大きな障害に直面することが予想されている。微細化への最も大きな障壁は、ソースとドレインの距離の短縮に伴って、互いが干渉して起こる短チャネル効果によるデバイス特性の劣化であり、この事が微細化限界を決めている。この困難を打破するデバイス構造として、薄いチャネル層を二つのゲートで挟み込むダブルゲートMOSFETが究極の構造と認知されているが、ダブルゲート構造の作製が困難なため、現在に至るもまだ実用化されていない。

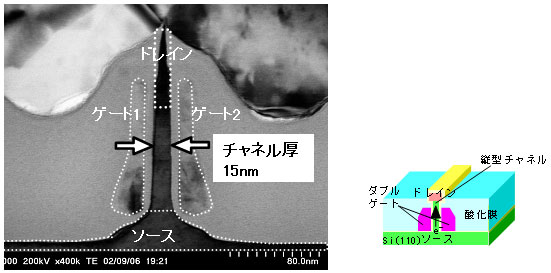

今回、産総研で開発した縦型ダブルゲートMOSFET(IMOSFET)は、市販のバルクSi基板を使用しており、従来のCMOS作製技術に加え、イオン照射部分のアルカリ水溶液に対する著しい減速エッチング特性を利用したことで作製を可能としたものである。この新開発のプロセスを用いて、チャネル厚15nmの世界最薄の縦型ダブルゲートMOSFET(IMOSFET)の試作と動作実証に成功した。実測した素子特性は、理論予測と合致する優れた特性を示している。本技術開発は、究極のMOSFETと言われるダブルゲートMOSFETの実用化への道を拓いた成果と言える。なお、ダブルゲートMOSFETは、二つのゲートを持つことによりダイナミックにしきい値電圧を制御できるので、超低消費電力ULSIを実現する可能性も有している。

○イオン照射減速エッチングプロセスを新たに開発

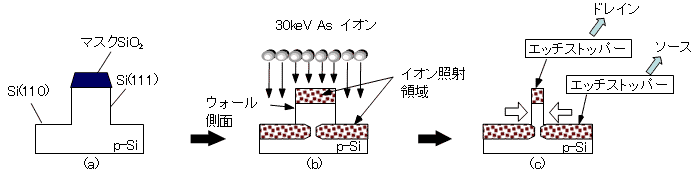

技術的ブレークスルーとしては、縦方向チャネルとなる極薄のSiウォール(壁)の作製に、新たに開発したイオン照射減速エッチングを用いたことである。イオン照射部分に対して、市販のアルカリ現像液によるエッチングの速度が著しく減速することを利用し、その部分をエッチングマスクとして用いることによって、バルクSi基板上にナノメートルスケールのSiウォールを形成することに成功した。この方法は、プロセスの再現性に優れており実用性が極めて高いものである。

○優れた素子特性を確認

今回、実際に15nmチャネル厚の世界最薄縦型ダブルゲートMOSFET(IMOSFET)の試作に成功しただけでなく、素子特性も詳細に測定した。測定結果は、MOSFETの重要な特性指標であるサブスレッショールド特性(S-スロープ)がチャネルの厚さを減少させるにつれて向上することを明瞭に示した。これは、スケーリングによる素子寸法の更なる微小化に対しても特性が劣化せず、むしろ向上することを示しており、将来の超高集積LSIの実現に大きく前進する成果である。

本成果によって、バルクSi基板を使用した微細縦型ダブルゲートMOSFET(IMOSFET)の基本作製技術は確立された。今後は、プロセスの最適化によってデバイス特性の向上を目指すと共に、超低消費電力化および多機能化をも実現するダブルゲートMOS技術の確立を図っていく予定である。

なお、本成果は2002.12.9-11に米国サンフランシスコで開催される国際電子デバイス会議(2002IEDM: 2002 IEEE International Electron Devices Meeting)で、2002.12.10に発表する予定。

情報通信社会を支えるSi型 ULSIは、そこに用いられるMOSFETの微細化によって驚異的な発展を遂げてきた。しかしながら、Si型 ULSIの将来には、大きな障害が立ちはだかっている。すなわち、更なる微細化を進める場合、出力側となるドレインの影響が入力側であるソースに及ぶようになり、第3の端子であるゲートからの制御を基本としたMOSFETの電気的特性が著しく劣化してくることである。これは短チャネル効果と呼ばれ、MOSFETの微細化限界を決める最大の要因となる【図1左】。短チャネル効果が顕在化すると、基板を介したソース・ドレイン間のリーク電流が増大し、待機時の消費電力の増大も深刻になり集積化限界を招いてしまう。

これらを克服するデバイスとしては、薄いチャネル層を二つのゲートで挟み込んでドレインからソースへの干渉を断ち切った、ダブルゲートMOSFET【図1右】が最も有効であるとITRSロードマップ(2001)により認知されている。ダブルゲートMOSFETは、1984年に旧工業技術院電子技術総合研究所(現産総研)から提案されたものである(世界で最初の出版物が1984年であり、日本国特許出願は1980、1983年:XMOSと命名した)。

XMOSデバイスは、最も微細化に適したデバイス構造であるばかりでなく、ゲートを二つ持つ、いわば4端子デバイスとしての高い機能性をも有している。その最も端的な機能が、一方のゲートにより、ダイナミックにしきい値電圧を制御することによって超低消費電力LSIを実現できることである。すなわち、今後のSi 型ULSIの発展に立ちはだかる消費電力の爆発を回避できるデバイス構造であり、究極のMOSFETと称する所以である。ただ、弱点はダブルゲートを含めた作製技術であり、現在に至るもまだ実用化されていない。

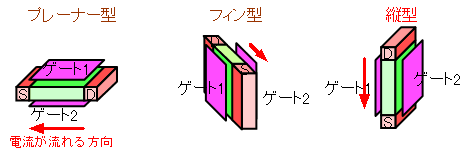

ダブルゲートMOSFETの形態は、プレーナー型、フィン型、縦型の3つのタイプがある【図2】。何れのタイプにおいても作製技術の困難さから、提案後あまり注目されなかった。しかし、近年、最も権威ある電子デバイス国際会議であるIEDMで、2001年10件、2002年9件と多数の発表が行われるようになり、最も進化したMOSデバイスとして急激に脚光を浴びている。

今回、産総研で開発した微細縦型ダブルゲートMOSFET(IMOSFET)は、バルクSi基板を使用し、新開発のイオン照射減速エッチングプロセスを用いて作製したもので【図3】、リソグラフィーよりも微細な極薄Siウォールチャネルを形成できる【図4】。15nmチャネル厚の世界最薄縦型ダブルゲート試作デバイスは優れた短チャネル素子特性を示し、究極のMOSFETと言われるダブルゲートMOSFET の実用化への道を拓いた成果と言える。

|

|

図1 通常のバルクMOSFETとダブルゲートMOSFETとの比較

|

|

|

図2 ダブルゲートMOSFETの三つのタイプ

今回開発したものは3番目の縦型ダブルゲートMOSFET(IMOSFET)

|

|

|

図3 イオン照射減速エッチングによる微細Siウォールの作製フロー

|

(a)SiO2マスクを用いた縦方向エッチングによるやや厚いSiウォールの形成

(b)SiO2マスクを除去後砒素(As)イオン注入

(c)イオン照射減速エッチングによる極薄Siウォールチャネルの形成

|

|

|

|

図4 試作したチャネル厚15nmの縦型ダブルゲートMOSFET(IMOSFET)の断面TEM写真

|

(1) 新規イオン照射減速エッチングプロセスによる微細縦型ダブルゲート作製技術の開発

Siの加工技術には、Siの結晶面に依存して異なるエッチング速度を持つことを利用した異方性ウェットエッチングの方法がある。通常は、(100)面、(110)面、(111)面の順にエッチング速度は遅くなるが、イオン照射を行った部分は、極端にエッチング速度が減速されることを新たに見いだした。この現象を利用して、今回の微細縦型ダブルゲート作製技術を開発した。実際に用いたエッチング溶液は、市販のアルカリ現像液である2.38% TMAH (

tetramethylammonium hydroxide) 溶液で、まず、(110)Si基板上にSiO

2マスクにより厚いSiウォールを形成する【図3(a) 】。(110)Si基板を用いるのは、TMAH溶液の異方性エッチングによって、SiO

2マスクにそって、エッチング速度の遅い(111)面からなるSiウォールを作るためである。次に、30 KeVの砒素(As)イオンを注入すると、厚いSiウォールの頂上部とウォール周辺の下地のSi部分だけ照射され、Siウォールの側壁は照射されない【図3(b) 】。従って、もう一度TMAH溶液でエッチングを施すと、イオン照射部分はエッチストッパとして働くため、Siウォールの側壁だけがゆっくりとエッチングされ、縦方向チャネルとなるSi ウォールを精度良く極薄化することができる【図3(c) 】。実際にこの方法を用いた、極薄Siウォールチャネル縦型ダブルゲートMOSFET(IMOSFET)の作製プロセスを開発した。

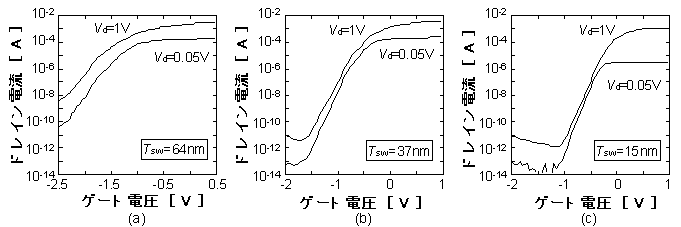

(2)ダブルゲートMOSFETに期待される優れた短チャネル素子特性を検証

ダブルゲートMOSFETの大きな特徴は、チャネルをはさんで両側のダブルゲートによりドレイン電界をシールドするため、短チャネル効果を最も有効に抑止できることにある。チャネル層がSiバルクと繋がっている通常のバルクMOSFETとダブルゲートMOSFETの中間の構造として、SOI(

Silicon on Insulator) MOSFETがある。SOI層を薄膜化して深さ方向の電流パスを遮断すれば、短チャネル効果抑制に一定の効果はあるものの、下地のSiO

2層を介してのドレイン電界のソースへの影響は免れず、短チャネル効果抑止に限界がある。それ故に、ダブルゲートMOSFETが微細化限界を克服するデバイス構造として期待されているのである。【図5】は、試作した微細縦型ダブルゲートMOSFET(IMOSFET)のSiウォールチャネル厚をパラメータとした静特性(ドレイン電流-ゲート電圧特性)を示している。注目すべき点は、ドレイン電流のゲート電圧に対する立ち上がり部分であるサブスレッショールド領域の特性である。Siチャネル厚が薄いほど、立ち上がりが急峻であり、かつ、ゲートしきい値電圧V

thの負側へのシフト(ロールオフ特性と呼ばれる)が有効に押さえられていることがわかる(この場合の理論値は-0.35V)。ドレイン電流立ち上がりのなまりや、V

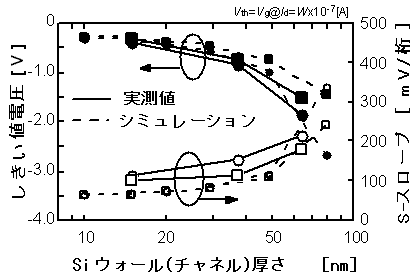

thロールオフは、代表的な短チャネル効果であるが、Siチャネル厚を薄くすることによって、ダブルゲートMOSFETの優位性である短チャネル効果抑止を実験的に明らかにした。今回の縦型ダブルゲートデバイスでは、通常のMOSFETのチャネル幅に相当するものはSiウォール長になる。したがって、極薄Siウォールチャネルをn本平行に設けることによって、同じウエハ面積に対して、通常のMOSFETの2n倍もの電流を流すことができ、必要に応じて大きな回路駆動能力を持たせることができる利点もある。【図6】は、しきい値電圧Vthと電流立ち上がり性能であるS-スロープの、Siウォール厚さ依存性を示している。試作デバイスによる実験値とシミュレーション結果は良く一致しており、Siチャネル厚を20nm程度以下に薄くすれば、十分に短チャネル効果が抑止され、ダブルゲートMOSFETの特徴が発揮できることを示している。

|

|

図5 試作した縦型ダブルゲートMOSFET(IMOSFET)のドレイン電流-ゲート電圧特性

Siウォール(チャネル)厚Tswをパラメータにしている

(a)Tsw=64nm、 (b) Tsw=37nm、 (c) Tsw=15nm

Tswが薄いほど短チャネル効果が抑止されている

|

|

|

図6 縦型ダブルゲートMOSFET(IMOSFET)の、しきい値電圧、S-スロープのSiチャネル厚さ依存性

[ ○ ] および [ □ ] は、ドレイン電流の飽和モードと線形モードでの値を示している

しきい値電圧は負に大きくなるほど、S-スロープは大きくなるほど短チャネル効果が顕著であることを意味する

Siウォール(チャネル)厚を20nm程度以下に薄くすれば、十分に短チャネル効果が抑止されることを示している

|

ダブルゲートMOSデバイスは、1984年の旧工業技術院電子技術総合研究所(現産総研)からの提案後、その作製技術の困難さ故に長い間注目されてこなかったが、1997-8年頃から加速的に関心を集めている。その関心は米国においてことに強く、中でもIBMは「SOIの次はダブルゲート」との見通しを1998年に発表して以来、ダブルゲートMOSデバイス研究を戦略的に行っている。プレーナー型ダブルゲートMOSFETで初歩的な回路動作(インバータ)を2001年に発表、2006年には製品導入を目指す(フィン型FETとの情報がある)とアナウンスしているがデバイス技術はまだ確定していない。

一方、1998年に(株)日立製作所との共同研究でフィン型FETを発表したカリフォルニア大学バークレー校は、継続的に研究を続けており、企業との連携を積極的に進めている。最近のAMDとのフィン型FETの共同研究もその例である。Intelは昨年、将来デバイスとして薄膜SOI MOSFET(DSTと呼んでいる)をアナウンスしたが、一転して本年、フィン型FETよりも薄膜化の必要がないとしてTri-ゲートFETを将来デバイスとアナウンスしている。しかし、電流は3倍になるものの、極微細化しない限りダブルゲートMOSデバイスの短チャネル効果抑止特性は失われる。Bell Lab.は縦型FETの研究を進めているが、微細化には成功していない。米国のいくつかの大学ではダブルゲートMOSデバイスの基礎研究をシミュレーション主体で行っている。欧州では、フランスのIMEPが研究課題を挙げている。

一方、国内では、(株)日立製作所が、1989年に発表したDELTAをフィン型FETの原型と主張しているが、本格的に集積回路技術開発に取りかかってはいない。富士通(株)では、1988年にSGT、1991-94年にかけてプレーナー型のダブルゲートMOSの研究が行われていたが、現在は行われていない。

以上、最も微細化に適したデバイスとしてITRSロードマップも認めているダブルゲートMOSデバイスへの関心は、フィン型FETを中心としてことに米国で急速に高まっている状況にある。しかし、フィン型FETには、フィン構造の横方向に電流を流すことになるので流せる電流量が大きな制約を受けるというネックがあり、すなわち、ダブルゲートMOSデバイス技術はまだ確立されていないといえる。

(1)イオン照射減速エッチング技術により、ダメージフリーで極薄のSiウォールチャネルを形成できる

(2)リソグラフィーよりも微細な厚さのSiウォールチャネルを形成できる

(3)ゲート長がSiウォールの高さの制御により行えるので数nmまでのスケーリングが容易

(4)大電流を流すことが可能

(5)High-Kゲート絶縁膜材料の導入が容易に可能

他のデバイスにはない、上記のような優位性を最大限に生かすため、配線を含めた超低消費電力集積化技術および多機能化技術の開発が今後の課題である。

本成果によって、バルクSi基板を使用した微細縦型ダブルゲートMOSFET(IMOSFET)の基本作製技術は確立された。今後は、プロセスの最適化によってデバイス特性の向上を目指すと共に、今回のnチャネルに加えて、詳細な不純物拡散制御を必要とするpチャネルデバイスの作製技術の開発を進め、ダブルゲートCMOS集積化技術の確立を図っていく。さらに、ダブルゲートMOSFETの持つ4端子素子としての特徴を最大限に生かす超低消費電力LSI技術の構築を目指す。