独立行政法人 産業技術総合研究所【理事長 吉川 弘之】(以下「産総研」という)エレクトロニクス研究部門【部門長 伊藤 順司】は、単結晶電極を持つ新型高性能TMR素子をシリコンLSIチップ上に作製する手法を世界で初めて開発した。

開発した新技術は、TMR素子の強磁性電極の厚さを非常に薄くナノメートルサイズにすると、量子サイズ効果により信号強度の増大と磁気特性の向上が計れるというもので、ポストDRAMとして期待されている不揮発性メモリ( MRAM )の大容量化の課題解消に繋がると期待される。

単結晶強磁性電極(Fe(001))の厚さが1nm付近で最大のTMR比を示すという新現象を発見し、これを可能にした薄膜作製技術の有効性を実証した。具体的には、TMR素子の電極を単結晶化することで結晶粒を無くし、電極表面を原子レベルで平滑にするためにMgO下地層を用い、任意の基板の上に高配向・超平滑な電極層を作製する手法を開発した。

○量子サイズ効果を用いてTMR素子の信号強度(TMR比)の向上に成功

産総研では、単結晶薄膜作製技術を用いて非常に平滑で薄い(厚さ2nm以下)単結晶の強磁性電極を持つTMR素子を作製し、量子サイズ効果によってTMR比が増大することを世界で初めて実証した。

○単結晶電極を用いて電極の超平滑化に成功。

産総研では、TMR素子の電極を単結晶化することによって結晶粒を無くし、電極表面を原子レベルで平滑にすることに成功した。

○高性能TMR素子をシリコンLSIチップ上に作製する新手法を開発。

産総研では、MgO下地層を用いることによって任意の基板の上に高配向・超平滑な電極層を作製する手法を開発した。これにより、シリコンLSIチップ上に高性能TMR素子を作製することが可能となる。

今後、単結晶電極を持つTMR素子の更なる特性の向上を行い、超Gbit級MRAMの実現を目指す。

なお、上記の研究成果のうち、「量子サイズ効果を用いたトンネル磁気抵抗素子の信号強度の向上」については、産総研と科学技術振興事業団【理事長 沖村 憲樹】との共同研究契約に基づき、戦略的創造研究推進事業の中の研究領域「電子・光子等の機能制御」【研究統括 菅野 卓雄(東洋大学 理事長)】における研究テーマ「固体中へのスピン注入による新機能創製」の一環として行われた。

MRAM(Magnetoresistive Randam Acess Memory)は、DRAMに代わる大容量で高速な不揮発性メモリとして世界的に開発が行われているメモリである。現状技術を用いることにより1Gbit程度のMRAMの実現は見通しが立っているが、それ以上の高集積化のためには、MRAMの心臓部であるTMR素子の特性を飛躍的に向上させる必要がある。現状のTMR素子の信号出力電圧(TMR比に比例する)は30mV程度と、DRAMの信号出力電圧(100mV以上)に比べて小さいために、集積度を上げるに従いノイズに埋もれて読み出せなくなってしまう。また、情報の書き込みはTMR素子の磁化の向きを磁場により変えることにより行われるが、集積度の増大に従い、この書き込み磁場のばらつきが無視できなくなるという問題を抱えている。既存技術では、TMR比の向上のために、TMR素子の電極材料やプラズマ酸化・熱処理条件の最適化が検討されてきており、現在、室温で約50%のTMR比が実現されているが、このような従来の手法によるTMR比の向上は原理的に飽和に近づきつつあり、TMR比を向上させる抜本的な解決策が求められてきた。また、書き込み磁場のばらつきは、TMR素子の電極の表面が原子レベルで凸凹していることにより発生するが、結晶方向がバラバラな多結晶状態の強磁性電極を用いている現状のTMR素子では、その凹凸をなくすことは困難であった。

産総研では、今回、結晶方向の揃った単結晶状態の強磁性電極を用いるTMR素子をSiO2上に成長させる技術を開発することにより、上記の問題の新しい解決手法を示した。これによりMRAMのGbitを超える超大容量化の道が拓けた。

(1)電極の超薄膜化によるTMR比の向上

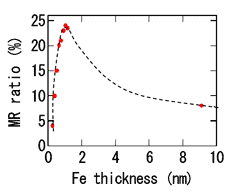

単結晶強磁性電極(Fe(001))を用いてTMR素子を作製し、Fe(001)電極の厚さを非常に薄く(2nm以下)かつ平滑にするとTMR比が増大するという新たな現象を発見した【図1参照】。TMR比は従来、電極に使用する強磁性物質に固有な値と考えられており、実用的な観点から本命の材料とされるFe,Co,Niなどの強磁性遷移金属では60%程度が限界と考えられている。今回の成果は、TMR比が物質固有の値ではなく、ナノテクノロジー(電極の超薄膜化によって、電子が閉じ込められる量子サイズ効果がおきた)を用いると、その値を大きく変えることができることを実証したものである。この現象を用いれば、従来型のCo-Fe電極を用いたTMR素子においても強磁性電極層を超薄膜化することによってTMR比を向上させることが可能である。また、強磁性電極を薄くすると、TMR素子を微細化した時に書き込みが容易になるという、高集積MRAMに適した利点もある。

|

|

図1 単結晶Fe(001)電極を持つTMR素子のTMR比(縦軸)とFe電極の厚さ(横軸)の関係

( Feの厚さが1nm付近でTMR比が増大する )

|

(2)単結晶電極を用いて電極を超平滑化

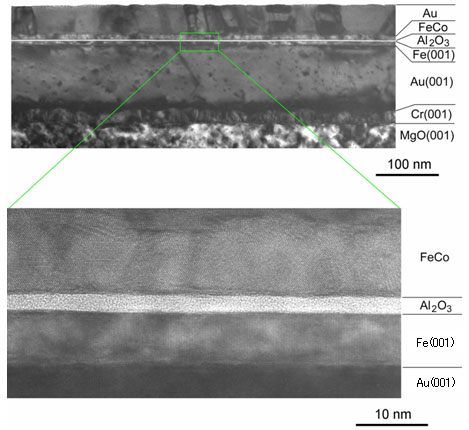

TMR素子の二つの強磁性電極の表面が凸凹していると、この電極間に磁気的な結合が発生し、その磁化の向きを変えるために必要な磁界の大きさがばらつき、MRAMの書き込みが困難になる。現状の多結晶電極を用いたTMR素子の場合、結晶粒に起因した電極表面の凹凸によって静磁気結合が生じることが問題になっている。これを解決する有効な手法は、電極層を単結晶化して結晶粒をなくすことである。産総研では、TMR素子の電極を単結晶化することによって電極表面を原子レベルで平滑することに成功した【図2参照】。

|

|

図2 単結晶Fe(001)電極を持つTMR素子の断面の電子顕微鏡(TEM)写真

( 原子レベルで平滑な電極の作製に成功 )

|

(3)単結晶TMR素子をシリコンLSIチップ上に作製する新手法

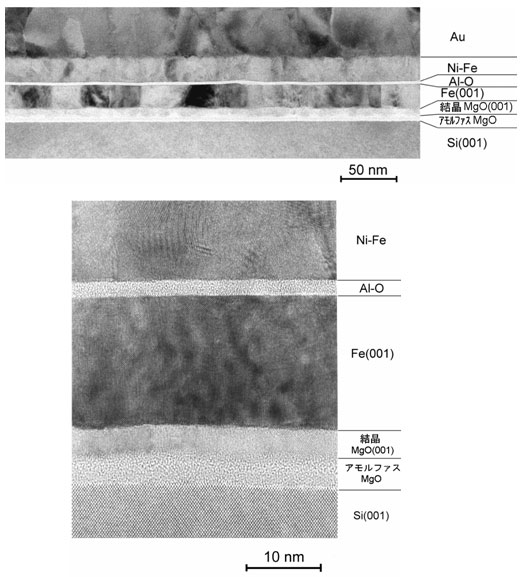

このように単結晶電極を持つTMR素子は優れた特性を有するが、下地にMgOやGaAsの単結晶基板を用いたのでは実用的ではない。MRAMではシリコンLSIチップ上にTMR素子を作製するため、酸化シリコンや金属配線の下地の上にTMR素子を積層する必要がある。産総研では、MgO下地層を用いることによって任意の下地の上に単結晶的な高配向・超平滑な電極層を作製する手法を開発した【図3】。厚さ10nmのMgOをスパッタ成膜すると、下部はアモルファス構造のMgOが成長するが、上部は高配向のMgO(001)が成長する。その上に金属層を成長させると、非常に平滑で単結晶的な強磁性電極を作製することができる。産総研では、実際に酸化シリコン上にこのようなTMR素子を作製することに成功した。これにより、シリコンLSIチップ上に新型高性能TMR素子を作製することが可能となる。

|

|

図3 MgO下地層を用いてシリコン基板上に作製したTMR素子の断面の電子顕微鏡(TEM)写真

( 原子レベルで平滑な界面を持つ単結晶的Fe(001)電極層の作製に成功 )

|

現時点で最高のTMR比を示す電極材料(CoFe合金)を用いて、非常に薄い単結晶電極を持つ新型TMR素子を作製し、TMR比50%を越える最高性能のTMR素子の実現を目指す予定。さらに、TMR素子の超微細化(100nmスケール)を行い、1Gbitを越える高集積MRAM実現に向けた基本技術の確立を目指す予定である。