従来、

窒化シリコン膜は、

アモルファス構造のものしか得られなかったが、今回、結晶構造を持った

単一分子層の窒化シリコン膜を実現した。

独立行政法人 産業技術総合研究所【理事長 吉川 弘之】(以下「産総研」という)は、アトムテクノロジー研究体【プロジェクトリーダー 田中 一宜】(以下「JRCAT」という)と共同で、N2/H2ガスを用いた直接熱窒化プロセスを新たに開発し、シリコン表面上に結晶構造を持った単一分子層窒化シリコン膜を形成することに世界で初めて成功した。

窒化シリコン膜は、ULSIプロセスで重要な役割を持つ膜であるが、従来、シリコン表面上に極薄窒化シリコン膜を形成するとアモルファス構造のものしか得られず、薄膜化するほどその構造の不均一性が問題となっていた。

今回、構造を完全に制御した単一分子層の窒化シリコン膜を形成できるようになった事により、今後、ULSIデバイスの高集積化技術への応用が期待できる。

現在LSIは、様々な製品に使用されている。特にその中でも、パソコン、ゲーム機等の情報家電分野では、機能の高度化、扱う情報の大規模化に伴い、益々高性能なLSIが熱望されている。

この「 LSIの高性能化 」のためには、「 LSIのスケーリング則 」が大きな役割を演じてきた。これは、トランジスタの設計寸法を一定のルールで縮小化すると性能が向上するというものである。トランジスタを縮小化すれば、トランジスタ中を電子が流れる時間を短くでき、信号処理速度を向上させることができるが、スケーリング則によると電子が流れる部分の寸法だけを小さくしても向上せず、トランジスタの三次元的な構造を比例縮尺的に小さくする必要がある。即ち「チャネル長さを1/2」にすると、それに従い「チャネル幅やゲート酸化膜の厚さ等も1/2」にしなければならないということである。このような微細化がLSIの高速化、高性能化のための一つの方策であり、半導体メーカーは、スケーリング則に従いLSIの高性能化を達成してきた。

しかし、近年その着実な高性能化も限界に達しつつある。現在、主に使用されているLSIでは、シリコン表面に設けられる電気回路配線の最小加工寸法は約0.13µm程度であり、このようなLSIを構成するゲート酸化膜の厚さはおよそ1.5~2nm程度である。ここで「µm」という単位は、「1万分の1cm」という微細な単位で、「nm」は「さらにその1000分の1」である。更なる高性能化のため、スケーリング則に従いLSIを微細化すると、2010年頃にはゲート酸化膜の厚さは0.6~0.8nm程度が必要とされるようになると考えられている。これはシリコン酸化膜で3~4分子層程度という極めて薄い酸化膜であることを意味している。

酸化膜がこのような薄さになると、もはや絶縁膜としての効果は期待できなくなる。電子のトンネル効果により、絶縁膜を通り抜けて電流が流れてしまうためである。その問題への対策として考えられているのが、シリコン酸化膜よりも誘電率の大きい「high-k材料をゲート絶縁膜として使用する」というものである。high-k材料を使用することで、スケーリング則に従ったまま、絶縁膜の厚さを増やすことができ、それにより極薄シリコン酸化膜で問題となる直接トンネル電流を減少させようというものである。

このhigh-k 材料のゲート絶縁膜としての応用に関して最も大きな問題と考えられているのが、ゲート絶縁膜とシリコンとの界面で生じる界面反応である。high-k材料として期待されている物質の多くは金属酸化物で、これをシリコンの表面に堆積し、熱処理を行うと、金属酸化物とシリコン間の界面反応が発生し、酸化シリコンや金属酸化物のシリケートが形成されてしまい、急峻な界面の形成ができず、シリコン酸化膜1nm相当の厚さを持ったhigh-k膜を形成できない。このため、界面反応の発生メカニズムや、界面反応を抑制する表面処理技術の研究が進められている。

従来、種々の材料をhigh-k材料とシリコン表面の境界に形成し、界面反応を阻止することが試みられてきた。その中で近年、極薄窒化シリコン膜を界面に挿入すると、界面反応を抑制する効果があることが示され、注目されている。これは、窒化シリコン結合が強固であること、結合距離が小さいため酸素等の原子の透過を抑制できることに起因すると考えられている。

この材料は、high-k材料よりも低い誘電率を持つため、厚い窒化膜を界面に挿入すると、厚い窒化膜部分の誘電率の寄与が大きくなってしまい、絶縁膜全体の誘電率を低く抑えることができなくなってしまう。そこで、できるだけ薄い窒化膜を使用することが重要である。

しかし、CMOSに用いられてきたシリコン(001)面上に窒化シリコン膜を形成(アモルファス構造を持った窒化シリコン層となる)し、その膜を極限まで薄くすると、構造が不均一となり界面での反応を阻止できなくなる恐れがある。界面層として使用するためには極限まで薄い層を均一に形成することが重要であり、アモルファス構造では制御は困難であった。

我々のグループ(産総研&JRCAT)では、極薄窒化シリコン膜の形成の方法を探ってきた。その結果、新たにN2/H2ガスを用いた直接熱窒化プロセスを開発し、それによりシリコン(001)表面上に結晶構造( 2×2周期構造 )を持った単一分子層窒化シリコン膜を形成することに世界で初めて成功した。

従来、窒素ガス、アンモニアガス、あるいは窒素プラズマ等で形成された窒化シリコン膜は、先にも述べたとおり全てアモルファスであった。これは、シリコンと窒素の結合距離が短いため、表面で窒素吸着による均一な周期的構造を形成した場合、下地のシリコンの結晶格子が著しく歪んでしまうことが原因である。歪みが少なくなるように、窒素原子を表面に均一に吸着させてやると、今度はシリコンの余った結合が大量にできてしまい表面のエネルギーを大きくしてしまう。このような理由からシリコン表面上には均一な周期構造を持った極薄窒化シリコンは形成できないものと考えられていた。

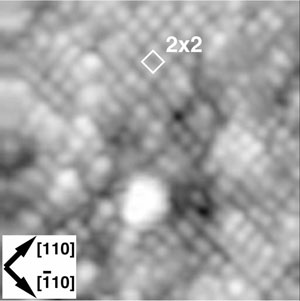

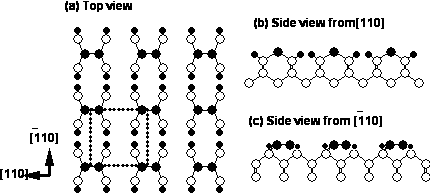

我々のグループでは、上記のような現状を詳細に検討してきた。その結果、シリコン表面に現れるシリコンの未結合手を終端して表面を安定化させる効果を持つ水素を、反応ガス中に添加することにより均一な周期構造を持った極薄窒化シリコンを形成できることを見いだした。【Fig.1】 これは、窒素吸着構造が形成される際に歪みが少なくなるように、窒素原子を表面に均一に吸着させ、それに伴い発生したシリコンの未結合手を水素ガスによって終端することで、周期構造の形成と表面歪み、及び表面エネルギーの上昇抑制を同時に達成するものである。【Fig. 2】

この手法を用いることにより、high-k膜とシリコン界面の反応を抑制する最も薄い膜を、完全に制御した構造及び厚さで形成できるので、将来的に望まれる「原子レベルでの半導体製造技術」の一つとして、high-k材料のデバイス応用を1歩前進させることができると考えられる。

|

|

|

|

|

|

Fig. 1 単一分子層窒化したシリコン(001)表面のUHV-STM像。

10×10nm。白枠は2×2周期構造に相当するユニットセル。 |

|

|

|

|

|

|

|

Fig. 2 Si(001)-2×2:N表面の構造モデル。

小さな黒丸が水素原子、大きな白丸がシリコン原子、

大きな黒丸が窒素原子にそれぞれ対応している。 |

|