国立研究開発法人 産業技術総合研究所【理事長 石村 和彦】(以下「産総研」という)は、国立研究開発法人 新エネルギー・産業技術総合開発機構(以下「NEDO」という)「ポスト5G情報通信システム基盤強化研究開発事業 研究開発項目②先端半導体製造技術の開発 (b)先端半導体の後工程技術(More than Moore技術)の開発 (b1)高性能コンピューティング向け実装技術」において、TSMCジャパン3DIC研究開発センター(株)(以下「3DICセンター」という)が実施する研究開発の中で、同社と3DIC実装のための新材料・新プロセス技術の開発に関する共同研究を実施します。3DICセンターは、産総研および国内企業の材料・プロセス技術を評価・検証する研究開発用パイロットラインを、産総研つくば西事業所の高機能IoTデバイス研究開発棟に構築します。

Society 5.0を支える技術基盤として、先端半導体を確保することの重要性が改めて認識されています。例えば、超高速・低遅延・多数同時接続といった特長をもつ第5世代移動通信(5G)は、各種サービスに用いられ始めていますが、スマート製造やコネクテッドカーといった高信頼性を要する産業用途には、5G の機能を強化したポスト5G技術とコンピューティング技術を融合させた情報通信基盤が必要です。そこで求められるのが、高性能・低消費電力・高信頼性の先端半導体です。2019年10月29日に官邸にて開催された第32回未来投資会議では、「5Gの加速及びポスト5Gのあり方」が議題として取り上げられ、先端半導体の製造能力が日本国内に無い現状への対応が議論されました。

半導体の製造は、一般にシリコンウエハーに回路を作りこむ前工程と、ウエハーからチップを切り出してパッケージング(実装)する後工程に大別されます。この前工程においては、これまで回路の性能向上を実現してきた微細加工が物理的限界に近づいているため、高機能化や多機能化を継続していくために後工程の重要性が増しています。具体的には、演算を行うロジックチップと、メモリー・アナログデバイス・センサーなどを一つのパッケージに統合する3次元あるいは2.5次元の実装技術の高度化が求められています。わが国には、後工程に用いる材料や装置について強みを有する企業が多数存在します。また、産総研は、これまでにNEDOプロジェクト等を通じて開発した後工程向けの材料・プロセス・評価・シミュレーション技術を有しています。

このような背景の下、NEDO「ポスト5G情報通信システム基盤強化研究開発事業/先端半導体製造技術の開発」の中で公募された「先端半導体の後工程技術(More than Moore技術)の開発」において、産総研は、3DICセンターが提案し採択された「3DIC技術の研究開発」について、同社と共同研究を行うこととなりました。3DICセンターは、世界最先端の半導体製造技術を有するTaiwan Semiconductor Manufacturing Company, Ltd.(以下「TSMC」という)が設立した日本法人です。

このNEDO事業において、3DICセンターは、TSMCが開発したChip-on-Wafer-on-Substrate(CoWoS®)構造をベースとして、高性能コンピューティング向け先端半導体(5 nmノード以降)の実装に必要となるパッケージ基板の大面積化、3次元・高密度実装向け材料技術、製造装置等の開発とこれらに対応するアセンブリー・パッケージング技術などの開発を行います。

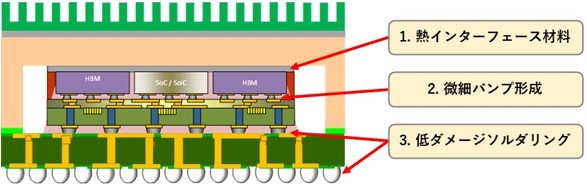

産総研は、3DICセンターと共同で、新材料・新プロセス技術の開発を行います。最先端の3DIC実装における重要な技術課題として、デバイス動作時に発生する熱の効率的な除去、チップの薄化や集積化による応力発生や反りの制御、狭ピッチでの電気接続における信頼性・インテグリティの確保などが挙げられます。これらの課題解決の鍵となるのは、従来技術の限界を超える新材料や新製造プロセス技術です。具体的には、産総研がこれまでに確立した基本技術を応用して、熱インターフェース材料、微細バンプ形成、低ダメージソルダリングの研究開発を行います。

3DIC構造の断面図と産総研が担当する研究開発内容

3DICセンターは、産総研および基板・材料・装置等の共同開発を行う企業が開発した要素技術を評価・検証するために、研究開発用パイロットラインを産総研つくば西事業所の高機能IoTデバイス研究開発棟のクリーンルーム(1,800 m2)に構築します。この研究開発用パイロットラインは、TSMCの最新技術と、3DICセンターが産総研および共同開発先企業と開発する技術を一カ所に集めたものです。プロセス・材料・計測の開発や適用をオンサイトで行い、その結果を短期間でフィードバックすることで、新たな3DIC構造の開発加速が期待されます。このプロセス・材料・計測が三位一体となった拠点は、3DIC実装技術開発の新たな地平を拓くとともに、世界水準の半導体後工程技術を国内に確保するものです。産総研は、TIAにおけるオープンイノベーション推進の経験を生かして、研究開発用パイロットラインの運営に協力するとともに、そこで協働する後工程関連企業の研究開発をサポートしていきます。

産総研では、NEDO「ポスト5G情報通信システム基盤強化研究開発事業/先端半導体製造技術の開発」の「先端半導体の前工程技術(More Moore技術)の開発」において、東京エレクトロン(株)、(株)SCREENセミコンダクターソリューションズ、キヤノン(株)の3社との共同研究により、3DICセンターの研究開発用パイロットラインと隣接するスーパークリーンルーム棟に前工程のパイロットラインの構築を開始しています。今回、3DICセンターが後工程パイロットラインを産総研内に構築することで、産総研は、前工程と後工程の両方の施設を敷地内に有することになります。産総研は次世代コンピューティング基盤開発拠点として、2030年を見据えた戦略策定、各種革新技術の研究開発、試作・評価環境の整備を包括的に進めています。経済産業省の第1回半導体・デジタル産業戦略検討会議(2021年3月24日)において示された半導体戦略の方向性も踏まえつつ、産総研は先端的な半導体を将来的に国内で製造するための技術の確保に貢献していきます。

高機能IoTデバイス研究開発棟

国立研究開発法人 産業技術総合研究所

広報部 報道室

TEL:029-862-6216 FAX:029-862-6212

E-mail:hodo-ml*aist.go.jp(*を@に変更して使用してください。)