NEDOは、AIチップ開発加速のためのイノベーション推進事業を行っており、産業技術総合研究所、東京大学と共同で、東京大学浅野キャンパス(東京都文京区)内に「AIチップ設計拠点」の整備を進める中で、本日より中小・ベンチャー企業など向けに試験運用を開始しました。

本拠点では、省エネルギーで効率的にAIを動作させるAIチップの設計に必要なEDAツールやハードウェアエミュレーター、標準IPコアなどを提供するほか、これらを活用する設計フローなどの共通基盤技術も提供します。

今後、中小・ベンチャー企業などの本施設の活用に関するフィードバックをもとに、さらに使いやすいAIチップ設計拠点として整備し、AIチップ開発加速への貢献を目指します。

|

|

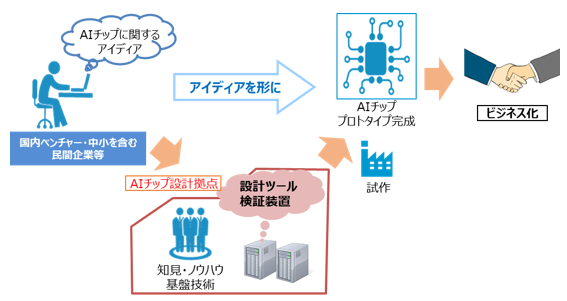

図1 AIチップ設計拠点の概要 |

目覚ましく進展するIoT社会において、実世界のさまざまな形態の情報であるビッグデータから人々の生活に新たな価値を創造するための鍵となる技術として人工知能(AI)技術が注目されています。

一方、AI技術の根幹をなす半導体集積回路の微細化が物理的な限界に近づいており、エネルギー消費の増大が極めて大きな課題となっています。この課題を解決するためには、省エネルギーで効率的にAIを動作させる半導体集積回路・デバイス(AIチップ)の開発が必要不可欠であり、世界的にもAIチップの開発競争が激化しています。

日本では、多くの中小・ベンチャー企業などが台頭し、AIチップの開発に取り組んでいます。しかし、AIチップの開発には、EDAツール※1やハードウェアエミュレーター※2(H/Wエミュレーター)、標準IPコア※3などが必要であり、中小・ベンチャー企業などに革新的な構想があったとしても、AIチップの研究開発に対する壁になっています。

このような背景のもと、国立研究開発法人 新エネルギー・産業技術総合開発機構(NEDO)は、AIチップ開発加速のためのイノベーション推進事業※4において、国立研究開発法人 産業技術総合研究所(産総研)、国立大学法人東京大学(東京大学)と共同で、東京大学浅野キャンパス(東京都文京区)内の武田先端知ビルに整備中の「AIチップ設計拠点」で、AIチップ設計に必要なEDAツールやH/Wエミュレーター、標準IPコアなどからなるAIチップの設計環境を整えるとともに、これらを活用する設計フローなど、AIチップ設計のための共通基盤技術の開発、知見・ノウハウの蓄積や人材育成などを進めています。

今般、本プロジェクトで拠点整備を進める中で、EDAツールや標準IPコアの選定、導入などAIチップの設計環境の試用準備が整ったことから、本日より中小・ベンチャー企業を中心に広く公開し、試験運用を開始しました。

本拠点では、AIチップの設計に必要なEDAツールやH/Wエミュレーター、標準IPコアなどを中小・ベンチャー企業などに提供し、またこれらを活用する設計フローなどの共通基盤技術も提供します。

今後、利用者からのフィードバックなどを活用して、さらに使いやすいAIチップ設計拠点として整備していきます。

なお、10月15日(火)から18日(金)まで開催されるCEATEC 2019のNEDOブースにおいて、本「AIチップ設計拠点」の紹介およびデモンストレーションを実施します。NEDOブースの詳細については、NEDOイベントページ(URL:https://www.nedo.go.jp/events/IT_100047.html)をご参照ください。

【1】さまざまな利用形態に対応

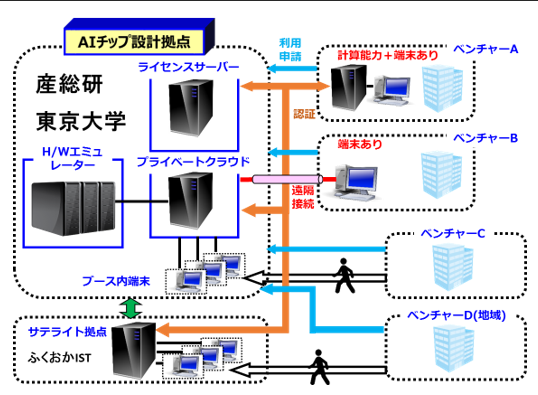

本拠点の利用者は直接、利用ブースで設計環境を利用できるほか、遠隔からもネットワークを介して設計環境を利用できます。また、本拠点から離れた地域で活動する利用者は、地域サテライト拠点に設置する利用ブースからも本拠点の設計環境を利用することができます。現在、九州地域では、公益財団法人 福岡県産業・科学技術振興財団(ふくおかIST)が、ロボット・システム開発センター(福岡システムLSI総合開発センター)内に地域サテライト拠点として利用ブースを設置しています。サテライト拠点は、今後、追加していく予定です(図2)。

なお、本拠点の利用申請は、ウェブサイト(https://ai-chip-design-center.org)から可能です。また、NEDOと産総研、東京大学が拠点で主催するフォーラムの案内をはじめ、拠点から発信するニュースも、本ウェブサイトに掲載されます。

|

|

図2 AIチップ設計拠点の利用形態 |

【2】EDAツール、H/Wエミュレーターや標準IPコアを整備

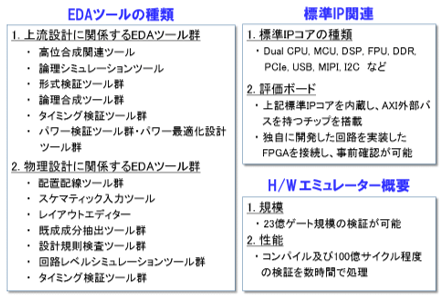

本拠点では、EDAツール、H/Wエミュレーターならびに標準IPコアを整備しています。EDAツールとしては、上流設計※5に関係するEDAツール群はもちろんのこと、物理設計※6に関係するツール群が利用可能です。H/Wエミュレーターは、国内最大規模の23億ゲートの大規模回路で100億サイクルを数時間で検証できる装置が利用可能です。標準IPコアについては、40nmプロセスや28nmプロセスで利用できる標準インタフェース回路などを準備しているほか、それら標準IPコアを搭載した評価ボードを用いて、利用者が開発した回路と標準IPコアの接続などを事前に評価することができます(図3)。

|

|

図3 本拠点で整備しているEDAツール、H/Wエミュレーター、標準IPコアの情報 |

NEDOは、産総研、東京大学とともに、中小・ベンチャー企業などの本拠点利用者からのフィードバックや、本拠点で研究開発中のAIチップ設計に関する共通基盤技術などを活用して、さらに使いやすいAIチップ設計環境を構築していきます。また、共通基盤技術や拠点で蓄積した知見・ノウハウをベースにした教材などでAIチップ設計技術者を育成します。

これらの取り組みにより、AIチップ設計拠点の確立と、日本の中小・ベンチャー企業などのAIチップ開発加速への貢献を目指します。