国立研究開発法人 産業技術総合研究所【理事長 中鉢 良治】(以下「産総研」という)エレクトロニクス・製造領域【領域長 金丸 正剛】AI chip Design Laboratory(以下「産総研 AIDL」という)と国立大学法人 東京大学(以下「東京大学」という)【総長 五神 真】大規模集積システム設計教育研究センター(以下「東京大学 VDEC」という)は協力してわが国の革新的なAIチップ開発を加速するための「AIチップ設計拠点」を、東京大学 本郷キャンパス浅野地区武田先端知ビルに構築しました。

本拠点(推進責任者 産総研 AIDL ラボ長 内山 邦男)は、産総研および東京大学が共同で提案し、採択された経済産業省「産業技術実用化開発事業費補助金(AIチップ開発加速のための検証環境整備事業)」、および国立研究開発法人 新エネルギー・産業技術総合開発機構(以下「NEDO」という)「AI チップ開発加速のためのイノベーション推進事業」を活用し、AIチップ開発を目指す中小・ベンチャー企業などに、EDAツール群やエミュレーターからなるAIチップ設計環境や、設計フローやリファレンスデザインなどの共通基盤、拠点に蓄積される設計資産やノウハウ、AIチップ設計人材育成環境を提供することで、わが国の中小・ベンチャー企業などのAIチップ開発加速への貢献を目指すとともに、産官学協調によるAIチップ開発の加速を目指します。

|

|

AIチップ設計拠点の概要 |

目覚ましく進展するIoT社会において、実世界のさまざまな形態の情報であるビッグデータから人々の生活に新たな価値を創造するための鍵となる技術としてAI(人工知能)技術が注目されています。特に近年のAI技術は急速な発展を遂げており、画像認識、音声認識、自動運転といったさまざまな分野に広がりを見せるとともに、AI技術が人々の日常生活に浸透していく時代が到来しつつあります。

他方、IoTやAI技術の根幹をなす半導体集積回路の微細化は物理的な限界に近づいており、エネルギー消費の増大が極めて大きな課題となってきています。これらの課題を解決するためには、省エネルギーで効率的にAIを動作させる半導体集積回路・デバイス(AIチップ)の開発が必要不可欠であり、世界的にもAIチップの開発競争が激化しています。

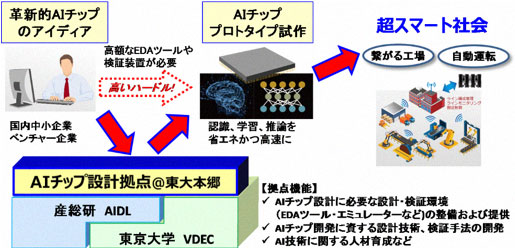

日本国内においては多くの中小・ベンチャー企業などが台頭し、AIチップの開発に名乗りを上げている状況です。しかしながら、AIチップの開発には、極めて高価なEDAツールやエミュレーターが必要なことに加えて、AIのアイデアからAIチップを作り上げるまでにはさまざまな壁が存在しています(図1)。

産総研および東京大学は協力して、国内中小・ベンチャー企業などのAIチップ開発を加速するために、AIチップ開発に必要なさまざまな機能をオンサイト、もしくは遠隔からでも利用できる環境を提供する「AIチップ設計拠点」を東京大学本郷キャンパス浅野地区武田先端知ビル内に設置しました。それに併せ、当拠点を先導的に推進する立場として、株式会社 日立製作所にて半導体集積回路に関する研究開発を主導してきた内山 邦男を産総研に招聘(しょうへい)しました。また、産総研および東京大学は、この度、経済産業省「産業技術実用化開発事業費補助金(AIチップ開発加速のための検証環境整備事業)」(以下「METI事業」という)、およびNEDO「AI チップ開発加速のためのイノベーション推進事業/研究開発項目②:AI チップ開発を加速する共通基盤技術の開発」(以下、「NEDO事業」という)に共同で提案し、採択されました(産総研側代表者 産総研 ナノエレクトロニクス研究部門 副研究部門長 昌原 明植、東京大学側代表者 東京大学 VDEC 教授 池田 誠)。

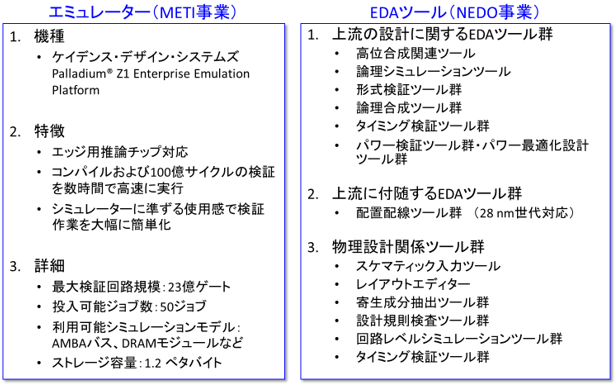

本拠点は、METI事業やNEDO事業を活用して最先端のEDAツールと大規模論理検証装置を導入し、AIチップ設計・検証環境を整備するとともにエミュレーターを組み込んだ設計フローとツールチェーンを提供していきます。また、AIチップ開発未経験の企業が開発の参考にできるリファレンスデザインやセンサー機能を組み込んだAIチップ開発のためのセンサーデバイスモデル、AIチップを国内の半導体製造拠点(FAB)で試作する際に必要不可欠なライブラリーといった設計基盤を開発し、拠点を利用する中小・ベンチャー企業などに提供していきます。またこれと同時に、集積回路開発人材の底上げを目的として人材育成も実施していきます(図1)。

|

|

図1 AIチップ設計拠点における取り組み |

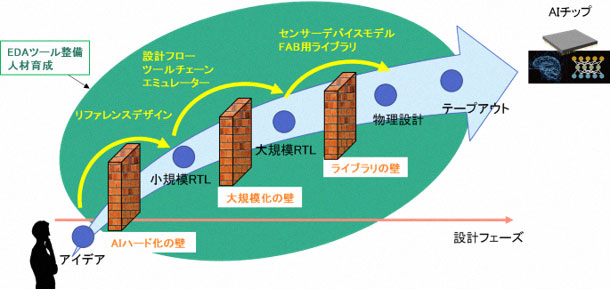

NEDO事業では、本拠点での活用を目指して、AIチップの機能や振る舞いを論理回路レベルで設計する上流設計に関係するEDAツール群はもちろんのこと、上流設計結果に基づいてライブラリーを適切に配置・配線することでAIチップの設計図を作成、設計図の検査といった物理設計に関係するツール群も導入します(図2)。さらに、23億ゲートの大規模AIチップ回路で100億サイクルを数時間で検証できるエミュレーター使用環境も整備します。

|

|

図2 AIチップ設計拠点に導入するEDAツール群(予定)とエミュレーター |

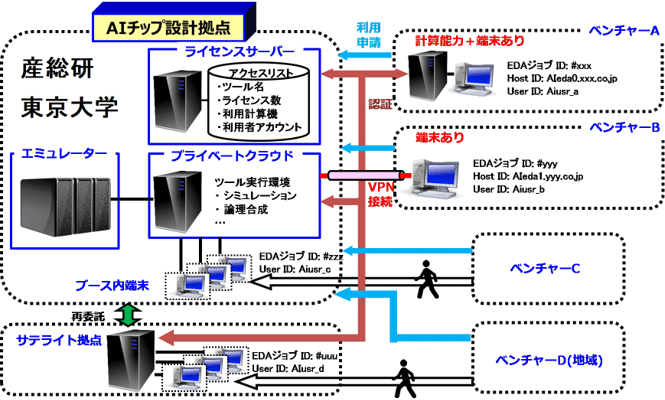

また、さまざまなAIチップ設計環境を有する中小・ベンチャー企業などに対応できるように、オンサイト、もしくは遠隔からでも利用することができ、利用者間の秘匿性を確保した拠点を構築していきます(図3)。利用者自身が比較的高性能な計算機を有する場合には、利用者自身の計算機にEDAツールをインストールし、ライセンス認証を行い利用することができます(図3:ベンチャーAに相当)。また、利用者自身が高性能な計算機を有していない場合には、拠点に設置するプライベートクラウド上のツールを利用することができます(図3:ベンチャーB、Cに相当)。更に、地域中小・ベンチャー企業などに対しては、地域サテライト拠点に設置する利用ブースにおいて利用することができます(図3:ベンチャーDに相当)。九州地域に関しては、公益財団法人 産業・科学技術振興財団(福岡IST)がロボット・システム開発センター(福岡システムLSI総合開発センター)内に地域サテライト拠点を設置しました。

|

|

図3 AIチップ設計拠点の利用イメージ |

本拠点の予約ウェブサイト(URL: http://www.ai-chip-design-lab.org)は平成31年3月頃のオープンを予定しており、中小・ベンチャー企業などは4月以降に本拠点を利用することができます。

また、拠点活動開始を記念いたしまして公開シンポジウムを、平成31年2月12日、武田先端知ビル5階武田ホールにて開催いたします。

中小・ベンチャー企業などがAIチップを開発する場合、さまざまな形態の支援(設備支援、人材育成や開発費の調達など)が必要となります。産総研 AIDLと東京大学 VDECがAIチップ設計拠点を設置することにより、この拠点を中心として、産総研AI関連の研究ユニットとの連携、東京大学 VDECが長年培ってきた人材育成教育メニュー、半導体関連企業やベンチャーキャピタルとの協力による半導体設計の知見やファイナンスを中心とした金融面でのアドバイスやアレンジなどからなるエコシステムが構築されることが期待できます。そして、中小・ベンチャー企業などのAIチップ技術開発を包括的に支援することによって、国際競争力の高い日本発のAIチップの創出を後押しします。