国立研究開発法人 産業技術総合研究所【理事長 石村 和彦】(以下「産総研」という)新原理コンピューティング研究センター【研究センター長 湯浅 新治】川畑 史郎 総括研究主幹らは、デバイス技術研究部門【研究部門長 中野 隆志】らと共同で、超伝導量子ビットから構成される量子アニーリングマシンの開発と動作実証に日本で初めて成功した。

産総研は、特定組合せ最適化問題専用のアーキテクチャ(ASAC)を世界で初めて提唱した。これに基づいて、6量子ビットの量子アニーリングマシンの製造を行い、絶対温度10 mKにおいてその動作実証に成功した。ASACを用いることで、従来方式に比べて1桁程度少ない量子ビット数で、組合せ最適化問題を解くことが可能となる。これにより、問題の大規模化に伴って、計算に必要な量子ビット数が増大するという実用上の課題が軽減される。超伝導量子アニーリングマシンの社会実装は、創薬、運輸などの幅広い産業分野における効率化につながるであろう。なお、この技術の詳細は、2021年6月22~25日にオンライン開催された断熱量子計算国際会議AQC2021で発表された。

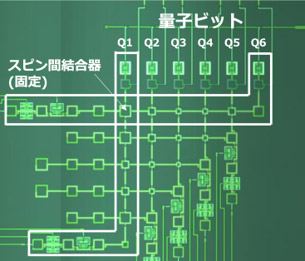

古典2-bit乗算回路専用の超伝導量子アニーリングマシン(6量子ビット)の顕微鏡写真。Q1〜Q6は超伝導量子ビット。

われわれの生活において、いくつかの可能性の中からベストあるいはそれに近い解を求める行為は日常的に行われている。このような問題は組合せ最適化問題と呼ばれ、われわれの日常生活だけではなく、薬の開発や運輸業での最適な経路の探索などさまざまなビジネス分野に内在している。しかし、組合せ最適化問題は、問題の規模が大きくなればなるほど、その計算時間が急激に増加することが知られている。そのため、メガビット〜ギガビット級の大規模な実用的組合せ最適化問題を効率的に解くことが、今後構築を進めるSociety 5.0において必須となっている。

そのような背景から、量子アニーリングに大きな注目が集まっている。量子アニーリングとは、組合せ最適化問題をイジング模型の最小エネルギー状態探索問題に変換し、量子力学的重ね合わせを制御して、近似解を求める手法である。変換後のイジング模型は、複雑に相互作用する量子ビット(スピン)から構成されている。そのため、隣の量子ビットとしか相互作用しない実際のハードウエアにおいては、任意の組合せ最適化問題を解くために、「グラフ埋め込み」と呼ばれる方法を用いて、遠くの量子ビット同士の相互作用を実装している。

カナダのベンチャー企業D-Wave Systems社は、2011年に超伝導量子ビットとグラフ埋め込み技術を利用した量子アニーリングマシンの商用化に成功し、2020年に5000量子ビット級の製品D-Wave Advantageを販売した。また、アメリカおよびヨーロッパにおいても、同種の量子アニーリングマシンの実現を目指した大型国家プロジェクトが進められている。

グラフ埋め込み技術を用いる従来型の量子アニーリングマシンは、量子ビットのコピーを大量に用意することで、任意の遠隔量子ビット間の相互作用を実装している。そのため、現状の量子ビット数では、大規模な組合せ最適化問題を扱えないという深刻な問題があり、それが社会実装のための障害となっていた。グラフ埋め込み技術を用いた5000量子ビットの量子アニーリングマシンで巡回セールスマン問題を解く場合、せいぜい10都市程度までしか扱うことができない。しかしながら、社会実装のためには、自由度が10万以上のさまざまな組合せ最適化問題を解くことが求められている。

さらに、量子アニーリングマシンの性能向上のためには、量子ビットの量子コヒーレンスを維持することが極めて重要であると考えられている。しかし、コヒーレンス性能が高い量子ビットを用いたとしても、グラフ埋め込みによって計算性能が大幅に劣化することが最近の研究で示されていた。

産総研は、長年培ってきた超伝導集積回路の研究開発を発展させ、超伝導量子アニーリングマシンと超伝導量子コンピューターのハードウエア設計・製造・評価基盤技術の確立および社会実装へ向けた研究開発を産学官連携の下ですすめている。また、内閣府統合イノベーション戦略会議が2020年に策定した「量子技術イノベーション戦略」に基づき、産総研に設置された「量子デバイス開発拠点」(拠点長:安田哲二)において、本研究開発を実施している。

なお、本研究開発は、国立研究開発法人新エネルギー・産業技術総合開発機構の委託事業「高効率・高速処理を可能とするAIチップ・次世代コンピューティングの技術開発(プロジェクトリーダー 金山敏彦)」における採択課題「組合せ最適化処理に向けた革新的アニーリングマシンの研究開発(2016~2020年度)(研究代表者:山岡雅直)」による支援を受けて、横浜国立大学と連携して行った。

産総研は、特定の最適化問題に特化した量子アニーリングマシンのアーキテクチャ(ASAC)を世界で初めて提唱した。このアーキテクチャに基づいて、古典論理回路に対応する組合せ最適化問題の一例として、古典2-bit乗算回路専用超伝導量子アニーリングマシン(6量子ビット)の設計と製造を行った。

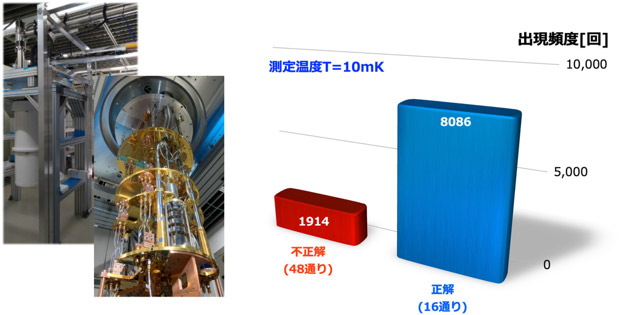

古典2-bit乗算回路の正しい動作は、26=64通りの組み合わせの中で、24=16通りである。図1に、極低温評価システムにおいて得られた、10 mKにおける実験結果を示す。1万回測定を行った結果、80%以上の正答率が得られることが確認された。この成果は、大規模な組合せ最適化問題の処理を可能とする実用的超伝導量子アニーリングマシン実現のための重要な基盤技術となる。

ASACを利用することで、必要最小限の量子ビット数で大規模な組合せ最適化問題を解くことが可能となる。それによって、大規模化の際に障害となっていた冗長量子ビット数をグラフ埋め込み方式に比べて1桁程度抑えることができる。さらに、ASACはさまざまな組合せ最適化問題にも適応可能である。具体例としては、新薬の開発における分子の安定構造の探索などがあげられる。

図1 10 mKの極低温環境を実現する極低温性能評価システム(左)と2-bit乗算回路専用量子アニーリングマシン(6量子ビット)の10 mKにおける実験結果(右)。2-bit乗算回路に対する64通りの解候補の中で、正解は16通りだけ。

1万回測定を行った結果、正答率は80%以上だった。

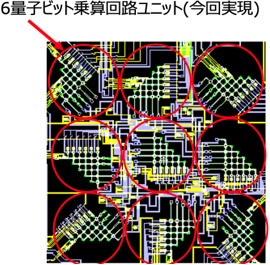

今後、大規模な量子アニーリングマシンを製造し、極低温における動作実証を行い、ASAC方式の優位性の実証を目指す(図2)。また、実用化のためには、正答率を向上させる必要がある。そこで、ノイズ低減技術や高品質量子ビット製造技術を開発する。

図2 6-bit乗算回路専用超伝導量子アニーリングマシン(78量子ビット)の予想図。

今回実現した乗算回路ユニット(6量子ビット)をタイル状につなぎ合わせることで、より大規模な乗算が可能となる。今後、実現を目指す。

国立研究開発法人 産業技術総合研究所

新原理コンピューティング研究センター

総括研究主幹 川畑 史郎 E-mail:s-kawabata*aist.go.jp(*を@に変更して送信下さい。)