# 高性能な NAND フラッシュメモリーアレイ

## 次世代半導体不揮発メモリーの実用化へ前進

酒井 滋樹

さかい しげき (左)

shigeki.sakai@aist.go.jp ナノエレクトロニクス研究部門 新材料・機能インテグレーション グループ 招聘研究員 (つくばセンター)

強誘電体ゲートトランジスタ の実用化を目指して、トラン ジスタ微細化と集積回路メモ リの研究を行っています。

#### 高橋 光恵

たかはし みつえ(右)

mitsue-takahashi@aist.go.jp ナノエレクトロニクス研究部門 新材料・機能インテグレーション グループ 主任研究員 (つくばセンター)

次世代不揮発メモリ素子である強誘電体ゲート電界効果トランジスタの作製とその回路応用の研究をしています。

#### 関連情報:

#### 共同研究者

竹内 健(東京大学)、Zhang Xizhen、厳 康(前産総研 特別研究員)、Le Hai Van、 Zhang Wei(産総研特別研 究員)

#### 用語説明

\*ソリッドステートドライブ (SSD): データを記憶する媒体として半導体不揮発メモリーであるフラッシュメモリーを用い、これに電気信号を与えてデータの消去・書き込みと読み出しを行うデータ記憶装置。

### プレス発表

2011 年 9 月 28 日「 高性能な 64 kb 強誘電体 NAND フラッシュメモリーアレイを作製」

この研究開発は、独立行政 法人 新エネルギー・産業技 術総合開発機構 (NEDO) 省 エネルギー革新技術開発事業 の支援を受けて行いました。

#### NANDフラッシュメモリーの課題

パソコンやサーバーのハードディスクドライ ブに代わる大容量データ記憶装置として、よ り小型軽量で低消費電力のソリッドステート ドライブ (SSD) \*が注目されています。しかし SSDの基本部品である半導体不揮発メモリーの NANDフラッシュメモリーは、書き換え可能回 数が約1万回と少なく、情報処理量の多いデー タセンターのサーバーに用いるには書き換え可 能回数をより多くすることが望ましいと考えら れています。また、集積度を高めるために今後 もNANDフラッシュメモリーセルの寸法を縮小 し続ければ、書き換え可能回数はさらに減少し てデータの信頼性に不安が生じると言われてい ます。このため、書き換え耐性がより高く、メ モリーセルの寸法縮小も可能な、次世代半導体 不揮発メモリーの開発が必要です。

#### Fe-NANDフラッシュメモリーアレイの作製

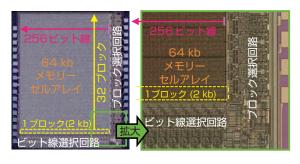

私たちは、強誘電体ゲート電界効果トランジスタ (FeFET) をメモリーセルとして用いる強誘電体NANDフラッシュメモリー (Fe-NANDフラッシュメモリー) に注目し、FeFETの集積化技術により、初めて全ビット測定が可能な64キロビット(kb) Fe-NANDフラッシュメモリーアレイの作製に成功しました(図1)。

図 1 今回作製したチップの全体写真(左)とチップの右下隅を拡大した光学顕微鏡写真(右)

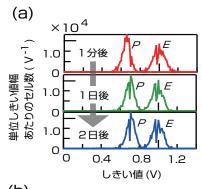

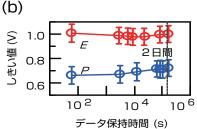

図2 ある 1 ブロックにおける 1 分後、1 日後、2 日後の しきい値分布 (a) と 2 日間の測定によるデータ保持特性 (b) E: ブロック消去後、P: 全ビット書き込み後

この64 kb Fe-NANDフラッシュメモリーアレイを用いて、ブロック消去、ページ書き込み、データ非破壊読み出しを行い64 kbのすべてのメモリーセルにアクセスできることを確認しました。さらに、全ビットの消去と書き込み、市松模様状書き込みの3通りのパターンを書き込み、これらの読み出しに成功しました。また、ブロックレベル(2 kb)で2日間の測定による良好なデータ保持特性(図2)のほか、セルレベルでは1億回書き換え可能であることも確認しました。

将来的には、Fe-NANDフラッシュメモリーのデータ書き込み時のビット線電圧は1 V、ワード線電圧は6 Vまで下げることができ、これまでのNANDフラッシュメモリーと比べて消費電力は約7分の1になると見込まれます。

#### 今後の予定

今後はFe-NANDフラッシュメモリーセルの 微細化を進め、シリコンデバイスにおける目安 のサイズの一つであるゲート長0.18 μmを達成し、その後、さらに小さいゲート長0.05 μmの Fe-NANDフラッシュメモリーを数年以内の実用化を目指します。低消費電力で1億回の書き 換え可能回数をもつ特性を活かし、データセンター向けSSDを最初の実用化のターゲットとしたいと考えています。