## オン抵抗世界最小のパワー MOSFET

### イオン注入とエピタキシャル成長膜が生み出す IE-MOSFET

ワイドギャップ半導体のシリコンカーバイドは、低損失の次世代パワー半導体デバイス用の基板として有望視されており、デバイスの開発が盛んに行われている。私たちは、新たに縦型 MOSFET の p ウェル部分を高濃度のイオン注入とエピタキシャル成長膜で構成した IE-MOSFET を考案し、ノーマリーオフで世界最小のオン抵抗を達成した。この成果により、パワー半導体デバイスを用いた省エネルギー化が大きく前進するものと期待される。

Because of wide band-gap, silicon carbide is an attractive semiconductor material for the advanced low-loss power semiconductor device, and much research has been done to realize it. We recently developed IE-MOSFET (Implantation & Epitaxial MOSFET), in which p-well is composed of heavily implanted bottom layer and lightly doped upper epitaxial layer. The fabricated device exhibits a lowest on-resistance among the normally-off power switching semiconductor devices. This result largely advances the energy saving technology using the power semiconductor devices.

#### 限界に近づきつつあるパワー半導体の性能

パワー半導体デバイスは、電力を使用できる形に変換する装置であり、家庭用電化製品、車載用半導体素子、配電系の大電力変換素子など、電気を使うあらゆる機器に組み込まれている。従って、パワー半導体デバイスの変換効率の向上、すなわち変換時の損失の低減が省エネルギー化への大きな貢献となる。これまでのパワー半導体デバイスの損失の低減は、既存のシリコン(Si)パワー半導体デバイスの改良によって進められてきたが、近年はSiの物性からくる性能の限界が近づきつつある。さらに、耐圧600V以上の中

高耐圧領域ではバイポーラデバイスであるIGBTが用いられてきたが、電子と正孔の双方がキャリアとなるためスイッチング時にキャリアの注入と再結合による損失が発生し、このスイッチング損失も通電損失に加えて無視できない状況となってきた。

#### シリコンカーバイトSiCの可能性

この問題に対して、ワイドギャップ半導体であるシリコンカーバイド(4H-SiC)を用いれば、通電時の損失(オン抵抗)をSiパワー半導体デバイスに比べて1桁以上小さくすることができ、さらにショットキーバリアダ

**原田信介** Shinsuke Harada s-harada@aist.go.jp パワーエレクトロニクス研究センタ

パワーエレクトロニクス研究センター デバイスプロセスチーム 1 研究員

これまで、主にシリコンカーバイドパワー半導体デバイスの開発に関する研究に従事してきた。高耐圧のユニポーラスイッチングデバイスとして有望視されるSiC-MOSFETには解決すべき問題が多く、一日も早い実用化に向けて、その構造と製造プロセスの開発を中心に取り組んでいる。

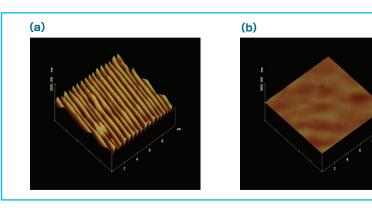

図 1 原子間力顕微鏡で観察した (a) イオン注入層の表面と (b) エピタキシャル成長膜の表面

# esearch

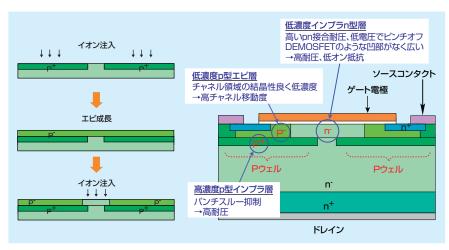

図2 開発した IE-MOSFET の断面構造と製造プロセス

イオード (SBD) とMOSトランジスタ (MOSFET) のユニポーラデバイスの みで変換器が構成できるため、電子の みがキャリアとなることからスイッチ ング時におけるキャリアの注入と再結 合による損失もない。これまでの開発 状況は、SiC-SBDはオン抵抗をほぼ理 論値まで下げることに成功しており、 すでにサンプルの出荷もスタートして いる。

これに対して、SiC-MOSFETはSiの 理論限界を超える特性はいくつか報 告されているものの、SiCの理論値に は遥かに及ばない。その原因の一部 はSiC-MOSFETの構造に関連してい る。通常の構造は、チャネルとなるア クセプタ不純物領域 (pウェル) をイオ ン注入で形成するため、図1(a)のよ うに表面がラフになりチャネルを流れ る電子の移動度が劣化していた。SiC-MOSFETのオン抵抗は大部分がチャ ネル抵抗によるものなのでこの影響 はきわめて大きい。この問題を解決す る手段として、これまでにわれわれ は、pウェルを濃度の異なる二重のp型 エピタキシャル成長膜によって構成し た二重エピタキシャルMOSFET (DE-MOSFET) を開発している。この構造 では、アクセプタの不純物元素をエピ

タキシャル成長時に導入するため、図 1 (b) のようにpウェル表面は平坦にな り、チャネル抵抗の増大を防止するこ とができる。試作の結果、汎用性の高 い600V級のSi-IGBTに比べて、オン抵 抗を半分以下まで下げることに成功し た。しかし、SiCの理論値に比べると オン抵抗が依然として高く、また耐圧 に関してもドリフト層の理想耐圧より も低く改善の余地があった。

#### IE-MOSFETの開発

今回、さらなる特性の向上を目 指して開発したのがIE-MOSFET (Implantation & Epitaxial MOSFET) である。図2にその断面構造を示す。 IE-MOSFETでは、pウェルの底部を 選択的な高濃度のアクセプタイオン注 入で、表面部をエピタキシャル成長膜 で構成したことにより、DE-MOSFET と同様にpウェル表面を平坦化でき チャネル抵抗の劣化を防止することが

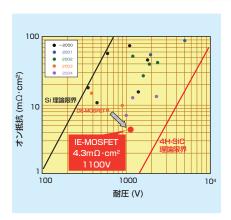

図3 開発した IE-MOSFET と、これまでに報 告された SiC MOSFET の耐電圧とオン抵抗の 関係

できた。さらに、pウェル間のn型領域 の形状が単純化されたため、その領域 の抵抗が低減され、耐圧も向上させる ことができた。試作素子で測定したオ ン抵抗は4.3m Ω·cm<sup>2</sup>で耐圧は1100Vで あり、DE-MOSFETと比較するとオン 抵抗は半分、耐圧は2倍近くまで性能 を向上することができた。これは、同 程度の耐圧をもつSi-IGBTに比べて約 1/5のオン抵抗である。また、Si-IGBT はバイポーラデバイスなのでスイッ チング損失が大きいのに対し、IE-MOSFETはユニポーラデバイスなの で、スイッチング損失も大幅に削減で きたことになり、パワー半導体デバイ スの飛躍的な高効率化が達成されたこ とになる。

今後は、オン抵抗の理論的限界値1 ~3mΩ·cm<sup>2</sup>を目指し、また素子面積 の拡大による大電流化を目指してお り、適用分野のいっそうの拡大を図る。

#### 関連情報:

- 日経産業新聞、日刊工業新聞:2005年3月4日.

- 第52回応用物理学関係連合講演会講演予稿集30p-YK-5.

- 産総研技術開発カタログ No.310.

- 特願 2002-304596「炭化ケイ素半導体装置及びその製造方法」PCT 出願 PCT/ JP03/12727.

- 特願 2003-345551 「炭化ケイ素半導体装置」PCT 出願 PCT/JP04/14476.